pp. 120, 6-3-2012

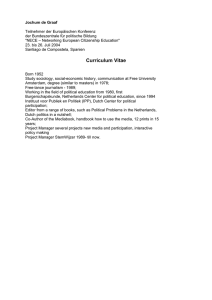

advertisement