BUCK-BOOST DC-DC CONVERTER with INPUT PROTECTION

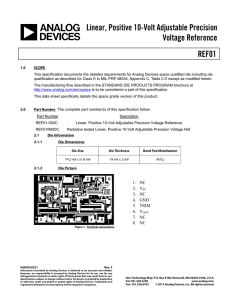

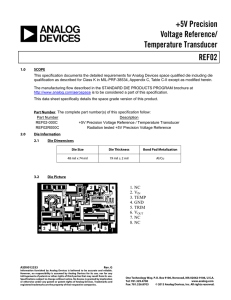

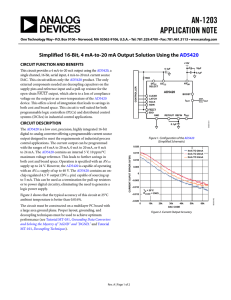

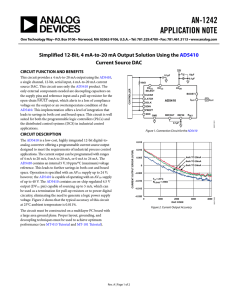

advertisement