Design and Control of a Buck-Boost DC-DC Power

advertisement

Design and Control of a Buck-Boost

DC-DC Power Converter

Robin Vujanic

Semester Thesis

July 2008

Supervision:

Dr. S. Mariethoz

Prof. M. Morari

Contents

1

2

3

Introduction

1.1 Motivation and Objectives

1.2 Converter Topology . . . .

1.3 Synchronous Rectification

1.4 Degrees of Freedom . . . .

.

.

.

.

1

1

3

5

6

.

.

.

.

.

.

.

.

.

.

.

11

11

13

16

17

18

21

22

23

24

27

30

Power Losses

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Losses Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 Modeling Power Losses . . . . . . . . . . . . . . . . . . . . . . . . . .

33

33

33

35

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

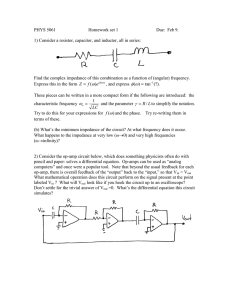

Models of the Circuit

2.1 What is considered and what is not considered . .

2.2 Simulations in PLECS . . . . . . . . . . . . . . . . .

2.3 Basic Analytical Models: Full-Buck and Full-Boost

2.3.1 Buck Model . . . . . . . . . . . . . . . . . .

2.3.2 Boost Model . . . . . . . . . . . . . . . . . .

2.4 Buck-Boost Model . . . . . . . . . . . . . . . . . . .

2.4.1 Estimation Equations . . . . . . . . . . . . .

2.4.2 Equations for the four States . . . . . . . .

2.4.3 Equations for the State-Times . . . . . . . .

2.4.4 The Averaged Model . . . . . . . . . . . . .

2.4.5 The Hybrid Model . . . . . . . . . . . . . .

iii

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Contents

4

5

Controller Design

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Why MPC . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Basic Control Strategies . . . . . . . . . . . . . . . . . . .

4.3.1 Buck, the Simplest Mode . . . . . . . . . . . . .

4.3.2 Boost Mode and the Gain Scheduling Technique

4.4 Buck-Boost Operation . . . . . . . . . . . . . . . . . . .

4.4.1 The Feedforward . . . . . . . . . . . . . . . . . .

4.4.2 The Feedback . . . . . . . . . . . . . . . . . . . .

4.4.3 Results . . . . . . . . . . . . . . . . . . . . . . . .

Conclusion

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

41

41

42

43

43

44

46

47

51

52

59

Bibliography

61

iv

Chapter 1

Introduction

In Zweifelsfaellen entscheide man sich fuer das Richtige.

Karl Kraus

Abstract

A study on the properties and control of a promising circuit topology for a DC-DC buckboost power converter is presented. The circuit contains four transistors operated synchronously in couples. We propose a set of mathematical models to describe this circuit,

and an approach to determine the behavior of the losses occurring inside of it. These are

then combined in order to achieve a control scheme that drives the circuit while minimizing said losses. The control strategy proposed here is based on a combined feedback

(MPC) and feedforward action. Control performance parameters such as disturbances

rejection capability have been investigated as well.

1.1

T

Motivation and Objectives

he present work deals with the design and control implementation of a BuckBoost DC-DC power converter.

DC-DC power converters are employed in order to transform an unregulated DC

voltage input (i.e. a voltage that possibly contains disturbances) in a regulated output voltage. For example, a DC-DC power converter can transform an unregulated

(i.e. distorted) 9V input voltage in a regulated (i.e. ”clean”) voltage of 12V at the output. Some DC-DC power converters have a fixed output reference and ensure that

such voltage is always delivered, no matter what the input is; some others can have

a variable output reference, which can be therefore set depending on the current

need of the device the power converter is used in. The converter discussed in this

work belongs to this second category. In particular, the converter is able to deliver

output voltages both higher as well as lower than (or even equal to) the input voltage; this is why it is referred to as a ”buck-boost” (or ”step-up/step-down”) power

1

CHAPTER 1. INTRODUCTION

unregulated

v in

DC

DC

regulated

vout

Figure 1.1: Abstract functionality of a DC-DC Power Converter: an unregulated input voltage

is transformed into a regulated (i.e. ”clean”) output voltage; The output reference voltage, in

the case of a buck-boost converter, can be set to be either smaller, larger or equal the input

voltage.

converter. A schematic depicting the abstract functionality of a DC-DC power converter can be seen in Figure 1.1.

Such power converters are needed in a vast number of electrical devices, which

on one side is a motivation for this project, and on the other side also explains why

much research is still conducted on this topic. Very high efficiencies have been

achieved by converters currently on the market, yet the main goal of this project is to

push the everlasting quest for still-higher-efficiencies a step further, by exploiting a

novel converter topology and modern control techniques together with appropriate

design choices.

Recent studies on this topic (Frehner 2007) were able to establish some rudimental model of the circuit (the plant) and then applied standard control techniques

(PID and LQR based control schemes). These studies resulted in poor overall performance since:

• The topology was not exploited to its fullest; it was studied and controlled

only either in its full-buck mode or in its full-boost mode (see Chapter 2 for

what is meant with ”full-buck”, ”full-boost” modes), thereby simplifying the

analysis but causing unsatisfactory results as well.

• The implementation of these standard control techniques presented challenges,

mainly because of two reasons:

– first, with PID and LQR controls it is difficult to implement state and inputs constraints (which arise in a natural way when dealing with the control of this plant); an approach via saturators was attempted, but still the

controller performance was unsatisfactory, especially in the boost mode;

– second, especially with the PID approach the control of a multiple-inputs

plant becomes considerably more challenging compared to a single-input

plant; since the plant was considered always either in its full-boost or in

it full-buck mode, this problem has not actually been faced

2

1.2. CONVERTER TOPOLOGY

input stage

“buck”-leg

“boost”-leg

T1

output stage

T3

C

RL

L

Vin

T2

+

Vout

T4

RC

-

Figure 1.2: Schematic of the circuit topology used to achieve DC-DC power conversion; the

different stages are depicted, and notice the load, which is simulated by a current source for

the moment. Later, it will be replaced by a Load resistance for calculations.

• The controllers did not account for the losses inside the circuit, nor a model

for these losses was established.

The present work shows the advances made with respect to these limitations.

1.2

Converter Topology

onsider Figure 1.2, which depicts the circuit topology employed for this project.

It can be split into two separated voltage conversion stages, the ”buck”-leg and

the ”boost”-leg; the first stage (the ”buck”-leg) consists of switches T1 and T2, while

the second stage (the ”boost”-leg) contains switches T3 and T4. We divide the circuit

in these two legs because it turns out that for proper functionality of the circuit

(i.e. in order to avoid a voltage source to be short-circuited - a condition referred

to as ”shoot-through”) each of these two pairs of switches (i.e. for example T1 and

T2) need to work in a complementary manner, and is therefore to be regarded as a

”couple” of switches. Switch T3 and T4 are the other ”couple of transistors” and

these two couples constitute the two circuit legs1 .

For T1 and T2 to work in a complementary manner means that when switch T1

is conducting current (it is on), switch T2 must be off, and vice-versa.

C

1 The

transistors used in this work for switching are MOSFETs.

3

CHAPTER 1. INTRODUCTION

d1

a)

1-d1

dead-time

b)

d2

phase

dead-time

dead-time

Ts

dead-time

Figure 1.3: Typical gate signals obtained for a certain choice of (d1 , d2 , φ); (a) depicts the

signals sent to the first couple of switches (T1 and T2) while (b) shows the signals sent to T3

and T4 (also notice the phase there).

On an important side note, in order to safely avoid the occurrence of both switches

being on (which would lead to shoot-through), short periods of time between the

switchings are introduced, during which both transistors are turned off; these are

so-called dead times2 . This way of operating switches for current rectification is

referred to as synchronous rectification and is briefly discussed in Section 1.3.

Getting back to the discussion on the active times of the switches, the following

naming convention has been used (see Figure 1.3): the time during which T1 is on

(and therefore T2 is off) is denoted as d1 . Since all of the switches are operated in a

cyclic manner (as it is usual in power converter designs), d1 is actually the portion of

time over a cycle during which T1 is on. To make an example, d1 = 0.2 means that

T1 is on 20% of the time of an entire cycle, and is usually referred to as the dutycycle of T1. Therefore, if negelecting small dead-times, 1 − d1 is the time portion

during which T2 is on (i.e. the ”duty-cycle” of T2). The same principle applies for

the second leg, where the portion of time during which T3 is on is denoted as d2

(and therefore 1 − d2 is the time during which T4 is on).

Further, notice that the two duty cycles d1 and d2 can be shifted one relative to

2 During these times, if necessary, conduction is ensured by the body-diodes found in parallel with the

transistors, which are actually a ”parasitic” result of the transistor’s fabrication.

4

1.3. SYNCHRONOUS RECTIFICATION

the other by adding a phase between them, which is denoted with φ 3 . These duty

cycles (d1 and d2 ) and the phase are important variables affecting the behavior of the

circuit because they are in fact the variables that are going to be controlled in order

to achieve the desired output voltage signal. Figure 1.3 shows the typical look of the

gate signals corresponding to certain choices of d1 , d2 and phase and illustrates the

concept of the dead time.

Note: especially when considering the circuit in its ”pure” boost version, this

choice for d2 is *not* consistent with the literature where d2 would be the time during which T3 is off. This controvert convention was adopted at the beginning of this

study and was kept later on for compatibility with initial results.

For the rest of the circuit, the names used for the components is to be understood

as follows:

• L, C, Rload , RC , RL : these are the components inside the circuit. L and C are the

inductor and the (output) capacitor, Rload is the resistor used to model a load

on the output, RC and RL are the parasitic ESRs (Equivalent Series Resistances)

to L and C.

Note: unfortunately, C is also the de-facto established symbol for a matrix in

the standard matrix form of the state-space description of systems, and this

convention for naming this matrix is also used here (see below). However, the

meaning of each instance of C is clear from the context.

• vin , vout , vC , iL : input and output voltages, voltage across the capacitor, current through the inductor.

Note: in order to avoid confusion, voltages are going to be denoted with the

letter ”v” and inputs (to the plant, see Chapter 4) with the letter ”u”.

• T1, T2, T3, T4: the switching transistors.

1.3

Synchronous Rectification

W

hile earlier DC-DC power converters relied on the use of diodes for current

rectification (which is necessary for the converter’s operation), increased performances have been achieved by adopting synchronous rectification in the design

of the power supply instead. Synchronous rectification means that the functionality

3 For

readability of the code developed for this project, it is to be noted that a unit-less denotation has

been used for the phase. A phase of 0.3 means that the d2 signal is shifted of 30% of a duty cycle with

respect to the d1 signal, i.e. the switch T3 is going to switch in the on mode 30% of a cycle later than

when the switch T1 was turned on.

5

CHAPTER 1. INTRODUCTION

once provided by the diode - i.e. current rectification - is now undertaken by a rectifying transistor, typically a MOSFET. Such rectification improves efficiency, thermal

performance, power densities, manufacturability, reliability as well as having typically faster switching transients, and decreases the overall system cost for power

supplies (Selders 2003). These performance increases are mainly due to the fact that

the on-resistance of MOSFETs, RDS,on , can be reduced either by increasing the size

of the die or by paralleling discrete devices, while the forward voltage-drop across

diodes cannot be lowered under a certain (physically imposed) limit; this motivates

the choice of using synchronous rectifiers in the circuit topology studied for this

project.

1.4

Degrees of Freedom

sing the models that are going to be discussed in detail in Chapter 2, it is possible to obtain the vout /vin ratio provided by the circuit with a given combination

of d1 , d2 and φ.

Because of their definition, the d1 , d2 and φ variables are constrained to lie in the

interval [0,1], i.e.:

U

(d1 , d2 , φ) ∈ [0, 1]3

(1.1)

Two typical surfaces showing how the vout /vin ratio behaves with respect to the

(d1 , d2 , φ) variables at steady state are depicted in Figures 1.5 a) and b).

It is confirmed from this surfaces that the general behavior of the output voltage,

in the ideal case, follows the equation:

vout = vin

d1

d2

(1.2)

Some important aspects emerging from this figure have to be highlighted:

• First, notice how this confirms the choice of naming ”buck” and ”boost” the

two legs composing the converter made previously; in fact, d1 (the duty cycle

corresponding to the ”buck” leg) is a multiplicative factor to vin between zero

and one, while d2 (duty cycle of the ”boost” leg) is a multiplicative factor to

vin between one and .

• Second, this figure also shows that the output voltage varies linearly with

varying d1 while instead, when varying d2 , it varies non-linearly. The nonlinearity of the boost stage will have deep consequences for the development

of the control (it is going to pose a major challenge for the design of a valid

controller); this is going to be discussed more in detail in Chapter 2 and 4.

6

1.4. DEGREES OF FREEDOM

v

/ v = f(d1,d2)

out

in

7

6

vout / vin

5

4

3

2

1

0

1

d1

0.5

0

0.1

0.3

0.2

0.5

0.4

0.6

0.8

0.7

0.9

1

d2

dependence of the output voltage on d1 , d2

vout /vin: 0.4

1

0.9

0.8

d2

0.7

0.6

0.5

0.4

0.3

0.2

0.1

0

0.2

0.4

phase

0.6

0.8

1

0

0.1

0.2

d1

0.3

dependence of the output voltage on the phase φ

Figure 1.4: Dependence of the output voltage from the inputs of the plant, i.e. (d1 , d2 , φ)

7

0.4

CHAPTER 1. INTRODUCTION

0.7

0.

9

9

0.

1

1.2

1.4

1.6

0.3

0.2

1.8

9

0.

0.7

0.4

0.8

0.5

0.5

0.6

0.4

0.1

0.6

0.05

d2

0.8

0.5

1.2

0.7

2

1

1.4

0.6

1.2

1.6

2.4

0.4

1.8

2

3

0.1

0.8

0.

9

0.1

0.2

0.3

0.5

0.2

0.8

0.3

0.8

0.3

0.7

0.6

0.4

1

0.2

0.05

0.9

0.1

vout / v in (d1,d2) iso-lines

1

1.2

0.2

1.4

1.6

1.8

2

0.3

2.4

0.4

0.5

d1

3.4

3

0.6

4

0.7

0.8

3.4

0.9

4

5

6

Figure 1.5: Output-voltage iso-lines resulting from slicing Figure a) with planes perpendicular to the vertical axis. Notice that all the points along each of these curves represents d1 ,d2

combinations that will always deliver the same vout /vin ratio.

• Third, notice from Figure 1.5 b how the vout /vin ratio does not depend on

the phase φ; and while the vout /vin ratio is unaffected by changes in φ, variables describing the circuit state (in particular the inductor’s current iL ) are

indeed going to be affected by changes in the phase, resulting in different performances in terms of losses. This is a very important aspect, and leads to our

first ”degree of freedom”: the phase4 .

• Fourth, ”slicing” this surface along planes perpendicular to the vout /vin (”z”)axis results in the set of curves depicted in Figure 1.5. This is the set of curves

of constant output voltage as a function of d1 and d2 . This is also a result of

fundamental importance because it leads to our second ”degree of freedom”:

each choice of d1 and d2 along one of these curves will always lead to the same

output voltage.

The main objective of this project can now be stated as follows: by exploiting

these two degrees of freedom we will be able to affect the state of the circuit;

thus, many internal states will lead to the same output voltage, and the main task

will be to choose among all these possibilities the one that will lead to the least

possible power losses - i.e. to the most efficient way of driving the circuit.

This has been achieved as follows: first, different models of the circuit have been

4 The wording ”degree of freedom” is used to highlight the fact that φ can be chosen arbitrarily while

leaving the output voltage unaffected.

8

1.4. DEGREES OF FREEDOM

developed for different purposes, see next Chapter. After that, a thorough study of

the losses inside the circuit has been conducted using some of these models; this is

exposed in Chapter 3. Based on the study of the losses, the design of a control that

drives the circuit while accounting for losses has been done, and will be presented

in Chapter 4. Chapter 5 is a conclusive chapter, where possible outlooks will be

discussed and a summary of this project will be given.

9

Chapter 2

Models of the Circuit

Bildung ist das, was uebrig bleibt, wenn der letzte Dollar

weg ist.

Mark Twain

2.1

What is considered and what is not considered

T

he circuit being considered in this work is depicted in Figure 2.1. Notice that for

the development of the models, the output load is simulated with a resistance,

Rload . The meaning of the rest of the symbols has been exposed in Section 1.2.

In order to develop a controller, tools in order to forecast how the behavior of the

plant and the losses are going to be are necessary. In this work, two such tools have

been used:

1. Simulations in PLECS, a Simulink toolbox1 .

1 Part

of the validation of the losses behavior discussed later has also been conducted with PSpice, see

(Walter 2008)

T1

T3

C

L

Vin

T2

RL

+

R load Vout

T4

RC

-

Figure 2.1: Schematic of the circuit topology used to achieve the equations of the analytical

models.

11

CHAPTER 2. MODELS OF THE CIRCUIT

2. Analytical models of the circuit.

Under ”behavior of the circuit” we understand the following: we are interested

in knowing the currents inside the circuit (especially through the inductor) and the

voltages across the components (especially on the capacitor) as a function of the time

and with respect to changes to the input. Therefore this is the information our tools

should return us.

This translates into the following model structure for the plant:

• The states are the current through the inductor iL and the voltage across the

capacitor vC .

• Two of the inputs are the duty cycles that are imposed on the two pairs of

switches (one duty cycle for the input leg, one duty cycle for the output leg),

and a third input is the phase between the two duty cycles. As explained

previously, only one duty cycle is necessary in order to control two switches

because they must work in a complementary manner.

• The output is the output voltage (equal to vC in the ideal case - i.e. no ESR).

u

d1

d2

phase

Converter’s Circuit

(plant)

iL,vC

vout

(states)

Figure 2.2: Block diagram for the plant, depicting the inputs, the states and the output.

What is not going to be considered (at least for the formalization of the analytical

models) are the following non-idealities:

• Dead-times: they are implemented in the PLECS simulations but not in the

analytical models (see Section 2.3-2.4).

• Parasitic components: a number of parasitic and non-ideality-induced components could be added to the scheme, including various inductances and

capacitances, especially if a more detailed small- and large-signal description

for the transistors was to be made (rather than taking its ideal behavior, as has

been done). This is avoided here, these effects are actually present and will

deviate the results of an actual implementation from the simulation’s results.

12

2.2. SIMULATIONS IN PLECS

But the essential behaviors discussed in this work are still going to be present

and are still going to be important aspects for design decisions.

The only parasitic components considered are going to be RL and RC , mainly

due to backwards compatibility with previous works (Frehner 2007).

Reverse recovery and voltage drop of diodes, skin and proximity effects of inductors, transistors’ channel resistances and drain capacitance charge/discharge

mechanisms are some of the processes which are not modeled. Including them

in an analytical model greatly increases complexity (basically each additional

capacitance or inductance adds one more state to the model), and, further,

their presence influences homogenously the total losses rather than increasing

one in particular between the conduction or the switching losses (see Chapter

3). Since we are interested in a comparison between these tzpe of losses rather

than in their total amount, and since the stress for this study has been put on

simplicity and generality, these effects have been neglected.

• Discontinuous conduction mode is not considered.

In the following sub chapters, the two methodologies (PLECS Simulations and

Analytical Models) are described more in detail.

2.2

Simulations in PLECS

T

hese simulations have been used extensively at the beginning in order to gain

an understanding of the general behavior of the circuit without having to dwelve

too much into differential equations. The Simulink schematic used for these purposes is shown in Figure 2.3.

What has been done in this case is the following: first, for

D1 = {d1 ∈ R | 0 ≤ d1 ≤ 1}

D2 = {d2 ∈ R | 0 ≤ d2 ≤ 1}

P HASE = {φ ∈ R | 0 ≤ phase ≤ 1}

The inputs set

U := D1 × D2 × P HASE

has been ”gridded”, resulting in U ∗ ⊂ U . Then, for each knot of the discretized set

U ∗ ⊂ U , the behavior of the circuit has been studied.

The results of a single simulation done with PLECS can be seen in Figure 2.2,

where the predicted inductor current is depicted. As can be seen, this prediction

13

CHAPTER 2. MODELS OF THE CIRCUIT

Figure 2.3: Screenshot of the PLECS circuit used to make simulations.

indeed corresponds closely to the result we would have by applying an analytical

model (discussed later in this Chapter) instead.

In general, PLECS simulations have been useful in order to gain a general understanding of the circuit (for example, how does the vout /vin = f (d1 , d2 ) surface

looks like?) and of the losses. However, for decisional purposes they have been

completely substituted with simulations based on analytical models because of a

number of shortcomings this approach presents:

1. First, simulation times are much longer: this approach can increase calculation

times by hundreds. On one side, this makes evaluation of changes of circuit

behaviour with respect to small changes in components, control strategies etc,

less viable. And on the other hand, this forces the use of a wider grid for

the discretized set U ∗. Larger grid translates into less accurate evaluation of

optimal input trajectories (optimal with respect to losses, see Chapter 3).

2. Second, PLECS simulations have transients at the beginning. They can be

shortened by strategically supplying adequate initial conditions for the inductor’s current and the capacitor’s voltage (see Equations 2.30 - 2.35), but they

can never be completely avoided. Since the behavior of the circuit is considered at steady state, this results in even higher calculation times, because the

simulation time needs to be increased. Further, this makes the calculation of

RMS values of steady state signals less precise because there is no guarantee

that the chunk of signal taken in order to calculate the RMS value is already

completely at steady state, without having to resort to unfeasibly long simula14

2.2. SIMULATIONS IN PLECS

PLECS Simulation

30.24

30.22

iL(A)

30.2

30.18

30.16

30.14

30.12

30.1

2.97

2.971

2.972

2.973

2.974

2.975

2.976

time (s)

2.977

2.978

2.979

2.98

-3

x 10

result with PLECS simulations

Analytical Model Simulation

30.26

30.24

i L(A)

30.22

30.2

30.18

30.16

30.14

30.12

0

0.1

0.2

0.3

0.4

0.5

time (s)

0.6

0.7

0.8

0.9

1

-5

x 10

result with analytical models

Figure 2.4: Comparison between the result for the inductor’s current iL of a PLECS simulation with the prediction of the analytical model.

tion times.

3. Third, in order to develop the control and in general to gain a tool with which

it is actually possible to have a grasp on the plant, it is going to be necessary

to obtain the analytical equations in any case.

Nonetheless, testings of results were sometimes made with PLECS mostly for

validation purposes; especially in order to assess the controller performance later,

the plant’s behavior was simulated with a PLECS circuit.

15

CHAPTER 2. MODELS OF THE CIRCUIT

2.3

Basic Analytical Models: Full-Buck and Full-Boost

T

he standard methodology deployed to obtain a model for such a switched system is to take an average of the differential equations, where the weights of

the average are basically the portions of a single cycle during which these equations

hold2 .

In a first approximation, during these times a switch turned on is considered as

an ideal short, while a switch turned off is considered as an ideal open, making it

easy to determine what the differential equations for each state are. A more detailed

description of this technique is given in the next subchapters; further documentation

can be found on (Mohan et al. n.d.) and (Cuk and Middlebrooks n.d.).

The averaging procedure removes the complications involved in the switching

mechanisms, as those are basically ignored and only the average values of the signals are modeled. On one hand, this is an advantage because it delivers a simpler

model, useful to control slow changes of the signal3 . On the other hand, the information on the exact value of the signals at the switching times is lost, making it an

unusable tool for precise assessments of performance benchmarks such as switching

and conduction losses.

This is the basic reason why the feedback controller for the complete buck-boost

topology, which is based on this averaged model, only takes care of things such as

ensuring stability and disturbances rejection; since it cannot ”understand” how to

control better in terms of switching and conduction losses, this part of the controlling mechanism is lend to another structure. This is going to be discussed further in

Chapter 3 and 4.

In the next Sections, 2.3.1 and 2.3.2, the two separated models for the full-buck

and for the full-boost operation modes are first discussed. After those, a model

which fully discloses all the degrees of freedom the circuit makes available and

which describes the complete buck-boost functionality of the circuit is described.

It is to be noted that the first two models are a special case of the last one (both

in functional and mathematical sense), as it is also going to be shown.

Yet, it is also very important to observe that the complete description brings

along a number of features that are not to be found in the separated topologies; these

features are unique and show that the complete description is not just a patchwork

of the two simpler models, therefore making it a more complex reality which needs

to be considered carefully.

2 Additional

3 With

documentation on DCDC Power converters modeling can be found in (?),(?),(?),(?),(?)

”slow” it is meant slower than the switching frequency

16

2.3. BASIC ANALYTICAL MODELS: FULL-BUCK AND FULL-BOOST

2.3.1

Buck Model

The circuit can be considered equivalent to a synchronous buck converter if the third

switch T3 is always turned on, i.e. if d2 = 1. A preliminary study of the ”buck mode”

is useful to show the general approach which is going to be used for more complex

modes.

It turns out in fact that this version is the most attractive one as a starting point

for a study because the differential equations describing the states of the circuit (iL

and vC ) coming from the averaging method are linear by nature. This makes the

successive development of a control for this mode of the circuit straight-forward.

The procedure is the following: first, consider the case where T1 is on, and T2 is

off; applying Kirchhoff Voltage Law (KVL) and Kirchhoff Current Law (KCL) to the

circuit depicted in Figure 2.1 leads to the following equations for the states:

diL

dvC

+ vC + R C C

dt

dt

dvC

vC

dvC RC

iL = C

+

+C

dt

Rload

dt Rload

vin = iL RL + L

(2.1)

(2.2)

Then, consider the complementary case where T1 is off, and T2 is on; the same

equations hold basically, if vin is taken to be zero. Again, applying KCL and KVL

leads to:

diL

dvC

+ vC + RC C

dt

dt

dvC

vC

dvC RC

iL = C

+

+C

dt

Rload

dt Rload

0 = iL RL + L

(2.3)

(2.4)

The basic idea of the averaging technique is now the following: the set of Equations

2.1-2.2 is valid during the portion of cycle time d1 , while the other set, Equations

2.3-2.4 is valid during 1 − d1 . Multiply each set of Equations with these weights, and

then sum them together; simple algebraic reorganization of that result leads to:

diL

RL

RC Rload

1

RC

vin

=−

+

iL + − +

vC +

d1 (2.5)

dt

L

L (RC + Rload )

L L (RC + Rload )

L

Rload

1

dvC

=

iL −

vC

(2.6)

dt

C (Rload + RC )

C (Rload + RC )

For the output the following equation holds in both switching positions (no actual

averaging is therefore required):

vout = vC + C

17

dvC

RC

dt

(2.7)

CHAPTER 2. MODELS OF THE CIRCUIT

Equation 2.7 can be expanded by substituting

algebraic manipulation we obtain:

vout = vC +

dvC

dt

from Equation 2.6, and after some

iL Rload − vC

RC

Rload + RC

(2.8)

Equations 2.5-2.6 and 2.8 are the averaged model. It is evident that a matrix version

of these equations in the standard linear state-space description can be obtained

without the need of an additional linearization because, as can be observed (and

as explained previously), the equations are linear in the states and in the inputs by

themselves. The standard matrix formulation is:

ẋ = Ax + Bu

(2.9)

y = Cx + Du

with:

i

x= L

vC

(2.10)

u = d1

and:

"

A=

−RC Rload

L(RC +Rload )

Rload

C(Rload +RC )

− RLL +

h

C

− L1 + L(RCR+R

load )

1

− C(Rload

+RC )

RC

C = Rload Rload

+RC

1−

RC

Rload +RC

#

B=

i

vin /L

0

(2.11)

D= 0

The equivalent buck topology which is achieved by setting d2 = 1 lacks of the

degrees of freedom which are given by the full (d1 , d2 , φ) coordinates when they can

be chosen independently in [0, 1]3 . This is why there is no optimization with respect

to losses for this topology: because there is only one possible d1 which is able to

reach a given vout demand.

This is also why, as it can be verified, a simple feedback approach (as opposed

to a combined feedforward and feedback approach, as discussed later) is enough to

control this scheme.

2.3.2

Boost Model

The circuit in Figure 2.1 becomes equivalent to a synchronous boost converter if the

first switch, T1, is always on, i.e. if d1 = 1.

It turns out that this version does not have linear differential equations coming

automatically out of the averaging procedure.

18

2.3. BASIC ANALYTICAL MODELS: FULL-BUCK AND FULL-BOOST

This is one of the most important difficulties encountered while developing a

controller for this mode of the circuit and for the whole buck-boost topology: the

set of differential equations governing them is a set of non-linear equations (nonlinear both in the states and in the inputs). It is therefore mandatory to make

some sort of linearization at some point (being it a single linearization or multiple linearizations arising in a PWA approach) in order to apply standard control

techniques. Control of a non-linearized plant should not be undertaken in a first

approach for the control strategy.

Thus, it is clear that more care is needed to gain the model this time compared

to the buck version, while the procedure is basically the same: first determine the

set of differential equations valid in each of the two circuit states emerging from the

two switching positions of T3 and T4 (step 1). Then multiply them by the portion of

time in which they are active, and then sum them together (step 2). This is the set

of non-linear differential equations described in the previous paragraph. This set of

equations is then linearized around some operating point, and only then a standard

matrix formulation of the state-space model can be formulated (step 3).

It is to be noted that formulating the set of non-linear equations in terms of some

matrices prior to linearization is possible to a certain extent, but can be confusing

and is therefore avoided here. Also note that the equations are first merged and

only after that they are linearized.

(step 1) The equations are again gained with a combination of KVL and KCL,

with a procedure basically equal to the previous case; after algebraic manipulations,

we achieve the equations valid while the switch T3 is on (and T4 is off)

diL

1

=

dt

L

Rload iL − vC

vin − iL RL + vC + RC

Rload + Rc

1 Rload iL − vC

dvC

=

dt

C Rload + RC

Rload iL − vC

vout = vC + RC

Rload + RC

(2.12)

(2.13)

(2.14)

On the other hand, while T3 is off (and T4 is on), we have:

diL

1

= (vin − iL RL )

dt

L

dvC

vC

=−

dt

C (Rload + RC )

RC

vout = vC + vC

Rload + RC

19

(2.15)

(2.16)

(2.17)

CHAPTER 2. MODELS OF THE CIRCUIT

(step 2) Now we can merge the equations taking their weighted sum. The multiplicative weight for the first set of equations is d2 , while the weight for the second

set is 1 − d2 . Summing them afterward results in the following set of averaged nonlinear differential equations:

diL

1

Rload iL − vC

=

vin − iL RL + d2 vC + d2 RC

(2.18)

dt

L

Rload + RC

1 d2 Rload iL − vC

dvC

=

(2.19)

dt

C Rload + RC

d2 Rload iL − vC

vout = vC + RC

(2.20)

Rload + RC

Notice from this equations the evident non-linearity, which is due to terms such as

”d2 vC ”.

(step 3) The set can now be linearized, and we choose as linearization point the

dummy point x0 = [iL,0 , vC,0 ] and u0 = [d2,0 ]. The result is the following set of

equations:

1

d2,0

RC

RC Rload

diL

=

−RL + d2,0

iL +

1−

vC + ...

dt

L

RC + Rload

L

Rload + RC

(2.21)

1

Rload iL,0 − vC,0

vC,0 + RC

d2

... +

L

Rload + RC

dvC

1

Rload

1

1

=

d2,0

iL +

−

vC + ...

dt

C

Rload + RC

C

Rload + RC

Rload iL,0

1

... +

d2

C Rload + RC

vout = d2,0

RC Rload

RC

iL + 1 −

vC

Rload + RC

Rload + RC

(2.22)

(2.23)

which can clearly be expressed in the standard state-space matrix form, and used

once numerical values for x0 and u0 are chosen. Explicitly, this results in the following matrix description

ẋ = Ax + Bu

(2.24)

y = Cx + Du

with:

x=

iL

vC

u = d2

20

(2.25)

2.4. BUCK-BOOST MODEL

and:

A=

1

L

d2,0

Rload

RC

−RL + d2,0 RRCC+R

1

−

L

R

+R

load

load

C

Rload

1

1

1

d

−

2,0

C

Rload +RC

C

Rload +RC

Rload iL,0 −vC,0

1

vC,0 + RC Rload +RC

L

B=

Rload iL,0

1

C

(2.26)

(2.27)

Rload +RC

h

i

RC

C Rload

1 − Rload

C = d2,0 RRload

+RC

+RC

h

i

C Rload

D = RRload

i

L,0

+RC

(2.28)

(2.29)

This concludes the introductory discussion on the basic full-boost and full-buck

topologies. In the next Section, the discussion is extended to the complete buckboost functionality and the results are going to be shown.

2.4

Buck-Boost Model

aking the discussion a step further, in this section the development of the combined buck-boost topology is presented. As noted previously, when exploiting

the degrees of freedom of this circuit, a handful of new features arises which are not

to be encountered in the previous special cases. Among others, these can be cited:

T

1. Operating the switches as discussed in Section 1.2 gives rise to four feasible

combinations of switching states 2.5 compared to the previous cases where we

only had two intermitting states. This is the reason why this converter is called

a four-state converter.

2. This also directly relates to the fact that the equations for the state-times (the

time portions, during which one of the four state is active each cycle) are more

complex than before; the solution to this problem is given below, see Section

2.4.3.

3. Previously the choice of the duty cycles d1 (for the buck) and d2 (for the boost)

was constrained by the vout output demand. For instance, in the buck mode, if

the demand was vout = 10V with a given vin = 20V , then there was only one

feasible d1 which could achieve that demand (which is d1 = 0.5 in the ideal

case). This is no longer the case, as it is going to be shown, since an infinity of

combinations of (d1 , d2 , φ) exists that achieves a given vout demand.

21

CHAPTER 2. MODELS OF THE CIRCUIT

4. This additional degrees of freedom also enable us to have a better control on

the currents flowing inside the circuit while keeping the same vout . Exploiting

this property is going to allow us to optimize the switching in order to achieve

better performance in terms of losses.

5. Another important aspect concerning the modeling is that two different modeling approaches are actually going to be taken this time. The first one is the

usual averaging-technique, which will deliver the model used for the feedback

MPC. The second one is an engineered simulation of the hybrid behavior of

the switched system, described further in Section 2.4.5; the true waveform of

iL (and not only its average) will be reproduced with this model, which will

be used as a reliable tool for assessing the losses behaviour.

In the following, the presentation of the different models needed for the evaluation

of the buck-boost functionality is organized as follows: in Section 2.4.1, the Equations valid for the mean values of the plant’s variables at steady state is briefly described; in Section 2.4.2, the Equations governing the circuit behavior in each of the

four possible states are presented, and in the subsequent Section 2.4.3, the algorithm

used in order to determine the state times (the weights of the average) is exposed.

The results of these two Sections will be combined in Section 2.4.4 in order to achieve

the average model, and in Section 2.4.5 in order to obtain the hybrid model.

2.4.1

Estimation Equations

This is a set of equations useful for determining the steady-state mean values of

different signals. They do not account for the presence of the parasitic ESRs which

are otherwise included throughout the rest of the report, but are nonetheless useful.

Output values:

d1

d2

vin d1 /d2

=

Rload

vout = vin

iout

(2.30)

(2.31)

Capacitance:

vC = vout

(2.32)

iC = 0

(2.33)

22

2.4. BUCK-BOOST MODEL

Inductance:

(2.34)

vL = 0

iL =

2.4.2

vin d1 /d2

Rload d2

(2.35)

Equations for the four States

For each of the four states depicted in Figure 2.5 the corresponding sets of governing

differential equations is given here below. These differential equations are obtained,

as usual, by applying KVL and KCL laws and then by algebraically reorganizing

them, similar to what has been done in Sections 2.3.1 and 2.3.2. The denotations are

to be understood as follows: State ”13” means that switches T1 and T3 are currently

on; State ”23” means T2 and T3 are on, and so on.

a)

c)

C

Vin

L

RL

C

L

R load

RL

RC

R load

RC

b)

d)

C

Vin

L

RL

C

R load

L

RL

RC

R load

RC

Figure 2.5: Pictures of the circuit in its four possible states.

23

CHAPTER 2. MODELS OF THE CIRCUIT

State ”13” (see Figure 2.5.a)

diL

1

RC

RC

=

vin − iL RL +

− vC 1 −

dt

L

1 + RC /Rload

Rload + RC

dvC

vC

1

= iL −

dt

Rload

C (1 + RC /Rload )

iL Rload − vC

vout = vC + RC

(Rload + RC )

(2.36)

(2.37)

(2.38)

State ”14” (see Figure 2.5.b)

1

diL

= [vin − RL iL ]

dt

L

dvC

vC

=−

dt

C (RC + Rload )

vC

vout = vC − RC

(Rload + RC )

State ”23”4 (see Figure 2.5.c)

diL

1

RC

RC

=

−iL RL +

− vC 1 −

dt

L

1 + RC /Rload

Rload + RC

vC

1

dvC

= iL −

dt

Rload

C (1 + RC /Rload )

iL Rload − vC

vout = vC + RC

(Rload + RC )

(2.39)

(2.40)

(2.41)

(2.42)

(2.43)

(2.44)

State ”24”5 (see Figure 2.5.d)

diL

−RL

=

iL

dt

L

vC

dvC

=−

dt

C (RC + Rload )

vC

vout = vC − RC

(Rload + RC )

2.4.3

(2.45)

(2.46)

(2.47)

Equations for the State-Times

The following equations will model the time the circuit spends in each of the four

states for a given (d1 , d2 , φ) coordinate. Notice that these equations also respect the

4 Notice

5 Again,

that is basically the same set of equations as the previous one, if vin is taken to be zero.

this is the same set of equations of State 14 if vin is set to zero.

24

2.4. BUCK-BOOST MODEL

(relative) order in which these states appear6 .

Notice how a partitioning in cases was necessary to model the state-times correctly: a case-choice is to be made each time in order to fetch the valid set of equations (in figure 2.6 the correspondence between case and switching condition is depicted).

a)

d)

b)

e)

c)

f)

Figure 2.6: Diagrams of the different possible gate signals.

The symbols are understood as follows: t13 is the time spent while T1 and T3 are

on (therefore T2 and T4 are off). Similarly, t23 means T2 and T3 are on, and so on;

interpret the following as a MATLAB-code snippet (i.e. nested ”if” routines where

necessary).

Case 1 (Figure 2.6.a):

if (phase<=d1) && (mod(phase+d2,1)<= d1)

if ((phase+d2 - mod(phase+d2,1)) == 0)

t14 = phase;

t13 = d2;

6 While the relative sequence of states is not a relevant information for the averaged model, it is in fact

fundamental for properly simulating the switching behavior which is done in Section 2.4.5 in order to

gain the hybrid model

25

CHAPTER 2. MODELS OF THE CIRCUIT

t14 = d1 - (d2+phase);

t24 = 1-d1;

end

Case 2 (Figure 2.6.b):

if ((phase+d2 - mod(phase+d2,1)) ˜= 0)

t14 = phase - (1-d2);

t13 = 1-d2;

t23 = d1-phase;

t24 = 1-d1;

end

end

Case 3 (Figure 2.6.c):

if (phase>=d1) && (mod(phase+d2,1)>= d1)

if ((phase+d2 - mod(phase+d2,1)) == 0)

t14 = d1;

t24 = phase-d1;

t23 = d2;

t24 = 1-phase-d2;

end

Case 4 (Figure 2.6.d):

if ((phase+d2 - mod(phase+d2,1)) ˜= 0)

t13 = d1;

t14 = phase-(1-d2)-d1;

t24 = 1-d2;

t23 = 1-phase;

end

end

Case 5 (Figure 2.6.e):

if (phase<=d1) && (mod(phase+d2,1)>= d1)

t13 = phase;

t14 = d1-phase;

t13 = phase+d2-d1;

t23 = 1-phase-d2;

end

26

2.4. BUCK-BOOST MODEL

Case 6 (Figure 2.6.f):

if (phase>=d1) && (mod(phase+d2,1)<= d1)

t13 = phase-(1-d2);

t23 = d1-(phase-(1-d2));

t24 = phase-d1;

t23 = 1-phase;

end

Based on the results of these two first Subsections, it is now possible to estabilish

the equations for the averaged and hybrid models.

2.4.4

The Averaged Model

Multiplying the state-equations (2.38)-(2.47) with the corresponding state-times already provides the set of non-linear differential equations used to get the averaged

model. Explicitly, this results in:

diL

1

RC

RC

=

vin − iL RL +

− vC 1 −

t13 + ...

dt

L

1 + RC /Rload

Rload + RC

1

... + [vin − RL iL ] t14 + ...

L

1

RC

RC

... +

−iL RL +

− vC 1 −

t23 + ...

L

1 + RC /Rload

Rload + RC

−RL

iL t24

... +

L

(2.48)

vC

1

t13 + ...

Rload

C (1 + RC /Rload )

−vC

t14 + ...

... +

C (RC + Rload )

vC

1

... + iL −

t23 + ...

Rload

C (1 + RC /Rload )

−vC

... +

t24

C (RC + Rload )

dvC

=

dt

iL −

iL Rload − vC

(t13 + t23 ) + ...

vout = vC + RC

(Rload + RC )

vC

... + vC − RC

(t14 + t24 )

(Rload + RC )

27

(2.49)

(2.50)

CHAPTER 2. MODELS OF THE CIRCUIT

Equations 2.48-2.49 can be rewritten in a more compact form as follows:

i˙L

= F (iL , vC , vin , d1 , d2 , φ) =

v˙C

vin

vin

i

i

t13 (d1 , d2 , φ) + F14 L +

t14 (d1 , d2 , φ) + ...

= F13 L +

vC

vC

L

L

iL

i

... + F23

t23 (d1 , d2 , φ) + F24 L t24 (d1 , d2 , φ)

vC

vC

(2.51)

with:

F13 = F23 =

−1

L

RL +

RC

1+RC /Rload

1

C(1+RC /Rload )

−1

L

−1

Rload

1−

RC

Rload +RC

1

(2.52)

C(1+RC /Rload )

−RL F14 = F24 =

L

0

(2.53)

Since this model is non-linear, like the boost version discussed in Section 2.3.2,

a linearization around some operating point, denoted here again x0 = (iL,0 , vC,0 )

and u0 = (d1,0 , d2,0 , φ0 ), needs to be made. Such linearization can be written in the

standard state-space matrix form yielding, for A:

A=

∂F (iL , vC , vin , d1 , d2 , φ) =

∂x(iL , vC )

x0 ,u0

= F13 t13 (d1,0 , d2,0 , φ0 ) + F14 t14 (d1,0 , d2,0 , φ0 ) + ...

(2.54)

... + F23 t23 (d1,0 , d2,0 , φ0 ) + F24 t24 (d1,0 , d2,0 , φ0 ) ∈ R2×2

The values t13 (d1,0 , d2,0 , φ0 ), t14 (d1,0 , d2,0 , φ0 ), ..., which are still left undetermined

in this last result have to be determined with the right case-choice from the ”if”structure presented in the previous Section.

28

2.4. BUCK-BOOST MODEL

For B, we do partial derivation with respect to the inputs, yielding:

∂F (iL , vC , vin , d1 , d2 , φ) =

B=

∂u(d1 , d2 , φ)

x0 ,u0

vin ∂t13 (d1 , d2 , φ) iL

=

F13

+ ...

+

vC

L

∂u

x0 ,u0

vin ∂t14 (d1 , d2 , φ) iL

... +

F14

+

+ ...

vC

L

∂u

x0 ,u0

∂t23 (d1 , d2 , φ) i

... + F23 L

+ ...

vC

∂u

x0 ,u0

iL ∂t24 (d1 , d2 , φ) =

... + F24

vC

∂u

x0 ,u0

#

"

iL,0

0

0

C(1+RC /Rload )

∈ R2×3

= vin

−RC iL,0

−Rload vC,0

0

L

L(Rload +RC ) + L(1+RC /Rload )

(2.55)

Notice that the last equality in Equation (2.55) is not trivial. First, only after

computation of the partial derivative of the state-times with respect to the inputs,

i.e.:

∂t14 (d1 , d2 , φ) ∂t23 (d1 , d2 , φ) ∂t24 (d1 , d2 , φ) ∂t13 (d1 , d2 , φ) ,

,

,

∂u

∂u

∂u

∂u

x0 ,u0

x0 ,u0

x0 ,u0

x0 ,u0

it turns out that for each ”if”-case the B matrix looks always the same, while potentially six different matrices could have arisen for each of the six cases. Second, notice

how the last column of B contains only zeros; this confirms the statement made in

Section 1.4, where it was asserted that the mean of the output voltage does not depend on φ. Based on this model, it actually turns out that none of the mean values

(i.e. also the internal states’ mean values) changes if the phase is varied7 .

For the C and D matrices, the derivation of the output Equation with respect to

the states and the inputs has to be made, leading to8 :

C=

h

Rload RC

Rload +RC (t13

+ t23 )

1−

RC

Rload +RC

i

∈ R1×2

(2.56)

x0 ,u0

Rload RC ∂(t13 + t23 ) ∈ R1×3

D = iL,0

Rload + RC

∂u

x0 ,u0

(2.57)

7 The fact that the output mean value is not influenced is in fact a consequence of this fact, and therefore

only indirectly a consequence of the fact that the last column of B only contains zeros.

8 In the MATLAB routines attached to this document, approximations for these matrices have usually

been made. In particular, C has been approximated to be C ≈ [0 1] and D ≈ [0 0 0]

29

CHAPTER 2. MODELS OF THE CIRCUIT

This ends the discussion about the models needed for the feedback part of the

control scheme, discussed in Section 4.4.2.

2.4.5

The Hybrid Model

Hybrid model might sound exotic, but it is developed here in the (probably) most

intuitive way without resorting to tools such as HYSDEL9 . This is done by using the

information on the state times and their sequence from the previous Sections 2.4.22.4.3: basically, the sequence in which the states appears is known, and their active

time is known as well. The voltage across the inductor is easily estimated with the

following equations:

State ”13”:

vout

vL = vin − vC + iL −

− iL RL

Rload

(2.58)

vout

− iL RL

vL = − vC + i L −

Rload

(2.59)

vL = vin − iL RL

(2.60)

vL = −iL RL

(2.61)

vL

dt

L

(2.62)

State ”23”:

State ”14”:

State ”24”:

Then, integrating

diL =

over the period of time during which each state is active (thereby approximating

with the assumption that vL be constant) readily gives the desired waveform with

the small addition that the offset still needs to be adjusted. This can be done either

by using the approximative equation for the mean iL at steady state (2.35), which is

done here (because of its simplicity) with good results, or by enforcing the constraint

that the current at the beginning of each period must be equal the current at the end

of it.

9 http://control.ee.ethz.ch/˜

hybrid/hysdel/

30

2.4. BUCK-BOOST MODEL

Figure 2.2 shows for one given (d1 , d2 , φ) coordinate that the two approaches

agree up to 0.1%; it can be verified that the prediction for iL obtained this way is

accurate also for other choices of u.

As stated previously, the results from this hybrid model are used afterward to

make assessment regarding the behavior of switching and conduction losses; this is

going to be the main topic of Chapter 3.

31

Chapter 3

Power Losses

Ploetzliche Regenfaelle koennen zum Betreten einer

Buchhandlung zwingen.

Loriot

3.1

Introduction

ur objective is to drive the circuit while minimizing the losses occurring inside

of it. In order to do this, models for the behavior of these losses are necessary;

i.e. the aim of this Chapter is to present how this mapping, Ploss = f (d1 , d2 , φ), can

obtained.

O

3.2

Losses Description

T

here are two different types of losses occurring inside the circuit: Conduction

Losses (PConduction ) and Switching Losses (PSwitching ); in the following, these

two types of losses are going to be shortly described.

Conduction Losses

These are losses of resistive type, and, for the particular circuit that is investigated, they are produced because of current flowing through the following resistive

media:

• MOSFETs’ channel resistance RDS,on

• MOSFETs’ body diode

• Capacitance’s ESR (Equivalent Series Resistance)

• Inductance’s ESR

33

CHAPTER 3. POWER LOSSES

Being these losses of resistive type, they can be modeled to be proportional to the

square of the RMS value of the current flowing inside the circuit, i.e.:

PConduction ∼ i2L,rms

(3.1)

Note: this estimation is already an approximation, since higher losses will usually cause a rise of temperature, which is going to affect the values of the parasitive

resistances, which in turn is going to affect the losses.

Switching Losses

The mechanisms involved in the production of switching losses are more complicated than the previous ones. They are produced by the action of turning on

and off active devices on the power’s path, therefore they only happen at discrete

times ”tj ” (where j indexes all the times at which switchings of a given MOSFET

occur) and for a short period; they occur under the following circumstances (Mohan

et al. n.d.):

• switching of power currents (”turning on and off currents in the presence of

voltage”)

• parasitic drain capacitance charge and discharge

• gate drive losses

• body diode reverse recovery

In the part of investigation conducted on switching losses, only the first contribution

(i.e. switching losses due to switching of power currents) has been considered. An

estimate of their magnitude can be obtained as follows:

• If the MOSFET is turning on, and the current was not flowing through its

body diode, then the switching loss can be estimated as being proportional to

the product of the current that will start to flow through the MOSFET and the

voltage across the MOSFET prior to switching, i.e.:

+

PSwitching,j ∼ v(t−

j )iL (tj )

(3.2)

• If the MOSFET is turning off, on the contrary, and the current will not be able

to flow through its body diode, then the switching loss can be estimated as

being proportional to the product of the current that was flowing through it

and the voltage that will be applied to the MOSFET after, i.e.:

−

PSwitching,j ∼ v(t+

j )iL (tj )

34

(3.3)

3.3. MODELING POWER LOSSES

because of this, if the current iL is positive (flowing from the input stage to the output stage), then switching losses will occur only at switches T1 and T4. Conversely,

if iL is negative, then switching losses will occur in switches T2 and T3.

On a side note, it can be noted that since these losses occur at switching times,

the more switchings there are, the higher the switching losses will be (if the same

MOSFETs are used), i.e. switching losses grow proportionally to the switching frequency. Therefore, on one hand, switching frequency should not be chosen to be

arbitrarily high. But on the other hand, switching frequency should not be chosen

too low either because that would cause higher ripples on the output voltage.

Also, it is of critical importance to note at this point that during the simulations

described further in this chapter, the magnitude of the losses is estimated using these

very equations. But since these equations only give results that are proportional to the

exact values, their shape will describe the general behavior of the losses properly,

but their magnitude will need to be corrected by an adequate multiplicative correction constant. This constant will strongly depend on the choice of components that

is going to be made. This aspect is discussed more in detail in the next Section.

3.3

Modeling Power Losses

tis possible to achieve a characterization of the switching and conduction losses

using the equations of above, by estimating their value for each choice of (d1 , d2 , φ).

This is accomplished by using the model (2.58)-(2.61) discussed in Section 2.4.5,

which reproduces the hybrid behavior of the plant; explicitly, for each combination

of (d1 , d2 , φ), the shape of iL is calculated. This enables the calculation of the conduction losses. Then, the equations for the state-times exposed in Section 2.4.3 are

used to fetch the sequence of switchings occurring during each cycle, and the times

at which each switching occurs. This information is sufficient in order to calculate

the switching losses.

Notice that such a detailed description (in contrast to a simplified version given

by the averaged models) is needed in order to assess losses, first because the RMS

value of the current is needed (which can only be calculated if the correct shape of

the iL current is known), and second because the losses also depend on the sequence

of switchings which is adopted, which therefore needs to be known (what switch is

switched when, so that the current can be multiplied with the correct voltage).

The losses have been investigated for many vout /vin ratios, i.e. the set of (d1 , d2 , φ)

combinations giving the same output voltage has been gridded and then simulated

for each of the resulting knots. Typical results for low output references and for high

output references are shown in Figure 3.3 and 3.3.

I

35

CHAPTER 3. POWER LOSSES

Figure 3.1: Switching and Conduction Losses for a low vout /vin demand. Values are not

scaled properly, but do give an idea of the percentages. Notice that the switching losses have

a pretty marked behavior in this case; this is probably due to resonant occurrences inside the

circuit which should be investigated further. This image has been selected mainly because it

shows well how conduction and switching loss minima-locations do not necessarily coincide.

A fundamental result of this study is shown in Figure 3.3: it is evident from the

two pictures that the positions at which conduction losses and switching losses

are minimal do not necessarily coincide. The same result can be verified in Figure

36

3.3. MODELING POWER LOSSES

Figure 3.2: Switching and Conduction Losses for a high vout /vin demand. Values are not

scaled properly, but do give an idea of the percentages. The switching losses behavior depicted for this case is more representative of what is usually encountered.

3.3. This poses a challenge in the following sense: if the two minimal positions

would coincide, then the minimum of the sum of the two losses would also be at

that same place; but since they do not, it is important to sum up together the correct

values for conduction and switching losses, in order to achieve the correct position

of the minimum of the total. On one side, this means that sometimes there needs to

37

CHAPTER 3. POWER LOSSES

be an optimized trade-off between these two types of losses. On the other hand, this

also means that the exact values of the two losses will influence the position of the

minimum of the sum. Or stated another way round: we saw that the exact values

of switching and conduction losses still depend on the value of the multiplicative

correction terms that need to be applied; these values in turn depend on the choice

of components, and as a consequence the value and position of the minimum total

loss will depend on the choice of components.

Conduction Losses vs

Swiching Losses

phase = 0.8

phase = 0.2

1.17

1.16

i L (A)

1.15

1.14

1.13

1.12

1.11

1.1

2.96

2.964

2.968

2.972

time (ms)

2.976

2.98

2.964

2.968

2.972

time (ms)

2.976

2.98

Switching Loss (~)

30

25

20

15

10

5

0

2.96

Figure 3.3: Comparison between conduction (upper graph) and switching losses (lower

graph) for two different (d1 , d2 , φ) combinations giving both vout /vin = 0.2 (both have

d1 = 0.14, d2 = 0.7). On the first graph, it is clear that the blue curve, with φ = 0.2 has

overall lower conuction losses, because its RMS value is lower than the red one. On the lower

graph, however, where switching losses are depicted (as losses occurring only at discrete

times) it is clear that the blue inputs combination delivers higher switching losses. Therefore,

it is verified that conduction and switching losses do not necessarily have coinciding minimal

points, since lowering one might cause an increase in the other.

For the successive development of the controller, which will depend on these

38

3.3. MODELING POWER LOSSES

results, a certain choice for the corrective weights has been made, which is in no

way bound to any actual choice of components - as it should. This choice has been

made for prototyping purposes, and appropriate weight still need to be determined

from a proper selection of components.

39

Chapter 4

Controller Design

Short cuts make long delays.

Hobbit Proverb

4.1

Introduction

ased on the research done on the models in Chapter 2 and the Losses in Chapter

3, it is now possible to start developing an efficient control for the plant. As a

reminder, our task is to control the duty cycles of each pair of transistors and their

phase, so as to ensure:

B

• first and most important: reaching of and stabilizing around a given output

voltage demand;

• reaching the target steady state should happen in the desired manner, i.e. the

controller needs to handle transients properly;

• the controller also needs to be able to reject disturbances (usually encountered

on the load and on the input voltage source vin );

• while doing all this, the controller (in the full buck-boost mode) needs to

choose among the infinite possibilities of inputs, that would satisfy the above

conditions, those that will cause the least losses.

Notice that, as explained previously, minimization of losses is only possible if all

the degrees of freedom of the circuit are exploited, i.e. there is no optimization of

control strategy towards minimal losses for the buck or boost modes alone.

The presentation of the development of such a controller is going to be handled

in the next Sections as follows: first the choice of MPC as control approach for the

feedback is motivated; in Section 4.3 the control techniques deployed for the basic

versions of the circuit (full-buck and full-boost) are discussed, based on which the

more complex control for the whole buck-boost functionality is finally going to be

discussed, Section 4.4.

41

CHAPTER 4. CONTROLLER DESIGN

4.2

Why MPC

MPC was chosen based on the following reasons:

• its ability to efficiently deal with constraints

• because standard control techniques such as a PID implementation delivered

unsatisfactory results (Frehner 2007)

• because of its robustness to model uncertainties

• and because it works for multiple inputs plants exactly the same way as it

works for the SISO ones, thereby allowing analogous implementations for the

buck/boost (one input) and buck+boost (three inputs) modes; on the contrary,

traditional implementations using control techniques such as PIDs present

many challenges when applied to multiple inputs plants, especially when it

comes to the assessment of control performances such as stability, robustness

and disturbances rejection.

Also, while MPC was previously only applied to slow-dynamics plants, because the control action needed to be calculated from an optimization problem each

time (on-line control), recent developments made it possible to move the burden of

calculating the control moves off-line, through what is called a multi-parametric

(quadratic in this case) program approach (mpQP), thus allowing to apply MPCs

also to plants with fast dynamics (IfA Website1 ).

Calculating the input move on-line would consist in solving a quadratic program

(QP) each time (if 2-norm cost functions are taken - as it is usually the case), and a

multiparametric approach just means that this optimization problem is parametrized

and solved for a certain set of parameters x (this is the set of all the x’s contained

in a predefined constrained set X), and during runtime the correct input is easily

computed by plugging in the parametrized solution the appropriate current state x.

Multiparameter problems allow to calculate so-called explicit MPCs. An explitic

MPC is therefore nothing more than a look-up table that will return the control move

to be taken given some current state x. Notice that this is the same control move that

would be applied if an on-line MPC strategy would be chosen instead of the explicit

one.

Since the control moves are pre-calculated moving around the whole feasible

U × X set, it is necessary to constrain it in order to make this procedure end in finite

time. This is why this technique can be applied only to constrained problems. For

this particular plant, the inputs, which are basically the duty cycles and the phase,

1 see

(IfA n.d.) http://control.ee.ethz.ch/ hybrid/control.php

42

4.3. BASIC CONTROL STRATEGIES

need to be bounded between 0 and 1. This results in the inputs set U to be delimited

to:

(4.1)

U = u ∈ R3 | u ∈ [0, 1]3

X, on the other hand, is only ”loosely” constrained, i.e. it is taken to be much larger

then the actual values of the states are ever going to be driven at, just to make the

computation feasible. Notice that other restrictions could be made, in particular a

restriction on the inductor current to be non-negative (if discontinuous mode has

to be considered) and other restrictions to ensure soft-start requirements could be

made2 .

4.3

4.3.1

Basic Control Strategies

Buck, the Simplest Mode

s discussed in Chapter 2.3.1, the model obtained with the averaging technique

is linear. There is only one variable being controlled (d1 ) and there is no optimization of controls towards least losses. This is why a simple feedback approach

(as opposed to a combined feedforward and feedback approach, as discussed later)

is enough to control this scheme.

The feedback control is implemented as an explicit MPC. The MPC is to be fed

with a discrete time model which is easily obtained from the continuous model of

Equations (2.24)-(2.29) with the c2d() routine in MATLAB . Thus, starting from these

equations and plugging in testing values for the components reported in Table 4.1,

the following discrete-time model results:

A

xk+1 = Axk + Buk

(4.2)

yk = Cxk + Duk

(4.3)

with:

0.9992 −0.0498

A=

0.03321 0.9925

0.9997

B=

0.01662

C = 0.9998 0.0009998

D = [0];

2 http://control.ee.ethz.ch/˜

hybrid/applications.php#powerElectronics

43

CHAPTER 4. CONTROLLER DESIGN

Full-Buck, Full Boost

Buck-Boost

Sampling Frequency

vin

L

C

Rload

RL

RC

vin

L

C

Rload

RL

RC

TS

20V

2e−5 H

3e−5 F

5Ω

0.001Ω

0.001Ω

20V

2e−4 H

3e−5 F

5Ω

0.001Ω

0.001Ω

100kHz

Table 4.1: Values of the components used to test the behavior of the controller.

A typical start-up response of the controlled output can be seen in Figure 4.1.

The details of this implementation, such as the influence of the weights and of the

prediction horizon, are not discussed further, since this is a special case of the complete buck-boost topology; such discussions are going to be made for the general

case in Section 2.4.

4.3.2

Boost Mode and the Gain Scheduling Technique

nalogous to the Buck operation mode, only one variable is being controlled

(d2 ) and no optimization towards least losses can be done. Therefore also in

this case a simple feedback controlling strategy (i.e. not a combined feedforward +

feedback) is taken. And again, the feedback is based on a MPC approach, and the

discrete-time model is obtained with c2d() like before.

But the boost operation mode presents a challenge which was not encountered

for the buck mode: since the model obtained with the averaging technique is not

linear, the matrices obtained linearizing around x0 and u0 still depend on the numerical values of x0 and u0 , as can be seen from Equations (2.24)-(2.29). This could

indeed be a major problem because basically it means that different steady-state operating points have different dynamics. Notice that this challenge is to be faced in

the full buck-boost operation mode as well.

Fortunately, it turns out that while the plant driven in boost mode is indeed nonlinear, it still behaves ”well” (see below for what is meant with ”well”).

This fact has been exploited both for the boost and the buck-boost mode. The

reasoning behind it is the following: the fact that the model is non-linear is a reality

which cannot be avoided and needs to be accounted for; the most basic approach to

A

44

4.3. BASIC CONTROL STRATEGIES

Full-Buck Output Performance

7

6

vout (V)

5

4

3

2

1

0

0

0.5

1

1.5

2

2.5

3

3.5

4

4.5

5

time (ms)

Figure 4.1: Startup performance of the controller developed for the full-buck operation, with