GaNFET Application note

advertisement

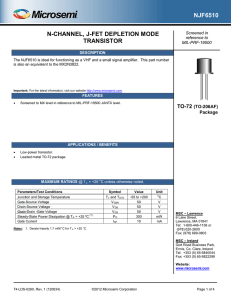

Applying MiGaN,TM GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability Anthony G.P. Marini, President/ Principal, DTM Associates/ Microsemi Corporation Al Ortega, Product Line Manager, Microsemi Corporation Introduction There is a lot of interest in the application of GaN HEMT (High Electron Mobility Transistor) power devices in high reliability and space power supplies, and given their excellent performance characteristics (ultra high-speed switching times, low gate charge and low ON resistance) these devices are certainly the natural technology progression in relation to conventional silicon MOSFET devices. But due to their “newness” in the marketplace, and some general misconceptions regarding their robustness and reliability, general acceptance of these devices in high reliability and space applications has been slow in coming. Microsemi MiGaNTM GaN Transistor product line, a new line of hermetically-packaged, enhancement-mode GaN power switches geared towards the high reliability and space marketplaces. These devices cover a breakdown voltage range from 40 V to 200 V. The on resistance of these devices, including packaging, is in the range of 7 to 25 milliohms. These devices are optimized for isolated DC-DC conversion, POL power processing, and motor drive applications. These devices are housed in the convenient and efficient U4A surface mount package. This application note is intended to show how MiGaNTM power transistors housed in the innovative U4A package can be used in high reliability and high performance DC-DC conversion circuits, and to help change the perception of these game-changing devices. GaN Device Construction and Inherent Characteristics In order to properly apply a GaN device in a particular end-user circuit, some background into the physics and construction of the device is in order. The GaN device enhancement mode process begins with a silicon wafer. A thin layer of Aluminum Nitride (AlN) is grown onto a conventional silicon substrate to provide a seed layer for the subsequent growth of gallium nitride heterostructure. Gallium nitride (GaN) is grown on the AlN. This layer provides a foundation on which to build the enhancement-mode GaN HEMT. A very thin AlGaN layer is then grown on top of the highly resistive GaN. It is this thin layer that creates a strained interface between the GaN and AlGaN crystals layers. This interface, combined with the intrinsic piezoelectric nature of GaN, creates a plain of high conductivity, high velocity electrons known as a two dimensional electron gas (2DEG). The key to the high performance of these devices is that the confinement of the electrons in such a small region “squeezes” them into an electron gas that has much higher mobility than in a semiconductor crystal. This higher mobility means the electrons can travel faster and with less resistance. Silicon devices, on the other hand, require more energy to pull an electron off of its atom in order for it to move to its next atom. In addition to the high conductivity, this majority carrier device’s switching characteristics are excellent because switching is solely limited by how fast the small amount of gate charge necessary for switching can be inserted and removed from the gate. Further processing of a portion of the 2DEG forms a depletion region. This depletion region interrupts the 2DEG and blocks conduction, and becomes the gate. To enhance the FET, a positive voltage is applied to the gate in the same manner as turning on an n-channel, enhancement mode power MOSFET. This action injects electrons under the gate contact and completes the 2DEG, creating a highly conductive, bi-directional path from drain to source. A simplified layer-by-layer representation of the GaN HEMT structure is shown in Figure 1. Several additional layers of metal and dielectric are added to this basic structure in order to route the electrons to the gate, drain, and source input/ output terminals. This structure is repeated many times to form the resultant power device. Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 A simplified layer-by-layer representation of the GaN HEMT structure is shown in Figure 1. Several additional layers of metal and dielectric are added to this basic structure in order to route the electrons to Applying MiGaNTM , GaN Devices in High Reliability theSpace gate, drain, and source input/output terminals.and ThisReliability structure is repeated many times to form the and Applications for Maximum Performance resultant power device. Figure 1. GaN HEMT Structure notStructure to scale.) (Unenhanced, Figure(Unenhanced, 1. GaN HEMT S ---- Key: G not to scale.) ------------------ D Source Connection/Field Plate Gate and Drain Connections Dielectric Protection Layer AlGaN Layer GaN Layer AlN Isolation Layer Silicon Substrate Layer --- 2-D Electron Gas The inherent structure yields GaN devices that behave similarly to silicon MOSFETs, with a few notable exceptions. The inherent structure GaN devices thatGaN behave similarly to silicon MOSFETs, with a few notable Because the gate region ofyields an enhancement mode MESFET is naturally depleted, no p-body diode is created; hence, there is no parasitic p-n junction between the substrate (source) and the drain, as is present in conventional exceptions. Because the gate region of an enhancement mode GaN MESFET is naturally depleted, no psilicon As such,hence, there isthere no conventional “body” present in the the device’s structure. This and doesthe not mean, bodyMOSFETs. diode is created; is no parasitic p-ndiode junction between substrate (source) however, that there is not reverse conduction functionality in the inherent GaN HEMT device operation. drain, as is present in conventional silicon MOSFETs. As such, there is no conventional “body” diode present in the device’s structure. This does not mean, however, that there is not reverse conduction When the gate-source junction of the device is at zero bias condition, there is a depletion region (i.e. absence of elecfunctionality theThis inherent HEMT devicetooperation. trons) under the in gate. actionGaN causes the channel be open. However as current is forced into the source, the drain terminal makes an excursion below ground (as would occur in a circuit with inductance carrying current at the drain,) When the gate-source junction of thebiased device is electrons at zero bias there a depletion region (i.e. junction the gate-drain junction becomes forward and are condition, injected under theisgate. When the gate-drain reaches, then exceeds, the threshold voltage, the channel begins to conduct. absence of electrons) under the gate. This action causes the channel to be open. However as current is forced into the source, the drain terminal makes an excursion below ground (as would occur in a circuit Due to the presence of the 2DEG in the channel, the conduction mechanism is comprised entirely of majority carriers. As such, with no minority carriers present, there is no recombination time and thus no (reverse) recovery time. This is an important difference between the parasitic body diode of the silicon MOSFET and the “diode” inherent in the third quadrant operation of the GaN HEMT. Another difference is that although there are no charge recovery losses in the GaN device, because the threshold must be exceeded to turn on the channel, the forward voltage drop of the GaN device “diode” is higher than that obtained in conventional silicon MOSFETs. Operational Areas of Concern for GaN Devices dv/dt (Miller)-Induced Turn On The structure and construction of the GaN device allows for inherent high speed operation: Switching times of 5 nanoseconds or less are possible. Such high voltage change rates (dv/dt) may make it necessary to be vigilant regarding unwanted, so-called Miller effect, turn on of the gate terminal during the high speed rise of the drain-source voltage in current fed Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 2 The structure and construction of the GaN device allows for inherent high speed operation: Switching times of TM 5 nanoseconds are possible. Such high voltage change rates (dv/dt) may make it Applying MiGaN , GaN Devicesorinless High Reliability necessary to be vigilant regarding unwanted, so-called Miller effect, turn on of the gate terminal during and Space Applications for Maximum Performance and Reliability the high speed rise of the drain-source voltage in current fed applications such as point-of-load (POL) power converters. In such circumstances, depending upon the ratio of the Miller feedback charge (Qgd) applications such as point-of-load (POL) power converters. In such circumstances, depending upon the ratio of the Miller to the gate to source charge (Qgs), a device that is intended to be OFF (and driven as such) may turn on feedback charge (Qgd) to the gate to source charge (Qgs), a device that is intended to be OFF (and driven as such) may duringthe thehigh high rate of voltage change its drain terminal. This causes action causes unwanted turn on during rate of voltage change at itsatdrain terminal. This action unwanted transienttransient current to flow current to flow in the “OFF” device,power and can lead to and/or excessive power dissipation and/orordevice failure in the “OFF” device, and can lead to excessive dissipation device failure if not controlled eliminated by if notVcontrolled eliminated by design. V devices arebecause inherently design. 40 devices areor inherently immune to dv/dt40 induced turn-on the immune Miller ratiotoisdv/dt belowinduced 1 when turn-on VGS = 0 V. Future generations of Miller enhancement FETsV are to have miller ratios below 1 with VGS = 0GaN V. Figure = 0expected V. Future generations of enhancement mode because the ratio ismode belowGaN 1 when GS all 2a illustrates a simplified POL output stage with the important operational elements included. FETs are all expected to have miller ratios below 1 with VGS = 0 V. Figure 2a illustrates a simplified POL output stage with the important operational elements included. Figure 2. Typical POL Converter Output Stage. Figure 2. Typical POL Converter Output Stage. +Vdd Drivers and PWM +Vdd Qcon Vsw Lo Vsw Co Lo Cgd +Vo Qsyn Qcon Rdrv(pd) Rg +Vo Qsyn Co Cgs a.) b.) Figure 2b shows the circuit of Fig. 2a with equivalent and parasitic elements included, shown in grey. Figure 2b shows the circuit of Fig.resistance 2a with equivalent and parasitic included, shown inresistance, grey. Consider the point equivalent driver pull down Rcon in series withelements theQinternal HEMT gategate Rg. The drv(pd) justand closes. Switch OFF, and the is held low via the Consider where switch syn where switch Qconthe justpoint closes. Switch Qsyn Q is OFF, the gate is held lowisvia the equivalent driver pull down voltages across Cgd and Cgs are approximately 0 V each. The rate of voltage change at node VSW is resistance Rdrv(pd) in series with the internal HEMT gate resistance, Rg. The voltages across Cgd and Cgs are approximately 0 V approximately Vdd/tr(Qcon) (as Vsw makes an excursion from approximately 0 V to approximately Vdd),approxieach. The rate of voltage change at node VSW is approximately Vdd/tr(Qcon) (as Vsw makes an excursion from and this voltage rate causes current to flow rate in capacitor gd equivalent mately 0 V to approximately Vdd),a and this voltage causes a C current to flow into: capacitor Cgd equivalent to: I Cgd C gd dVsw / dt This current flows into the equivalent impedance of Rdrv(pd) in parallel with Cgs. If the voltage impressed upon the gate in parallel with CgsThis . If can the voltage impressed This current the time equivalent impedance of Rdrv(pd) exceeds Vgs(th) flows duringinto the rise (tr) event then the HEMT will turn-on parasitically. occur with bipolar-transisduring the rise time (tr) event HEMT or will turn-on parasitically. upon the gate exceeds Vgs(th) tor-based gate drivers (whose output is based on the Vce(sat) of athen driverthe transistor) with MOS-based gate drivers with an This unacceptably high pullbipolar-transistor-based down resistance. can occur with gate drivers (whose output is based on the Vce(sat) of a driver transistor) or with MOS-based gate drivers with an unacceptably high pull down resistance. There is an operational boundary condition at which the GaN device will be guaranteed to be off during the rise time transient – when ICgd · Req < Vgs(th) … so long as ICgd /Cgs · tr > Vgs(th) There is an operational boundary condition at which the GaN device will be guaranteed to be off during Req <a low Vgs(th) … so long as ICgddriver, /Cgs ·ortr provisioning > Vgs(th) the driving rise time – when ICgd · with Either thetransient gate of the GaN device pull-down resistance for a small gate reverse (OFF) bias, will assure that Miller-induced turn-on, and the efficiency and reliability consequences it entails, can never ocgate the GaN device with a low pull-down resistance provisioning forvoltage a cur.Either Care driving must bethe taken to of account for additional reverse conduction voltage when driver, using a or negative gate drive as thesmall drain gate voltage (reverse conduction voltage) will “follow” the gate voltage causing a higher VSD reverse (OFF) bias, will assure that Miller-induced turn-on, and the efficiency and reliability consequences it entails, can never occur. Care must be taken to account for additional reverse Maximum Drain-Source Voltage conduction voltage when using a negative gate drive voltage as the drain voltage (reverse conduction voltage) will “follow” the gate voltage causing a higher V A second area of concern for the GaN device is the fact that unlikeSDmany conventional silicon MOSFETs, the GaN HEMT is not avalanche rated at the breakdown of the drain-source junction. Accordingly, in order to maintain maximum reliability, Drain-Source it isMaximum necessary to insure that theVoltage maximum drain-source voltage (Vds) be guaranteed by design to remain within desired A second area of concern for the GaN device is the fact that unlike many conventional silicon MOSFETs, the GaN HEMT is not avalanche rated at the breakdown of the drain-source junction. Corporation Accordingly, in order to maintain maximumMicrosemi reliability, it is necessary to insure that the maximum drainOne Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 limits. To achieve source voltage (Vds) be guaranteed by design to remain within desired (and de-rated) 3 the necessary limiting of the maximum Vds there are two options: unconstrained or constrained operation. MOSFETs, the GaN HEMT is not avalanche rated at the breakdown of the drain-source junction. Accordingly, in order to maintain maximum reliability, it is necessary to insure that the maximum drainguaranteed by design to remain within desired (and de-rated) limits. To achieve source voltage ds) beDevices Applying MiGaNTM(V , GaN in High Reliability there are two options: unconstrained or constrained the necessary limiting of the maximum V and Space Applications for Maximum Performance and Reliability ds operation. (and de-rated) limits. To achieve the necessary of the maximum Vds are two options: V unconstrained or conUnconstrained operation relies on passivelimiting components to achieve thethere desired maximum ds, such as, for strained operation. example, the resonant reset of a single transistor forward converter (RRFC) as shown in Figure 3. In this case the peak voltagerelies encountered bycomponents the drain istodependent upon the peak of the reset resonance Unconstrained operation on passive achieve the desired maximum Vds, such as, for example, the )of the power isolation voltage, which is dependent upon the magnetizing inductance (L m Figure 3. In this case thetransformer resonant reset of a single transistor forward converter (RRFC) as shown in peak voltage encounCoss +resonance (Cdf/(Ns/Np)) ( where is the capacitance of the andbythe at the drain (Cthe tered thecapacitance drain is dependent upon terminal the peak of voltage, which C isdfdependent upon the magnetizing r = reset inductance power isolation and the capacitance at the drain the terminal (Cr resonance = Coss + (Cdf/(Ns/Np)) ( forward (Lm)of outputthe rectifier) plus anytransformer external capacitance utilized to achieve desired where Cdf is the capacitance of there the forward output rectifier) plus any external capacitance utilized and to achieve characteristics.) However, are variations in these passive elements from lot-to-lot due tothe desired resonance characteristics.) However, there are variations in these passive elements from lot-to-lot and due to temperature temperature changes. Therefore it is more difficult to control the maximum Vds of the HEMT except to changes. Therefore it is more difficult to control the maximum Vds of the HEMT except to guarantee that it falls within a guarantee that it falls within a window of tolerance. window of tolerance. The peak resonance voltage atdrain the drain is determined The peak resonance voltage at the is determined by: by: Vres(pk) Vdd Il(pk) Lm/Cr Where Il(pk) is determined Where Il(pk) is determined by: by: Il(pk) dd ton)/Lm Il(pk)0.5 0.5 (V (V dd ton)/Lm Il(pk) 0.5 (Vdd ton)/Lm And the duration of the reset event is: And the duration of the reset event is: trestres LL m Cr m Cr tres Lm Cr And duration ofreset the reset And the the duration of the eventevent is: is: Figure 3. 3. Single Transistor, Resonant-Reset Forward Converter. Figure Single Transistor, Resonant-Reset Forward Converter. Figure 3. Single Transistor, Resonant-Reset Forward Converter. Figure 3. Single Transistor, Resonant-Reset Forward Converter. Vds(t) Vds(t) tres tres Vres Vres Vds(t) tres +Vdd +Vdd Vres Vdd Vdd Vdd Von Von ton ton T t toff toff Von T ton t toff Df Df Tiso Tiso t Vd Vd T PWM PWM Qsw Qsw PWM +Vdd Lo Lo Ds Ds Tiso Vd Cres Cres Df + Lo + Vo Co Vo Co Ds - - Qsw + Vo Co - Cres primary voltage on time-voltage product (Von · ton) must equal InInorder iso),),the ordertotoreset resetthe thetransformer transformer(T(T iso the primary voltage on time-voltage product (Von · ton) must equal · ).).This means atathigher duty than the primary off time-voltage product (V off ·toff off ), the primary voltage oncycles time-voltage (V In order to reset product the transformer (T isoThis on · ton) must equal means higher duty cycleswhere wheretproduct toffisisless less than the primary off time-voltage (V off toff greater than V . Now because of the resonant reset characteristic, V , which tonton, ,VV off isisnecessarily on off · t ). This means at higher duty cycles where the primary off time-voltage product (V off resonant reset characteristic, Voff, whichisistoff is less than necessarily greater than Von. Now becauseoffof the off +V , may assume values greater than V at duty cycles greater atata aduty VV dd +V res , may dd at , Voff is values necessarily greater because ofthan the 0.5. resonant reset characteristic, tonassume on. Now greater than than V cycles greater than 0.5.For Forexample example duty Voff, which is dd res dd Vduty will be t /t · V cycle of 0.75 (75%), which is the practical operating limit for the RRFC, V off on off dd ddat a duty +V , may assume values greater than V at duty cycles greater than 0.5. For example V dd reswhich is the practical operating limit dd for the RRFC, Voff will be ton/toff · Vdd==3·V 3·V cycle of 0.75 (75%), dd will be approximately 1.41 times higher than that value. This means that the power switch, ––and V res will will be t /t · Vdd = 3·Vdd cycle of 0.75 (75%), which is the practical operating limit for the RRFC, V off on off be approximately 1.41 times higher than that value. This means that the power switch, and V res be able to withstand a de-rated off-state drain voltage of at least 4.2·V . QQ sw, ,must dd will be approximately 1.41 times higher than that value. This means that the power switch, – and V withstand a de-rated off-state drain voltage of at least 4.2·Vdd. sw must be able to res Qsw, must be able to withstand a de-rated off-state drain voltage of at least 4.2·Vdd. duty cycle relationship demands that, for a particular power switch with a given The previous V Microsemi Corporation off versus The previous V off versus duty cycle relationship demands that, for a particular power switch with a given One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Novwith 2013 a given , the duty cycle must be necessarily limited. If the available power switch has a abreakdown voltage BV dss versus dutylimited. cycle relationship demands for ahas particular power switch Thecycle previous mustVbeoffnecessarily If the available powerthat, switch breakdown voltage BVdss, the duty = 28beVdc (with value ofof20% oror32 Vdc), ofof100 the supply voltage VV dd , the duty cycle must necessarily limited. If tolerance the available power switch has a breakdown 4voltage dss Vdc (witha amaximum maximum tolerance value 20% 32 Vdc), 100V,V,and andBV the supply voltage dd = 28 then bebelimited totoavoltage ofof69%, totoapplying de-rating. And =value 28 Vdc (withprior a maximum tolerance value of since 20% ofcycle 100must V, and the supply Vdd value thenthe theduty dutycycle must limited amaximum maximum 69%, prior applying de-rating. And sinceor 32 Vdc), Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability In order to reset the transformer (Tiso), the primary voltage on time-voltage product (Von · ton) must equal the primary off time-voltage product (Voff · toff). This means at higher duty cycles where toff is less than ton, Voff is necessarily greater than Von. Now because of the resonant reset characteristic, Voff, which is Vdd+Vres, may assume values greater than Vdd at duty cycles greater than 0.5. For example at a duty cycle of 0.75 (75%), which is the practical operating limit for the RRFC, Voff will be ton/toff · Vdd = 3·Vdd – and Vres will be approximately 1.41 times higher than that value. This means that the power switch, Qsw, must be able to withstand a de-rated off-state drain voltage of at least 4.2·Vdd. The previous Voff versus duty cycle relationship demands that, for a particular power switch with a given BVdss, the duty cycle must be necessarily limited. If the available power switch has a breakdown voltage of 100 V, and the supply voltage Vdd = 28 Vdc (with a maximum tolerance value of 20% or 32 Vdc), then the duty cycle must be limited to a maximum value of 69%, prior to applying de-rating. And since Vres is dependent upon parametric values, then the variation of these parameters must be accounted for as a result of tolerance, temperature and age. These variations result in further restriction of the maximum duty cycle of the RRFC. The application of the RRFC means that the designer must be cognizant of and accommodate for many variables in order to insure that the maximum drain-source voltage of the power switch is not exceeded. Aforward foolproofconverter method for(TTFC) achieving a tightly-controlled Vds is to use Constrained operation utilizes the shown in Figure 4. Although theconstrained architectureoperation. of this power converter is more clamping of the drain voltage to a known voltage potential, and thereby gives the designer tacit control of the maximum complex and requires more Vds. An example of constrained operation is the two-transistor forward converter (TTFC) shown in Figure 4. Although the each power transistor is clamped to the components to implement, it has the advantage that the Vds of architecture of this power converter is more complex and requires more the two forward clamping diodes D and Dc2power . The supinput powertosupply voltage, dd plus components implement, it hasVthe advantage that the Vdsvoltage of each drops power of transistor is clamped toc1the input major limitation of the TTFC is that the duty cycle is limited to below 50%. Limitations aside, the use of is ply voltage, Vdd plus the two forward voltage drops of clamping diodes Dc1 and Dc2. The major limitation of the TTFC power transistor is kept constant overpolicy the entire thethe TTFC an insurance Vds of each that dutyis cycle is limited topolicy belowthat 50%.the Limitations aside, the use of the TTFC is an insurance that the Vds of each power transistorconditions. is kept constant over the entire range of operating conditions. range of operating Although twotwo power switching transistors are required for thisfor configuration, devices with lowerwith Rds(on) may be utiAlthough power switching transistors are required this configuration, devices lower Rds(on) lized because the maximum Vds of the devices is kept to a lower value using the clamping scheme -- and lower voltage is kept to a lower value using the clamping may be utilized because the maximum Vds of the devices HEMT’s inherently possess lower ON state resistances. This means that the efficiency of the TTFC may be comparable to scheme -and lower voltage HEMT's inherently possess lower ON state This that the that of the RRFC, with the only drawback being slightly greater complexity in theresistances. implementation of means the TTFC. efficiency of the TTFC may be comparable to that of the RRFC, with the only drawback being slightly greater complexity in the implementation of the TTFC. Figure 4. Two Transistor Forward Converter. Figure 4. Two Transistor Forward Converter. +Vdd Vds(t) Vdd + 2 Vf Qsw1 Von ton toff t T The voltage in the shaded area during the off time will assume a value between 0V and Vdd, depending upon operating conditions, after the transformer has reset. Gate Drivers and PWM Dc2 Dc1 Lo Df Vd2 Tiso + Ds Vo Co - Vd1 Qsw2 Maximum Gate-Source Voltage Microsemi Corporation The third area of concern for thePh: GaN device is limited gate voltage operating www.microsemi.com range versus the Rev. 1.0 Nov 2013 949-380-6100 Sales.Support@microsemi.com conventional silicon MOSFETs. Available GaN HEMT devices have a gate voltage range of +6 to -5 V. 5 This compares to a +/-20V range for a conventional MOSFET. Complicating this situation is the fact that full enhancement of the GaN HEMT device (and the corresponding maximum current carrying One Enterprise, Aliso Viejo, CA 92656 Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability Maximum Gate-Source Voltage The third area of concern for the GaN device is limited gate voltage operating range versus the conventional silicon MOSFETs. Available GaN HEMT devices have a gate voltage range of +6 to -5 V. This compares to a +/-20V range for a conventional MOSFET. Complicating this situation is the fact that full enhancement of the GaN HEMT device (and the corresponding maximum current carrying operating point) is not achieved until a gate-source potential of +4V. The reason that it is essential to not exceed the maximum (or minimum) gate-source voltage can be explained by the breakdown characteristic of the gate-source junction. Figure 5 is a curve tracer screen capture that illustrates the gate source breakdown characteristic of a typical GaN HEMT. Obtained using a very narrow pulse width (20 µs) and low repetition rate (100 Hz) to minimize the average power dissipation, it clearly shows the sharpness of the breakdown characteristic – the steepness of the breakdown curve essentially mimics a Schottky diode in the forward direction. This is because the gate-source (or gate-drain) junction is basically a metal-semiconductor junction. Consequently, smallsmall excursions in gateinvoltage beyondbeyond the +6 V/-5 V rating yield large to becurrents drawn by Consequently, excursions gate voltage the +6 V/-5will V rating will currents yield large tothe gate. The destructive process occurs as a result of the energy supplied to the gate as a result of an uncontrolled transient. be drawn by the gate. The destructive process occurs as a result of the energy supplied to the gate as a Theresult point of at an which each devicetransient. will fail due to point a highat energy the gate willfail be dependent upon the physical uncontrolled The whichinsult eachtodevice will due to a high energy insult size to of the die (affecting thermal resistance) and any minor imperfections in the gate-source/drain structure, and of course the the gate will be dependent upon the physical size of the die (affecting thermal resistance) and any minor magnitude and duration of the insult. imperfections in the gate-source/drain structure, and of course the magnitude and duration of the insult. Figure 5. Typical GaN HEMT Gate-Source Breakdown Characteristic. Figure 5. Typical GaN HEMT Gate-Source Breakdown Characteristic. This situation requires that the designer be careful with the accuracy/tolerance of the bias level of the power supply that provisions the gate driver. The designer MUST additionally insure that under all transient conditions that the gate potential is never allowed to exceed +6 V peak, and realistically lower than that value as a performance guard band. To this end, MiGaNTM GaN device in U4A package has been optimized to assist the designer in minimizing ringing and other transients due to gate/drain current interactions resulting from parasitic inductances. The I/O pad out of this U4A SMT package is shown in Figure 6a. The package provides four separate connections to the GaN HEMT inside, as shown in Figure 6b. The 'gate return' pad adjacent to the 'gate' Microsemi Corporation enables the designer to optimize the gate drive loop independently of thewww.microsemi.com high current drain-source Onepad Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com Rev. 1.0 Nov 2013 6 output loop, as shown in Figure 6c. The 'gate return' pad is connected directly to the source on the die internal to the package, thus eliminating deleterious load current and gate current interactions. The Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability This situation requires that the designer be careful with the accuracy/tolerance of the bias level of the power supply that provisions the gate driver. The designer MUST additionally insure that under all transient conditions that the gate potential is never allowed to exceed +6 V peak, and realistically lower than that value as a performance guard band. To this end, MiGaNTM GaN device in U4A package has been optimized to assist the designer in minimizing ringing and other transients due to gate/drain current interactions resulting from parasitic inductances. The I/O pad out of this U4A SMT package is shown in Figure 6a. The package provides four separate connections to the GaN HEMT inside, as shown in Figure 6b. The ‘gate return’ pad adjacent to the ‘gate’ pad enables the designer to optimize the gate drive loop independently of the high current drain-source output loop, as shown in Figure 6c. The ‘gate return’ pad is connected directly to the source on the die internal to the package, thus eliminating deleterious load current and gate current interactions. The benefit to the designer is that the high current, high di/dt drain current cannot influence the transient-sensitive gate current loop due to external (to the package) parasitic inductances and resistances in series with the high current source terminal. A second benefit is that during current commutation, power source inductance is separated from gate return inductance preventing the voltage induced by di/dt across the power during source turn oninductance (off). Source common to the gate anddrive power loopsduring (common from inductance being subtracted (added) from (to)drive the gate voltage turn onsource (off). Source inductance common to the gate drive and power loops (common source inductance or CSI) is a major contributor to losses inductance or CSI) is a major contributor to losses during current commutation. during current commutation. However, just providing the 'gate return' padpad on the U4A package harmfultransient voltages However, just providing the ‘gate return’ on the U4A packageisisnot notenough enough to to prevent prevent harmful TM from appearing at appearing the ‘gate’ terminal of theterminal MiGaNTMofGaN most consideration for reducing or MiGaNThe GaN important device. The most transient voltages from at the 'gate' the device. eliminating voltage overshoot in the gate current loop is to reduce the parasitic inductance in the gate important consideration for reducing or eliminating voltage overshoot in the gate current loop is to turn-on current Ig(on). The total loop in area this turn-on high transient current determines, in loop large area part, of thethis parasitic reduce loop, the parasitic inductance theofgate current loop,path Ig(on). The total high inductance present in this current loop. transient current path determines, in large part, the parasitic inductance present in this current loop. Figure 6. Microsemi MiGaNTM GaN in U4A Package and Optimized Current Loops. Figure 6. Microsemi MiGaNTM GaN in U4A Package and Optimized Current Loops. Vdd Gate Gate Return Drain Source Ig(on) Qsw Driver Gate In Gate Return Load Vgate Drain Source Id Ig(off) Cbypass (bottom view) a.) b.) c.) The principal goal for the designer is therefore to keep the connections from the output of the gate driver to the gate, from the power input of the gate driver to the power supply bypass capacitor (Cbypass) and from the 'gate return' pad to the power supply bypass capacitor as short as possible, and, if possible, route drive and return paths on separate board layers over each other to cancel inductance. It is recommended that the 'gate return' connection in the gate loop be implemented as a small copper etch area on the PCB. This implementation mimics, on a smaller scale, the properties of a ground plane. The power supply bypass capacitor should be located and connected directly across the power supply and ground pins of an IC gate driver IC – or as close as possible to the high current driver elements of a discrete gate driver circuit. The connection from the output from the gate driver should be as short as practicably possible. The width of this connection should be at least ½ of the length in order to minimize unwanted parasitic elements. Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com It is sometimes impossible to reduce the loop area enough to prevent unwanted loop inductance. This might happen because of component sizes or printed circuit board restrictions. Figure 7 shows the Rev. 1.0 Nov 2013 7 Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability The principal goal for the designer is therefore to keep the connections from the output of the gate driver to the gate, from the power input of the gate driver to the power supply bypass capacitor (Cbypass) and from the ‘gate return’ pad to the power supply bypass capacitor as short as possible, and, if possible, route drive and return paths on separate board layers over each other to cancel inductance. It is recommended that the ‘gate return’ connection in the gate loop be implemented as a small copper etch area on the PCB. This implementation mimics, on a smaller scale, the properties of a ground plane. The power supply bypass capacitor should be located and connected directly across the power supply and ground pins of an IC gate driver IC – or as close as possible to the high current driver elements of a discrete gate driver circuit. The connection from the output from the gate driver should be as short as practicably possible. The width of this connection should be at least ½ of the length in order to minimize unwanted parasitic elements. It is sometimes impossible to reduce the loop area enough to prevent unwanted loop inductance. This might happen because of component sizes or printed circuit board restrictions. Figure 7 shows the SPICE simulation output for the gate voltage of a GaN HEMT with series inductance values (between the gate driver and the gate) ranging from 1 nH to 20 nH. It is clear that for series inductance up to 2 nH, the gate voltage does not exceed the absolute maximum value of +6 V. For the larger values of series inductance unavoidably present in the gate circuit, all is not lost, as the designer has a valuable option to use to reduce the magnitude of the parasitic resonance peak voltage: damping resistance. This damping resistance should be placed in series with the output of the gate driver and the GaN HEMT gate. Figure 8 shows the gate voltage simulation results for the case of 5 nH of series inductance with a damping resistance value varied from 0 to 1 Ω in 0.25 Ω increments. and the GaN HEMT gate. Figure 8 shows the gate voltage simulation results for the case of 5 nH of seriesHEMT inductance with aSimulation: damping resistance value varied to 1nH. Ω in 0.25 Ω increments. Figure 7. GaN Gate Voltage Series Inductance From 1from nH to0 20 Figure 7. GaN HEMT Gate Voltage Simulation: Series Inductance From 1 nH to 20 nH. ----- 1nH ----- 2nH ----- 5nH ----- 10nH ----- 20nH Figure 8. GaN HEMT Gate Voltage Simulation: Series Inductance 5 nH, Damping Resistance From 0 to 1.0 Ω. ----- 0 ----- 0.25 ----- 0.5 ----- 0.75 ----- 1 Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 8 Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability Figure 8. GaN HEMT Gate Voltage Simulation: Series Inductance 5 nH, Damping Resistance From 0 to 1.0 Ω. Figure 8. GaN HEMT Gate Voltage Simulation: Series Inductance 5 nH, Damping Resistance From 0 to 1.0 Ω. ----- 0 ----- 0.25 ----- 0.5 ----- 0.75 ----- 1 For example, be seen in Figure 7 that at the 5 nHthe value that5the voltage blue) just barely in exceeds Forit can example, it can be seen in the Figure 7 that at the nHgate value that (shown the gateinvoltage (shown blue) the +6 V maximum rating of the device. 7 showsrating the gate voltage for this 5 nH7loop withthe a gate just barely exceeds the +6 Figure V maximum of the device. Figure shows gatedamping voltageresistance for this 5 added – the gate voltage is maintained below the +6 V level for damping resistances of 0.5 Ω or greater. nH loop with a gate damping resistance added – the gate voltage is maintained below the +6 V level for or greater. damping resistances of 0.5thedamping Caution must be exercised in applying resistance as when the value is increased, the peak available gate current is limited, and the rise and fall times of the gate voltage are increased. The net effect is a decrease in the overall Caution must –beforexercised applyinginthe dampingefficiency. resistance when the value increased, the peak performance of the circuit example aindecrease conversion So,asthe designer must is keep the damping resistance to the lowest reasonable that balances the gate switching desired are and increased. the maximum available gate current isvalue limited, and the rise and fall times performance of the gate voltage Thepeak net gate voltageeffect allowed. is a decrease in the overall performance of the circuit – for example a decrease in conversion Finally, if an integrated or discrete driver is used that has separate gate pull up and pull down outputs, it is recommended that the damping resistance be utilized in the gate pull up output only, as ratings-threatening overshoots in gate voltage will be encountered during and affect only the turn on event. This technique allows the switching performance to be maximized in that the performance of the turn on loop is only, necessarily, affected by the required damping and the turn off loop remains optimized. Thermal Considerations and Linear Mode Operation A fourth area of operational concern for the GaN HEMT device is that they are, by design, intended to be used as a high speed saturated switch. As such, it is not intended for linear operation such as a current source or an amplifier. There are two reasons for these operational limitations. The first is the fact that the HEMT die element is mounted directly to the U4A package “face down” with solder, such that conventional wire bonds (and the inevitable inductance associated with these connections) are eliminated. The gate, drain and source connections all must be made on the same side of the die, so necessary isolation gaps must be included between these contacts. These gaps then result in areas on the die face where thermal contact is not (and cannot) be made to the package base. Accordingly, this mounting technique results in a higher thermal resistance than if the die were mounted via its substrate – where the entire substrate area is utilized as the thermal contact to the package base – and wire bonds are employed for the remainder of the I/O connections. This necessarily higher thermal resistance limits the amount of power that may be dissipated by a given size GaN HEMT die: It is this power dissipation limit that necessarily restricts the device in its linear operation mode.While the GaN devices are not optimized for linear operation, it is noteworthy to point out that they have a positive temperature coefficient over the entire operationg range. While there are thermal disadvantages to vertical MOSFETs, current will be naturally spread over the entire device (or even devices in parallel), where the MOSFET can fail due to localized heating. Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 9 Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability Microsemi’s MiGaNTM GaN FETs are optimized by design for high-speed, saturated switching. It is in this application regime where the GaN HEMT outshines all competing devices. Even so, the power dissipation of the device rises as Id2 * Rds(on) when it is saturated, and at higher operating currents care must be taken not to exceed the maximum junction temperature under all operating conditions. This is particularly true in high current, high duty cycle applications such as the synchronous (lower) device in a point-of-load converter’s (POL’s) output stage. For example, for a 12 V-to-1 V POL providing 25 A of output current, the duty cycle for the synchronous switch is (1 – 1/12) = 91.7%, not that far away from DC! If a 7 mΩ GaN switch (MiGaNTM Product : MGN2915U4A) is utilized for the synchronous switch, then the power dissipation of the device just due to DC losses is 252 * 0.007 * 0.917 = 4.0 Watts. With switching losses and gate drive losses included, this dissipation increases to almost 5 Watts. The maximum junction temperature for the MGN2915U4A is 150°C and the junction-to-case thermal resistance is 2°C/W, so the system designer must provision a PCB cooling solution that will provide less than 3°C/W of thermal resistance from the U4A case-to-ambient to insure reliable operation at the maximum ambient temperature of 125°C. Thermal resistances in this range are difficult to achieve/obtain with conventional printed circuit board fabrication technologies. In systems utilizing surface-mount packaging for power devices, such as the U4A package, Microsemi recommends a PCB stack up that includes a layer of heat dispersing metal in the multi-layer “sandwich” to draw heat efficiently from the power dissipating elements, as shown in Figure 9. This approach allows heat to be transferred in the most Inefficient systemsmanner utilizing surface-mount packaging for of power devices, such material as the U4A Microsemi -- vertically though the think layers printed circuit board and package, copper clad then to the interecommends PCBwhich stackthen up that includes a layer of heat dispersing the multi-layer “sandwich” grated metal acore, conducts the heat laterally to the heat sinkmetal or coldinplate coupled to the ambient temperthan laterally through direct-contact copper etch/cladasand then spread throughout the board by incidental toature, drawrather heat efficiently from the power dissipating elements, shown in Figure 9. This approach allows thermal conduction paths. High performance thermal systems as described previously are available from various heat to be transferred in the most efficient manner -- vertically though the think layers of printed circuit manufacturers, the most notable are Arlon with their StaCoolTM material, Denka with their HITT Plate or ALSINK board material and copper clad then to the integrated metal core, which then conducts the heat laterally materials, Bergquist with their Thermal Clad material and Laird with their TlamTM material. These thermal systems, toalong the heat cold plate coupled to the ambient temperature, rather thansolution laterally directwithsink SMTor packages such as the U4A provide a reliable, thermally-efficient to through component cooling, and contact copper etch/clad and then spread throughout the board by incidental thermal conduction enable the designer to exploit the full potential of and maximum performance from their power circuits. paths. High performance thermal systems as described previously are available from various manufacturers, TM TM Figure MiGaNare GaN Products in U4A Packagematerial, Mounted to Thermally Multi-Layer System w/Metal Denka with Efficient their HITT Plate orPCB ALSINK the most 9.notable Arlon with their StaCool TM Cooling Core. materials, Bergquist with their Thermal Clad material and Laird with their Tlam material. These thermal systems, along with SMT packages such as the U4A provide a reliable, thermally-efficient The goal of the thermal system shown in Figure 9 is to minimize the thermal impedance of the lateral conduction solution to component cooling, and enable the designer to exploit the full potential of and maximum layer through the PCB dielectric/copper etch. This may be done by maximizing the copper thickness and minimizing performance their Another power circuits. the dielectricfrom thickness. important design goal is to insure that the coefficient of thermal expansion (CTE) of the metal heat sink/spreader is closely matched to that of the PCB dielectric to prevent delamination and voids -- TM Figure 9. MiGaN GaN Products in U4A PackageofMounted to Thermally Efficient Multi-Layer PCB which would adversely affect the thermal performance the system. System w/Metal Cooling Core. U4A Tcase PCB Tsink Metal Heat Sink/Spreader Tsink Side/Cross-Section View – Not to Scale The goal of the thermal system shown in Figure 9 is to minimize the thermal impedance of the lateral conduction layer through the PCB dielectric/copper etch. This may be done by maximizing the copper thickness and minimizing the dielectric thickness. Another important design goal is to insure that the coefficient of thermal expansion (CTE) of the metal heat sink/spreader is closely matched to that of the Microsemi Corporation PCB dielectric to prevent delamination and voids -- which would adversely affect the thermal One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 performance of the system. 10 Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability Gate Drive Circuits One of the more challenging tasks for driving a Rad-hard GaN HEMT (or conventional silicon MOSFET for that matter) is finding a suitable high speed driver with acceptable switching characteristics. This is particularly true for devices that support operation with a power supply bias of +5 Vdc (in accommodation of the maximum GaN HEMT gate voltage requirement.) devices available in the U4A package. This driver exhibits a total throughput delay time (td(on) + tr + To this Microsemi hasnscharacterized several available gate driverrange. integrated as fall welltimes as a discrete of less than 275 over the -55°C to 125°C temperature Thecircuits rise and when altertd(off) + tf ) end native. For power conversion at frequencies less than 200 kHz, the Microsemi SG1644 device was found to provide driving a 1500 pF load are less than 50 ns over the previous temperature range. acceptable drive performance for the breadth of rad-hard GaN HEMT devices available in the U4A package. This driver exhibits a total throughput delay time (td(on) + tr + td(off) + tf ) of less than 275 ns over the -55°C to 125°C temperature A discrete bipolar transistors (Microsemi 2N2369A) is shown Figure range.gate The driver rise andutilizing fall timesRad-hard when driving a 1500 pF load are less than 50 ns over the previousintemperature range. 10. An all-NPN design is required as there are no suitable rad-hard PNP transistors with fast enough A discrete driver utilizing Rad-hard bipolar transistors (Microsemi 2N2369A) shown in Figure switching timesgate available. This discrete design exhibits a total throughput delay istime of less than 10. 150An nsall-NPN design is required as there are no suitable rad-hard PNP transistors with fast enough switching times available. over the -55°C to 125°C temperature range. The rise and fall times when driving a 1500 pF load are less This discrete exhibits a total throughput range. delay time less than 150 ns over the -55°C range. The than 30 ns design over the previous temperature Theofadvantage of the discrete designtois125°C that ittemperature is rise and fall times when driving a 1500 pF load are less than 30 ns over the previous temperature range. The advantage significantly faster than the SG1644 IC, but the disadvantage is that it is more complicated – requiring 6 of the discrete design is that it is significantly faster than the SG1644 IC, but the disadvantage is that it is more comtransistors and 9 resistors and capacitors, excluding supply bypass power capacitors, driver. plicated – requiring 6 transistors and 9 resistors andpower capacitors, excluding supplyper bypass capacitors, per driver. However, for end-user applications switching at frequencies greater than 200 kHz there are other However, for end-user applications switching at frequencies greater than 200 kHz there are nono other reasonable alternareasonable at the present time. tives atalternatives the present time. Figure 10. Discrete GaN HEMT Gate Driver Circuit. Figure 10. Discrete GaN HEMT Gate Driver Circuit. Ballast resistor R8 is included in the design shown in Figure 10. However, this component may be Ballast resistor R8 is included in the design shown in Figure 10. However, this component may be eliminated if the gate eliminated if the gate drive area has been minimized or significant overshoot is not drive loop area has beenloop minimized or significant gate voltage overshootgate is notvoltage observed. observed. The simulation results for the 25°C switching performance for the discrete GaN HEMT gate driver are shown in Figure The simulation the 25°C performance the discrete 11. The loadresults for thisfor simulation is switching 1500 pF with 2 mA of gatefor leakage current.GaN HEMT gate driver are shown in Figure 11. The load for this simulation is 1500 pF with 2 mA of gate leakage current. Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Figure 11. Discrete GaN HEMT Gate Driver Circuit Simulation Results. Rev. 1.0 Nov 2013 11 Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability Figure 11. Discrete GaN HEMT Gate Driver Circuit Simulation Results. The trace in Figure 11 is11 the pulsepulse to theto driver, the red the pulse the gate output R8 =with 0 Ω and the0 blue Thegreen green trace in Figure is input the input the driver, redispulse is the gatewith output R8 = trace is the gate output with R8 = 1 Ω. This simulation shows the effect of the damping resistance (in this case R8) on the and the blue trace is the gate output with R8 = 1 . This simulation shows the effect of the damping rise time of the voltage presented to the gate of the GaN HEMT. resistance (in this case R8) on the rise time of the voltage presented to the gate of the GaN HEMT. There is a final area of GaN HEMT device performance that must be included into any accurate SPICE model of the ThereThis is a isfinal of GaN deviceMOSFET performance that must includedDC into any accurate SPICE device. the area fact that unlikeHEMT conventional devices with trulybe negligible gate leakage currents, the GaN model of the device. is the fact that unlike conventional MOSFET with DC HEMT possesses a gateThis leakage current of 2 mA typical and 7 mA maximum at devices a gate bias of truly 5 Vdc.negligible If the simulation results are expected to bethe accurate, particularly for the a peak signal, this leakage value should be7included gate leakage currents, GaN HEMT possesses gatedrive leakage current of 2 mA typical and mA into the SPICE model. maximum at a gate bias of 5 Vdc. If the simulation results are expected to be accurate, particularly for the peak drive signal, this leakage value should be included into the SPICE model. There are exciting developments in progress at Microsemi in regards to high speed rad-hard GaN/MOSFET gate drivers. Several single and dual drivers are in development that will provide total throughput delays of less than 40 ns driving a There exciting inless progress at ns. Microsemi in regards to high speedatrad-hard 3300 pF are load, with risedevelopments and fall times of than 10 These drivers will make operation switching frequencies up to GaN/MOSFET gatepractical. drivers.Please Several singlewith andMicrosemi dual drivers are development will provide total 1.5 MHz possible and consult sales (orinfrequently checkthat at the website at www.microsethroughput of less than 40 driving a 3300 load, with rise and fall times of less than 10 ns. mi.com) for thedelays availability of these IC ns GaN/MOSFET gatepF drivers. These drivers will make operation at switching frequencies up to 1.5 MHz possible and practical. Please consult with Microsemi sales (or frequently check at the website at www.microsemi.com) for the Demonstration Circuits availability of these IC GaN/MOSFET gate drivers. In order to observe the operation and determine the important operating metrics for (GaN HEMT drain and gate voltages and overall circuit efficiency) a properly designed power conversion circuit utilizing the MiGaNTM GaN devices in U4Apackage, it is necessary to have a demonstration circuit for each converter type (RRFC and TTFC.) Demonstration Circuits In order to observe the operation and determine the important operating metrics for (GaN HEMT drain and gate voltages and overall circuit efficiency) a properly designed power conversion circuit utilizing the MiGaNTM GaN devices in U4A-package, it is necessary to have a demonstration circuit for each converter type (RRFC and TTFC.) Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 12 Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability RRFC Demonstration Circuit Figure 12. RRFC Demonstration Circuit using MiGaNTM GaN devices Figure 12. Figure 12 shows the schematic for an open-loop RRFC power output stage utilizing a single Microsemi MiGaNTM GaN TM Figure 13. TTFC Demonstration Circuit MiGaN GaN devices device in SMT-package and Schottky rectifiers. This circuit is designed to accept a 28 V nominal input voltage (Vdd) and a 5.00 V bias voltage (for the gate drive of the GaN HEMT’s), and it provides an isolated 3.3 V output voltage with 15 A maximum output current. The operating switching frequency, determined/limited by the magnetic elements chosen, is 500 kHz. The output voltage is obtained by adjusting the duty cycle. In the circuit, the transistors and resistors bounded by the left-most dashed box form the discrete, high-speed gate driver as previously described and discussed. Transistor QPS1 is the main power switch, an MGN2901U4A, MiGaNTM GaN Product device , 100 V/10 mΩ device selected for its high breakdown voltage. Capacitor CS1 and resistor RS1 are the primary-side snubber/resonance capacitor, which are used to adjust the resonance reset time to the desired value and damp the value of the turn-off leakage inductance voltage spike. Additionally, there are three component locations (CS2, RS2 and DS1) in the right-most dashed box provided in order for the user to observe the efficacy of RCD snubbing in the reduction of the leakage spike. These components may be populated in place of CS1 and RS1. Transformer TP1 is the main power transformer, a Pulse Engineering PA0810NL. This transformer was selected as it provides an off-the-shelf solution, and this transformer also quantifies primary magnetizing inductance (86 µH, typical) – necessary to determine the resonant reset characteristics. Schottky rectifiers D1 and D2, both 1N6845U3’s, are the secondary rectifying diodes selected for their low forward voltage drop, 45 V reverse voltage rating and efficient SMT power package. Components L1 and C7 though C10 form the L-C output filter for the power conversion stage. In operation, a 0 V to +5 V pulse is provided to the PWM Input. The period of this pulse is equal to that of the target operating frequency and the pulse width is set according to: pw = (Vo/Vdd) * (Np/Ns) * T where T = 1/fs, Vo is the desired output voltage, Vdd is the input voltage to the converter’s output stage, Np is the number Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 13 Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability of primary turns on TP1 (6) and Ns is the number of secondary turns (2). Thus, for a 500 kHz conversion frequency, the pulse width is 707 ns for a 3.3 Vdc output voltage. This value is approximate and will have to be adjusted during operation, because this value does not include circuit losses (which increase as the load current increases.) TTFC Demonstration Circuit Figure Figure 13. 13. TTFC Demonstration Circuit MiGaNTM GaN devices Figure 13 shows the schematic for an open-loop TTFC power output stage utilizing Microsemi MiGaNTM GaN device in SMT-package and Schottky rectifiers. This circuit is designed to accept a 28 V nominal input voltage (Vdd) and a 5.00 V bias voltage (for the gate drive of the GaN HEMT’s), and it provides an isolated 3.3 V output voltage with 15 A maximum output current. The operating switching frequency, determined/limited by the magnetic elements chosen, is 500 kHz. The output voltage is obtained by adjusting the duty cycle. In the circuit, the transistors and resistors bounded by the dashed boxes form the discrete, high-speed gate drivers as previously described and discussed. Transistors QD1 and QD2 and their associated passive components provide the level shifting required interfacing to the gate drive for the upper power switch QD1. Transistors QPD1 and QPD2 are the main power switches, a MiGaNTM GaN device, MGN2915U4A 40 V/7 mΩ devices selected for their low Rds(on). Schottky rectifiers D4 and D5 are the primary winding “catch” rectifiers, providing the clamping action to Vdd and ground for the transformer primary-- and thus the two power switches. Schottky rectifier D3 and capacitor C13 form a boost/floating bias for the upper transistor (QPD1) gate drive. Transformer TP2 is the main power transformer, a Pulse Engineering PA0810NL. Schottky rectifiers D1 and D2, both 1N6845U3’s, are the secondary rectifying diodes selected for their low forward voltage drop, 45 V reverse voltage rating and efficient SMT power package. Components L1 and C7 though C10 form the L-C output filter for the power conversion stage. In operation, a 0 V to +5 V pulse is provided to the PWM Input. The period of this pulse is equal to that of the target operating frequency and the pulse width is set according to: pw = (Vo/Vdd) * (Np/Ns) * T where T = 1/fs, Vo is the desired output voltage, Vdd is the input voltage to the converter’s output stage, Np is the number of primary turns on TP1 (6) and Ns is the number of secondary turns (2). Thus, for a 500 kHz conversion frequency, Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 14 Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability the pulse width is 707 ns for a 3.3 Vdc output voltage. This value is approximate and will have to be adjusted during operation, because this value does not include circuit losses (which increase as the load current increases.) CAUTION: NEVER let the duty cycle exceed 50% as the power transformer will saturate and immediately provide a high quality short-circuit between Vdd and ground, destroying transistors QD1 and QD2 if the power supply current is not sufficiently limited. Demonstration Circuit Performance Results The circuits shown in Figures 12 and 13 were evaluated for conversion efficiency over the load current range of 1 A to 10 A for comparison between the two topologies, and waveforms at the critical switching nodes were captured at 1 A and 10 A of load current for each topology. The gate drive waveform(s) were also captured to compare them to the simulation results. Demonstration Circuit Performance Results Figure 14 shows a comparison of the efficiency curves obtained for the RRFC and TTFC evaluation circuit converters. The circuits shown in Figures 12 and 13 were evaluated for conversion efficiency over the load current range of 1 A to 10TTFC A forConversion comparison between the two topologies, and waveforms at the critical Figure 14. STFC Versus Efficiency. switching nodes were captured at 1 A and 10 A of load current for each topology. The gate drive It canwaveform(s) be seen that there a slight difference in the efficiencies of the two converters, wereisalso captured to compare them to the simulation results.chiefly due to the losses in the primary side Schottky clamping rectifiers and the additional driver stage require for the TTFC converter. It should be noted that the key consideration in this comparison the differential efficiency the two topologies and Figure 14 shows a comparison of thewas efficiency curves inobtained forbetween the RRFC andconverter TTFC evaluation not maximizing the conversion efficiencies. An efficiency improvement of 5-8% may be realized utilizing synchronous circuit converters. rectification to replace the Schottky rectifiers in the secondary side. Further efficiency improvements may be realized by optimizing the primary reset/clamping scheme utilized for the RRFC. Figure 14. STFC Versus TTFC Conversion Efficiency. 84% 83% Conversion Efficiency 82% 81% 80% RRFC TTFC 79% 78% 77% 76% 75% 1 2 3 4 5 6 7 8 9 10 Load Current (Adc) It can be seen that there is a slight difference in the efficiencies of the two converters, chiefly due to the losses in the primary side Schottky clamping rectifiers and the additional driver stage require for the Microsemi Corporation in this comparison was the differential in TTFC converter. It should be noted that the key consideration One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 efficiency between the two converter topologies and not maximizing the conversion efficiencies. An 15 efficiency improvement of 5-8% may be realized utilizing synchronous rectification to replace the Schottky rectifiers in the secondary side. Further efficiency improvements may be realized by Applying MiGaNTM , GaN Devices in High Reliability and Space Applications for Maximum Performance and Reliability A key goal of this evaluation was to observe the differences in the drain voltage stresses presented by each topology. Accordingly, Figure 15 is the oscilloscope capture of the drain-source voltage of power switch OPS1 in Figure 12 for a load current of 1Adc, and Figure 16 is for a load current of 10 Adc. Figure 15. OPS1 Drain-Source Voltage, Iload = 1Adc. Figure 15. OPS1 Drain-Source Voltage, Iload = 1Adc. Figure 15. OPS1 Drain-Source Voltage, Iload = 1Adc. It is clear that the peak drain-source voltage during the resonant reset event is 52 Vdc. It is clear that the peak drain-source voltage during the resonant reset event is 52 Vdc. 16. OPS1 Drain-Source Voltage, Iload reset = 10 event Adc. is 52 Vdc. It is clear that theFigure peak drain-source voltage during the resonant Figure 16. OPS1 Drain-Source Voltage, Iload = 10 Adc. Figure 16. OPS1 Drain-Source Voltage, Iload = 10 Adc. Again, it is clear that the peak drain-source voltage during the resonant reset event is 88 Vdc. It was observed that load currents greater than 10 Adc caused the drain-source voltage to exceed 90 Vdc, which is considered the derating fire-wall for this circuit topology. Lower peak drain reset voltages may be obtained with different transformer designs and with different snubbing techniques. However, the goal of this evaluation was not optimization of Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 16 It was observed that load currents greater than 10 Adc caused the drain-source voltage to exceed 90 Vdc, which is considered the derating fire-wall for this circuit topology. Lower peak drain reset voltages may be obtained withTMdifferent transformer and with different snubbing techniques. However, the Applying MiGaN , GaN Devices in Highdesigns Reliability and for Maximum Performance and Reliability goalSpace of thisApplications evaluation was not optimization of performance but rather to demonstrate the fact that the drain-source voltage for the RRFC is truly unconstrained and must be controlled by the designer, and it varies according to a number of parameters including load current. performance but rather to demonstrate the fact that the drain-source voltage for the RRFC is truly unconstrained and must be controlled by the designer, and it varies according to a number of parameters including load current. The oscilloscope capture of the drain-source voltage of the power switches OPD1(yellow) and OPD2 (blue) in Figure capture 13 at 1 of A the of load current voltage is shown in Figure 17, and Figure 18 is for a load ofFigure 10 13 at The oscilloscope drain-source of the power switches OPD1(yellow) and OPD2current (blue) in 1Adc. A of load current is shown in Figure 17, and Figure 18 is for a load current of 10 Adc. Figure 17. OPD1 (yellow) Drain-Source Voltages, = 1 Adc. Voltages, Iload = 1 Adc. Figureand 17.OPD2 OPD1(blue) (yellow) and OPD2 (blue) Iload Drain-Source It can be seen that the drain-source voltage for either power switch in Figure 13 is limited to 33 Vdc. It can be seen that the drain-source voltage for either power switch in Figure 13 is limited to 33 Vdc. Figure 18. OPD1 (yellow) and OPD2 (blue) Drain-Source Voltages, Iload = 10 Adc. Figure 18. OPD1 (yellow) and OPD2 (blue) Drain-Source Voltages, Iload = 10 Adc. Once again, that thethe maximum drain-source voltage for either Figurein 13Figure is limited Once again,ititisisobvious obvious that maximum drain-source voltage for power either switch powerinswitch 13 tois 36 Vdc. The small voltage spikes and ringing observed are due to the lead inductances of the Schottky catch rectifiers in the prilimited to 36 Vdc. The small voltage spikes and ringing observed are due to the lead inductances of the mary side of the circuit. These could be reduced or eliminated if leadless, SMT packaged devices were available for these Schottky catch rectifiers in the primary side of the circuit. These could be reduced or eliminated if components. leadless, SMT packaged devices were available for these components. Thus, the drain-source voltage stress for each Microsemi power transistor in the TTFC is truly constrained. As was Corporation mentioned topology provides a tacitSales.Support@microsemi.com insurance policy for the designer so long as theRev. duty One Enterprise,previously, Aliso Viejo, CAthis 92656 Ph: 949-380-6100 www.microsemi.com 1.0 Nov 2013 cycle limitation of less than 50%, the additional complexity and the slight decrease in conversion 17 efficiency are tolerable in the application. Schottky catch rectifiers in the primary side of the circuit. These could be reduced or eliminated if leadless, SMT packaged devices were available for these components. Applying MiGaNTM , GaN Devices in High Reliability and Space Applications voltage for Maximum andtransistor Reliability Thus, the drain-source stress Performance for each power in the TTFC is truly constrained. As was mentioned previously, this topology provides a tacit insurance policy for the designer so long as the duty cyclethe limitation of less thanstress 50%, for theeach additional complexity andTTFC the slight in conversion Thus, drain-source voltage power transistor in the is trulydecrease constrained. As was mentioned previefficiency are tolerable inathe ously, this topology provides tacitapplication. insurance policy for the designer so long as the duty cycle limitation of less than 50%, the additional complexity and the slight decrease in conversion efficiency are tolerable in the application. Finally, an oscilloscope capture of the gate drive waveform obtained from the evaluation circuit is Finally, capture of the drive waveform obtained from theinevaluation is shown Figure shownaninoscilloscope Figure 19. The three gategate drive signals are nearly identical amplitudecircuit and shape, soinonly one19. The three gate drive signals are nearly identical in amplitude and shape, so only one is shown for the purposes of analysis. is shown for the purposes of analysis. This trace is included in this discussion for the purpose of its This trace is included in this discussion for the purpose of its comparison to the simulated waveform shown in Figure 11. comparison to the simulated waveform shown in Figure 11. Figure 19. HEMT Gate Drive Voltage Waveform. Figure 19. HEMT Gate Drive Voltage Waveform. The amplitude and general wave shape are in general agreement with the simulation results shown in Figure 11. However, the actual circuit’s rise time is slightly longer than that of the simulation at approximately 40 ns versus 30 ns – a difference accounted for by the accuracy of the PSPICE model of the 2N2369A devices. However, it should be noted that the actual circuit wave form shows no overshoot or inductive ringing present, and the rise and fall of the gate voltage is dominated solely by an R-C response. The presence of the 1 W damping resistor in the high side drive for each individual driver helps contribute to this basic wave shape. In the end, the “cleanliness” of this wave shape is the benefit to the designer that the U4A package with the separate gate drive source return, as well as careful layout, can provide to the designer utilizing the GaN HEMTs in this package. Conclusion Because of their excellent performance GaN HEMTs are the power switch technology of the future for many power conversion applications. In addition to being a dependable, rad-hard device, if the devices are properly housed and provisioned with I/O pins, and furthermore they are carefully applied, they provide a reliable and high performance upgrade to conventional silicon MOSFETs in high-reliability and space applications. MiGaNTM GaN devices and the application note addresses all the key concerns of the GaN HEMT technologies and also these devices are taken through the Microsemi’s internal high reliability qualification levels (MHQLTM) that offer higher reliability. Microsemi Corporation One Enterprise, Aliso Viejo, CA 92656 Ph: 949-380-6100 Sales.Support@microsemi.com www.microsemi.com Rev. 1.0 Nov 2013 18