Using Highly Integrated RF ICs to Optimize your High Performance

advertisement

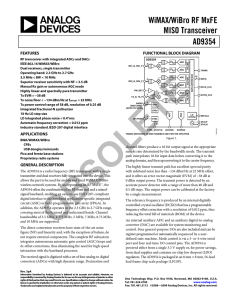

Th W The World ld LLeader d iin Hi High-Performance hP f Si Signall Processing P i Solutions S l ti Using Highly Integrated RF ICs to Optimize your High Performance Radio Designs The Integration Dilemma Example: RF Amplifier Internal vs. Ext Matching ADL5324 - KEY SPECIFICATIONS Frequency Range: 400 - 4000 MHz Gain: 14 dB @ 2140 MHz P1dB: 28.9 dBm @ 2140 MHz OIP3: 44 dBm @ 2140 MHz Noise Figure: 3.5 dB @ 2140 MHz Power Supply: 3.3/5 V Low Quiescent Current: 60/135 mA P k Package: SOT SOT-89 89 ESD Rating: ±1 kV (Class 1C) FEATURES Minimal External Matching Components On-Chip Active Bias Temperature p and Frequency q y Stable External Matching Components Driver Amplifiers vs. Gain Blocks RF Amplifiers ADL5324 Driver Amplifier with External Tuning 3 ADL5541 Internally Matched Gain Block Driver Amplifiers vs. Gain Blocks Part No. Description Freq (MHz) ADL5320 ADL5324 ADL5542 ADL5601 ADL5602 1/4 W Driver 1/2 W Driver RF/IF Gain Block RF/IF Gain Block RF/IF Gain Block 400 - 2700 400 – 4000 50 - 6000 50 - 4000 50 - 4000 4 Gain OP1dB OIP3 NF (dB) (dBm) (dBm) (dB) 13.2 14 18.7 15.3 19.5 25.7 28.9 18.3 19.0 19.3 42.0 44 39.0 43.0 42.0 4.4 3.5 3.2 3.7 3.3 Specs @ (MHz) VS (V) ISY (mA) Package 2140 2140 2000 900 2000 5 3/5 5 5 5 104 60/135 93 83 89 SOT-89 SOT-89 3x3 mm SOT-89 SOT-89 NC VPOS MNLG MNLE MNOP COMM MNON VPOS MNGM System on a Chip vs. Discrete Components MNIN LOI2 MNCT VGS2 COMM VGS1 VPOS VGS0 COMM LOSW VPOS PWDN VPOS COMM ADL5358 DVCT COMM NC N DVL LG VPO OS DVL LE DVO ON DVO OP COM MM DVG GM VPO OS 07885-0 001 LOI1 DVIN Single Chip Transceivers are Small and Convenient to use. Discrete RF Components tend to have Higher Performance and More Flexibility Is there a Happy Medium? 5 Size Matters! VCO TYP 10mm x10mm SAW 211 MHz) 7mm x 5mm x 1.33 mm Phase Locked Loop w. Integrated PLL 5mm x 5mm IQ Mod/IQ Demod/Mixer TYP 4x4mm to 6x6mm 6 Mixer w. Integrated PLL/VCO 6x6mm SOT-89 Driver Amp With External E t l matching t hi 15mm x 4 mm A Discrete Wireless Transmitter Band Pass Filter LNA LNA IMAGE REJECT FILTER IF SAMPLING ADC ADC DRIVER Rx MIXER FPGA A C ADC Anti-Alias filter VCO Pusle Shaping Filters PLL PLL REF CLOCK CLOCK DISTRIBUTION DAC 90o DAC 7 ADC IQ Modulator FEC MAC BB Interface RF AMP VVA/DSA RF DETECTOR Sample Rate Conversion 0o HPA DUC DDC Dual DAC Integrating g g Horizontally y in the Signal g Chain Band Pass Filter LNA LNA IMAGE REJECT FILTER IF SAMPLING ADC ADC DRIVER Rx MIXER FPGA A C ADC Anti-Alias filter VCO Pusle Shaping Filters PLL PLL REF CLOCK CLOCK DISTRIBUTION DAC 90o DAC 8 ADC IQ Modulator FEC MAC BB Interface RF AMP VVA/DSA RF DETECTOR Sample Rate Conversion 0o HPA DUC DDC Dual DAC Diversity Receivers suggest Integrating Vertically Band Pass Filter LNA LNA IMAGE REJECT FILTER Rx MIXER IF SAMPLING ADC ADC DRIVER FPGA ADC A C ADC Anti-Alias filter VCO Pusle Shaping Filters PLL REF CLOCK CLOCK DISTRIBUTION DUC DDC Sample Rate Conversion FEC MAC BB Interface 9 IC Process Technology – A Barrier to Integration? Band Pass Filter LNA LNA IMAGE REJECT FILTER IF SAMPLING ADC ADC DRIVER Rx MIXER FPGA A C ADC Anti-Alias filter VCO Pusle Shaping Filters PLL PLL REF CLOCK CLOCK DISTRIBUTION DAC 90o DAC SAW or Discrete LC 10 LDMOS GaAs Dual DAC IQ Modulator ADC FEC MAC BB Interface RF AMP VVA/DSA RF DETECTOR Sample Rate Conversion 0o HPA DUC DDC BJT CMOS IC Process Technology – A Barrier to Integration? Band Pass Filter LNA LNA IMAGE REJECT FILTER IF SAMPLING ADC ADC DRIVER Rx MIXER FPGA A C ADC Anti-Alias filter VCO Pusle Shaping Filters PLL PLL REF CLOCK CLOCK DISTRIBUTION DAC 90o DAC SAW or Discrete LC 11 IQ Modulator ADC LDMOS GaAs FEC MAC BB Interface RF AMP VVA/DSA RF DETECTOR Sample Rate Conversion 0o HPA DUC DDC Dual DAC BiCMOS CMOS Synthesizer y and Clock Integration g Options p Band Pass Filter LNA LNA IMAGE REJECT FILTER IF SAMPLING ADC ADC DRIVER Rx MIXER FPGA A C ADC Anti-Alias filter VCO Pusle Shaping Filters PLL PLL REF CLOCK CLOCK DISTRIBUTION DAC 90o DAC 12 ADC IQ Modulator FEC MAC BB Interface RF AMP VVA/DSA RF DETECTOR Sample Rate Conversion 0o HPA DUC DDC Dual DAC Working Towards Integration of VCOs with PLLs PLL Challenge VCO PLL VCO is to integrate VCO with PLL while maintaining good VCO p phase noise 13 Integrated PLL/VCO Phase Noise Comparison (@2.2 GHz) -60 -70 ADF4360-2 Int-N PLL with Integrated NB VCO Phas se Noise (dB Bc/Hz) -80 ADF4350 Frac-N PLL with Integrated Broadband VCO ADRF6702 IQ Mod w Integrated NB PLL-VCO -90 ADF4351 Frac-N PLL with Integrated Broadband VCO -100 -110 -120 -130 -140 -150 -160 10 100 1000 Frequency Offset (kHz) 14 10000 ADF4351 – Ultra Wideband PLL with integrated low-noise VCO KEY SPECIFICATIONS Output frequency range: 35MHz to 4 4GHz 4.4GHz Programmable Output divide-by1/2/4/8/ 16/32 or 64 3.0 V to 3.6 V power supply Programmable dual-modulus prescaler 4/5, 8/9, 16/17 Programmable output power level Improved EVM (0.4% @ 2.1GHz) FEATURES Output p Low Phase Noise VCO 1.8 V logic compatibility Integer-N or Fractional-N operation RF output mute function 3-wire serial interface Analog and digital lock detect Hardware and software power-down mode Fastlock Mode Pin and Function Compatible with ADF4350 ADF4351 - Broadband Operation Using an Octave VCO and Dividers VCO bank provides one octave of tuning range Operation from 4.4 GHz down to 35 MHz is achieved using a divider array. Device Size = 5 mm x 5 mm Main external components are power supply decoupling and loop filter 16 CN0245 - Wideband PLL Synthesizer with Simple I t f Interface t Q to Quadrature d t D Demodulators d l t Broadband PLL-to-IQ Demodulator Interface Circuit ADF4350: Wideband Synthesizer with Integrated high-performance VCO Low Frequency q y Interface Using g ADL5387 2XLO IQ Demodulator Operating frequency: 50 MHz – 2 GHz High Frequency Interface Using ADL5380 1XLO IQ Demodulator Operating O ti frequency: f 400MHz–4.4 400MH 4 4 GHz Polyphase quadrature architecture Provides recommended LO harmonic filtering components to ensure excellent quadrature accuracy 17 ADF5001 18GHz, divide-by-4 Prescaler KEY SPECIFICATIONS 4GHz – 18GHz Range Divide by y4 -10dBm to +10dBm input power range Output power -5dBm Phase Noise @100kHz offset: 150dBc/Hz Low Power: 30mA @ 3.3V : 7mA in PD mode FEATURES Matched 50 ohm single ended RF input Differential output to match to ADF4106/7/8 Ultra wide bandwidth Single 3.3V 3 3V supply 16-LFCSP (3mm x 3mm) PLL 1-4.5 GHz ADF5001 4 HighFreq Ext. VCO 4-18 GHz ADF41020 – 18GHz Integer-N PLL AVDD KEY SPECIFICATIONS RF input to 18GHz Programmable dual mod prescaler 104MHz PFD maximum frequency Normalised PN Floor = -221 dBc/Hz Integer-N operation 2.7-3.3V operation DVDD VP RSET CPGND REFERENCE R COUNTER REFIN PHASE FREQUENCY DETECTOR R COUNTER LATCH CLK DATA LE 24-BIT 24 BIT INPUT REGISTER CHARGE PUMP LOCK DETECT FUNCTION LATCH A, B COUNTER LATCH CP CURRENT SETTING 1 CURRENT SETTING 2 CPI3 CPI2 CPI1 CPI6 CPI5 CPI4 HIGH Z AVDD MUXOUT MUX N = 4.(BP + A) 3pF RFIN FEATURES Software compatible with ADF4106/7/8 integer-N PLLs Programmable charge pump currents Analog and Digital Lock detect Hardware and Software Power-Down 20-LFCSP 20 LFCSP (4mm x 4mm) 19 DIVIDE BY 4 SDOUT P/P+ 1 A&B COUNTERS M3 M2 M1 50Ω ADF41020 AGND CE DGND ADF5001 Core The World Leader in High-Performance Signal Processing Solutions Rx Signal Chain Evolution 20 Diversity IF Sampling Signal Chain - Circa 2009 Clock Generation and Distribution ADL5521 ADF9516/7 Image ADL5523 reject ADC SAW ADF4153 PLL AD6655 AD6657 ADL5521 SAW ADC ADL5523 2121 ADL5354 ADL5356 ADL5358 ADL5802 AD8376 FPGA Diversity IF Sampling Signal Chain Evolution 2012 ADL5811 ADL5523 ADL5240 ADL5202 Separated RF paths for Isolation AD9643 AD6649 ADL5811 ADL5523 Discrete pHEMT f best for b t NF with ith lesser ESD performance ADL5240 Duals D l available il bl b butt singles often used for isolation Frac-N PLL ADF4350 AD9523/23 Clock Distribution ADL5811 & ADL5812 – Wideband Passive Mixers Key Specifications RF Frequency: 700 MHz to 2800 MHz Input IP3: +27.5 dBm; IIP2: +62 dBm Input I t P1dB: P1dB +12.7 +12 7 dBm dB Noise Figure @ 2 GHz: 10.7 dB IF Frequency: 30 MHz to 450 MHz Power conversion gain: +7.5 7.5 dB LO drive level: 0 dBm Single supply operation: 3.6 V to 5 V Features Single-ended 50 Ohm RF and LO input Programmable via Serial Port Interface Tunable RF balun and IF filter Bias adjust for IIP3 and NF trade-off Individual channel power down control Robust ESD protection circuitry Small LFCSP footprint ADL5811: 32 lead 5 mm x 5 mm LFCSP ADL5812: 40 lead 6 mm x 6 mm LFCSP 23 Dual Devices Save Space but be Aware of Channel-to-Channel RF and IF Coupling 24 ADRF6601/2/3/4 Mixer Integration with PLL and VCO Mixer, VCO & PLL Requires a Family of Devices for Broadband Frequency Coverage VDD Integrated 750 – 1160 MHz (ADRF6601) 1550 – 2150 MHz (ADRF6602) 2100 – 2600 MHz (ADRF6603) 2500 – 2900 MHz (ADRF6604) Noise: -150dBc/Hz at 5MHz 40-Lead LFCSP (6mm x 6mm) 1 VDD VDD 10 17 22 VDD VDD NC NC 27 34 32 33 ADRF6602 Internal LO Range 1550MHz to 2150MHz LOSEL 36 LON 37 BUFFER LOP 38 BUFFER PL EN 16 DATA 12 SPI INTERFACE CLK 13 LE 14 x2 MODULUS FRACTION REG THIRD ORDER FRACTIONAL INTERPOLATOR REFIN 6 MUX PLL – :2 :4 + TEMP SENSOR INTEGER REG PRESCALER N COUNTER 21 to 123 PHASE FREQUENCY DETECTOR 2:1 MUX :2 DIV BY 2,1 7 VCO CORE 3100-4300 MHz GND 5 RSET 2 DECL3P3 2P5V LDO 9 DECL2P5 VCO LDO 40 DECLVCO 26 RFIN 29 IP3SET CHARGE PUMP 250 uA 500 uA(default) 750 uA 1000 uA 11 15 20 21 23 24 25 28 30 31 35 3P3V LDO + MUXOUT 8 4 25 VDD 3 39 18 19 CP VTUNE PBB NBB ADL5201/2 Single and Dual 31.5dB Gain Range Digitally Programmable VGA KEY SPECIFICATIONS -11.5 to 20dB Gain Range 0.5dB Step Size 150-Ohm Differential Input/Output 6.8 dB NF at 200 MHz (max gain) 50 dBm OIP3 at 200 MHz 24-Lead Frame CSP 4x4mm Package FEATURES Wide Input Dynamic Range for Multi-carrier A li ti Applications Flexible Control Interface (Parallel, SPI, Up/Down) Power Down and Low Power Bias Modes AD6649 IF Diversity y Receiver FDA DRVDD THRESHOLD DETECT I AD6649 SELECTABLE FIR FILTER VIN+A DIGITAL INTERLEAVING ADC VIN–A Q DC CORRECTION REFERENCE SELECTABLE FIR FILTER fS/4 NCO 32-BIT TUNING NCO DC CORRECTION Q VIN–B SELECTABLE FIR FILTER I FDB D0+/D0– DCO GENERATION DCO+ DCO– SYNC PROGRAMMING DATA SELECTABLE FIR FILTER THRESHOLD DETECT AGND D13+/D13 D13+/D13– CLK– MULTICHIP SYNC ADC VIN+B OR– CLK+ DIVIDE 1 TO 8 DUTY CYCLE STABILIZER OR+ SPI PDWN OEB SDIO SCLK CSB 09635-001 AVDD DDR L LVDS OUTPUT BUFFER Features: Integrated wideband digital down converter t (DDC): (DDC) SNR = 73 dBFs in a 95MHz bandwidth at 185 MHz @ 250 MSPS 1.8V analog g and LVDS supply pp y operation p Integrated dual-channel ADC: IF sampling frequencies to 400 MHz Flexible analog input: 1.4 V p-p to 2.1 V p-p range 32-bit complex NCO FIR Filters with 2 modes Amplitude detect bits for efficient AGC implementation AD9253 – Quad,, 14-Bit,, 80/105/125 MSPS Serial LVDS 1.8 V A/D Converter KEY BENEFITS 4 ADCs integrated into 1 package 115 mW W ADC power/channel / h l att 125 with scalable power options SNR = 73 dBFs (to Nyquist) ENOB = 12 bits SFDR = 88 dBc (to Nyquist) Excellent linearity MSPS DNL = ±0.75 LSB (typical) INL = ±2.0 LSB (typical) Serial LVDS (ANSI-644, default) Low power, reduced signal g option (similar ( tto IEEE 1596 1596.3) 3) Data and frame clock outputs 650 MHz full-power analog bandwidth 2 V p-p input voltage range 1.8 V supply pp y operation p Serial port control Full-chip and individual-channel power-down modes Flexible bit orientation Built-in and custom digital test pattern generation Programmable clock and data alignment Programmable output resolution 28 ADF4002 – Optimized p for ADC Clocking g AVDD KEY SPECIFICATIONS Bandwidth: 5 – 400 MHz Phase Noise: -110 dBc/Hz at 400 MHz, 1 MHz PFD Frequency. Normalized Phase Noise: -222 dBc/Hz Package: 4x4mm 20-LFCSP, 16-TSSOP DVDD VP RSET CPGND REFERENCE 14-BIT R COUNTER REFIN RF PHASE FREQUENCY DETECTOR CHARGE PUMP CP 14 R COUNTER LATCH CLK DATA LE 24-BIT INPUT REGISTER 22 FUNCTION LATCH N COUNTER LATCH SDOUT LOCK DETECT CURRENT SETTING 1 CURRENT SETTING 2 CPI3 CPI2 CPI1 CPI6 CPI5 CPI4 HIGH Z AVDD MUXOUT MUX SDOUT RFINA RFINB 13-BIT N COUNTER M3 M2 M1 CE FEATURES Programmable Charge Pump Currents Analog & Digital Lock Detect Programmable Prescaler Values Low Division Ratios Permitted Hardware and Software Compatible p to ADF4001 Enhanced Product Qualification (EP) Available 29 AGND DGND 06052-001 ADF4002 AD9523-1 Low Jitter Clock Generator and Distributor –80 1: 2: 3: 4: 5: 6: 7: –90 –110 110 –120 1 –130 2 –140 3 –150 –160 –170 7 4 NOISE: ANALYSIS RANGE x: START 10kHz TO STOP 40MHz INTG NOISE: –81.0dBc/40MHz RMS NOISE: 126.6µRAD 7.3mdeg RMS JITTER: 164.0fsec RESIDUAL FM: 1.7kHz –180 180 100 1k 10k 100k FREQUENCY (Hz) 1M 5 10M Absolute p phase noise 122.88 MHz out 30 6 09278-014 PHA ASE NOISE (dBc/H Hz) –100 1kHz, –123.1dBc/Hz 10kHz, –133.8dBc/Hz 100kHz, –140.5dBc/Hz 1MHz, –149.0Bc/Hz 10MHz, –161.5dBc/Hz 40MHz, –162.1dBc/Hz 800kHz, –146.9dBc/Hz Direct Conversion Rx architecture ADL5380 AD9251/31 AD9253/AD9633* AD9269AD9649/AD6659 ADC LNA AMP 90 Phase Shifter AD8366 ADA4937 /38 Main RX ADL5521 ADL5602 ADC ADF4350 31 Clock Generation and Distribution AD951X AD9523/24* FPGA Space Comparison between IF Sampling Rx and ZIF Diversity IF Sampling Rx Diversity ZIF Receiver IF Sampling signal chains typically require two filters after mixer SAW at Mixer Output for Channel Selection Anti-Aliasing Filter between ADC Driver and ADC ZIF Receiver only requires one filter after mixer Baseband Anti-Aliasing and Channel Selection Filter 32 A Typical IF Sampling Receiver 33 A Typical Direct Conversion Receiver 34 ADL5380 400MHz – 6GHz Quadrature Demod KEY SPECIFICATIONS Frequency Range: 400MHz to 6GHz Wide LO O input range -10 to +5dBm IIP3 +28 dBm, IIP2 +60dBm @ 2600MHz Input P1dB +12dBm @ 2600MHz NF 13 dB @ 2500MHz Voltage Conversion Gain 4dB Quadrature demodulation accuracy Phase accuracy <0.5° Amplitude balance <0.1 <0 1 dB Demodulation bandwidth 500 MHz Package 24-LFCSP FEATURES I/Q demodulator Programmable power consumption 35 ADRF6850 100MHz–1 GHz PLL/IQ Demod KEY SPECIFICATIONS Freq Range: 100 MHz-1000 MHz PLL Frequency Increment: <1 Hz PLL/VCO Phase Noise at 1 GHz -98dBc/Hz @ 10 KHz Offset RF VGA Gain Control Range: 60 dB Input P1dB: +12 dBm at 0 dB gain Input IP3: +22.5 dBm at 0 dB gain Noise figure: 11 dB at >39 39 dB gain, 49 dB at 0 dB gain BB Bandwidth (1 dB): 250 MHz in wideband mode, 50 MHz MH in narrow-band narro band mode Power supply: +3.3 V/350 mA 36 FEATURES I/Q Demodulator High Hi h Modulus M d l Frac-N F N PLL Integrated VCO 60 dB Voltage-Controlled VGA SPI/I2C Serial Interface Package: 8x8 LFCSP-56 Integration of BB VGA and Filter for ZIF Receive FEATURES -5 to 45 dB linear-in-dB gain range 3/6 dB Pre-Amp Pre Amp gain switch 1 to 31 MHz tunable filter in 1MHz steps SPI Programmable 6-pole Butterworth LPF w/ calibration 900mV to 1.5V 1 5V output common common-mode mode Excellent Gain & Group Delay Matching DC-offset compensation loop SPI Programmable 3 3V Supply 3.3V 5mm x 5mm LFCSP-32 40 35 30 20 15 10 5 0 –5 –10 1 10 FREQUENCY (MHz) 100 09422-012 GAIN (dB) 25 The World Leader in High-Performance Signal Processing Solutions Tx Signal Chain Evolution 38 A Zero IF Transmitter – Where do we Integrate? FPGA Pusle Shaping Filters PLL-VCO REF CLOCK CLOCK DIST. DAC 90o DAC 39 ADC IQ Modulator FEC MAC BB Interface RF AMP VVA/DSA RF DETECTOR Sample Rate Conversion 0o HPA DUC DDC Dual DAC AD9122 Dual LVDS I/F TxDAC+® KEY FEATURES 16b Dual DAC, based upon AD9779A Word, Byte & Nibble data load capability 1.2 GSPS DAC Update Rate Single port LVDS input Selectable 2X/4X/8X Halfband Interpolation filters NCO for exact carrier placement Channel matching control for optimal LO/SSB cancellation Phase compensation, in addition to gain and offset compensation Multiple chip synchronization interface Configurable clock multiplier/divider Digital inverse sinc filter Features and performance optimized g for direct conversion and IF sampling di diversity it Key Benefits 32 bit NCO for carrier placement flexibility Source synchronous LVDS Small 10x10mm LFCSP package Improved digital architecture for reduced power consumption AD9148 - Industry 1st High Performance Integrated QUAD DAC KEY FEATURES 16b QUAD DAC, based upon AD9122 1.0 GSPS DAC Update Rate Single or Dual Port LVDS Inputs Selectable 2X/4X/8X Halfband Interpolation filters 32b NCO for exact carrier placement flexibility Multiple p chip p synchronization y interface Configurable Clock Multiplier/Divider Channel Matching control for optimal LO/SSB cancellation Gain and Offset control through SPI Digital inverse sinc filter Features and performance optimized for direct conversion and IF sampling diversity Key Benefits Highly Integrated, Multi-DAC synchronization 32b NCO for exact carrier placement flexibility ADL5375 Multi Standard Broadband IQ Modulator KEY SPECIFICATIONS 9.4 dBm from 450 MHz to 4 GHz O OIP3: 3 ≥ +22 dBm d from o 450 50 MHz to 4 GHz G WCDMA ACPR: -72.5 dBc @ -10 dBm Pout Noise Floor -160 dBm/Hz @ 1.9 GHz LO Leakage: -40 dBm to 2 GHz SB Suppression: -40 40 dBc to 4 GHz 0 dBm LO Drive – Single Ended Output Return Loss 15 dB from 500 MHz to 5.5 GHz P1dB: FEATURES Matched 50 ohm RF output & LO Input 0.5 V or 1.5 dc baseband bias level Output Disable Pin LFCSP-24 (4mm x 4mm) Enhanced E h d Product P d t Qualification Q lifi ti (EP) Available 42 450 MHz – 6GHz ADRF6755 Broad Band Quad Modulator and DSA with Integrated Fractional Fractional-N N PLL and VCO KEY SPECIFICATIONS Freq Range: 300 MHz to 2310MHz Gain G i Control C t l Range: R 47dB Gain Step: 1dB OIP3: +21 dBm OP1dB: +8 dBm Modulator Noise Floor: -162 162 dBm/Hz PLL Phase Noise: -100 dBc/Hz @ 10 KHz Baseband BW: 250 MHz (-1 dB) Frequency Increment: 1 Hz Power Supply: +5 V/350 mA FEATURES IQ Modulator with Integrated Fractional-N PLL/VCO and 47 dB DSA SPI/I2C Serial Interface Functions with External VCO ADL5243 100-4000MHz Digital VGA KEY SPECIFICATIONS 31.5dB Range Digital Step Attenuator 0.5dB Step Size with 6-bit control 50-Ohm Single-Ended Input/Output Low-Noise Pre-Amp Stage 19.5dB Gain at 2GHz 3.3dB NF at 2GHz 19dBm OP1dB at 2GHz High Linearity Output Driver Stage 14dB Gain at 2GHz 26 5dB OP1dB 26.5dBm 41dBm OIP3 FEATURES Single monolithic GaAs die Combines AMP1 + DSA + AMP2 Flexible Control Interface (Parallel or Serial SPI) Independent I d d t Low-Noise L N i High Hi h Linearity Li it Driver Di Amp A 32-Lead Frame CSP 5x5mm Package 44 ADL5386 IQ Modulator & VVA & RF Detector KEY SPECIFICATIONS (350MHz) 50MHz to 2200MHz operation Baseband Bandwidth: 700 MHz P1dB: P1dB 11dBm 11dB OIP3: 25dBm Noise Floor: -160dBm/Hz LO/SB Suppression: -38dBm/-46 dBc VVA: 26 dB Range, 2.2 dB Insertion Loss Log Detector: 26 dB Detection Range FEATURES TxDAC Compatible Baseband Inputs 2X LO AGC LOOP with Voltage Set Point Integrated GaAs VVA Integrated Log Detector Integrated Stand-Alone Temp Sensor 4.6 mV/degC Single +5V supply 230mA ADL5386 Pout vs Setpoint in AGC Mode Temperature-Stable Linear-in-dB Operation over a wide output power range ZIF/CIF with Integrated g IQ Mod/PLL/VCO FPGA Image reject filter ADL5365 IF=112MHz ADC Anti-Alias AD9434 filter 12-bit, 368.64Msps ATT=2dB High side LO LO=RF+IF = 2252MHz Synth Ref FEC RMS detector 0o PA 90o DAC DAC IF=112MHz RF VGA TxMOD IQ Modulator + Frac-N Frac N PLL 47 DUC DDC Sample Rate Conversion AD9516-4 AD836x Pusle Shape Filters AD9122 MAC BB Interface ADRF6701/2/3/4 I/Q Modulator + Synthesizer Family FEATURES Broadband Operation p via a family y of pin-compatible devices 750 – 1100 MHz (ADRF6701) 1550 – 2150 MHz (ADRF6702) 2100 – 2600 MHz (ADRF6703) 2500 – 2900 MHz (ADRF6704) Phase Noise Performance similar to performance of stand-alone broadband PLL/VCO 40-Lead LFCSP (6mm x 6mm) IQ Modulator FRAC-N PLL Narrowband VCO 48 AD9739 - TxDAC® with MixModeTM Direct RF Synthesis KEY FEATURES SDI SDO CSB SCLK DATACLK_OUT0+ DATACLK_OUT0– DATACLK_OUT1+ DATACLK_OUT1– DATACLK_IN0+ DATACLK_IN0– DB0[13:0]+ DB0[13 0] DB0[13:0]– DATACLK_IN1+ DATACLK_IN1– DB1[13:0]+ DB1[13:0]– SPI CLOCK DISTRIBUTION SYNCHRONIZE ER DACCLK– DACCLK+ RESET LVDS LVDS DRIVER DRIVER R LV VDS RECEIVER 14b 2.5 GSPS DAC update rate Dual p port LVDS input p DOCSIS 3.0 ACLR: Eight QAM Carriers 72dBc @ 90 MHz IF 68.5dBc 68 5dB @ 920 MH MHz IF MixModeTM allows 2nd & 3rd Nyquist Band Direct RF Dual Port LVDS data interface with on-chip 100Ω termination Built-in self test Power dissipation = 1.1 W (max), 700 mW (typical) Programmable full-scale output current Data input sampling controller Pin comparable to AD9736 LVDS RECEIVER 14-, 12-, 10-BIT DAC CORE BAND GAP REFERENCE CURRENT SPI VREF Key y Benefits Wide Bandwidth, Direct RF I120 SPI IOUTA IOUTB AD9739 ACLR Performance Traditional vs. MixModeTM Architecture Traditional Architecture MixModeTM Architecture AD9779 + ADL5372 2GHz FMOD AD9739 in MixModeTM RFout = 2.10GHz Channel Power = -9.4dBm ACLR @ 5MHz = -74.3dBc -74 3dBc ACLR @ 10MHz = -75.8dBc ACLR @ 15MHz = -75.9dBc RFout = 2.10GHz Channel Power = -19.3dBm ACLR @ 5MHz = -71.8dBc -71 8dBc ACLR @ 10MHz = -74.8dBc ACLR @ 15MHz = -75.2dBc Multi-Stage g Up p and Down Conversion IQ DEMODULATOR Band Pass LNA Filter IMAGE Rx REJECT FILTER MIXER FPGA ADC AMP 90 Phase Shifter BB VGA & LPF ADC VCO VCO PLL PLL PLL PLL DUC DDC Sample Rate Conversion CLOCK DIST 51 DAC DAC 90o Tx MIXER RF DETECTOR FEC 0o HPA ADC VVA/DSA IQ MODULATOR Pusle Shaping Filters DUAL DAC MAC BB Interface ADRF6655 UP/Down Converter + Synthesizer KEY SPECIFICATIONS (900Mz) Input Freq Range: 100 MHz to 2500 MHz Output Freq Range: DC to 2200 MHz Mixer Input IP3: +29dBm Mixer Input P1dB: +12dBm Voltage Conversion Gain: +6dB Noise Figure: 12dB PLL Noise: -150dBc/Hz at 10MHz FEATURES Broadband Mixer for Transmit or Receive Integrated VCO & PLL Optional p External LO Input p 40-Lead LFCSP (6mm x 6mm) ADRF6806 Quadrature Demodulator w/ Synth-VCO KEY SPECIFICATIONS (LPEN=0) Quadrature Demodulator w/ Synthesizer Frequency Range: 50 to 525 MHz 1 dB Voltage Conversion Gain IP1dB: 12.2 dam IIP3: 28.5 dBm DSB NF: 12 12.2 2 dB Quadrature Demodulation Accuracy: Phase Accuracy: <0.5° Amplitude Accuracy: <0.1 dB IQ Bandwidth: 170 MHz (3 dB) FEATURES Integrated Synthesizer & VCO Auxilliary LO Output w/ Dividers SPI Programmable 40-Lead LFCSP (5mm x 5mm) 53 AD9963/61 Next-Generation MxFE® Rx TXCLK TXIQ/TXRXB TXD(11:0) 2/4/8 12 Bit DAC TXIP TXIN 2/4/8 12Bit DAC TXQP TXQN 2 12Bit ADC RXIP RXIN 2 12Bit ADC RXQP RXQN DATA Assembler TRXCLK TRXIQ TRXD(11:0) RESET SDIO SCLK CSB Serial Port Logic Referencesand Bias AUXIO2 AUXIO3 Aux DAC DAC12A Aux DAC DAC12B LDO VREGs LDOMO ODE Dual 12/10b, 130 MSPS DACs with programmable full-scale output current 2x and 4x interpolation filters Low Power 5 channels of analog auxiliary I/O Flexible I/O data interface to support interleaved and noninterleaved data transfers Mux Aux DAC RXB BIAS Tx CLKP CLKN AUXIN1 Aux DAC RXC CML DLL & Clock Distrib. TXC CML Dual 12/10b, 100 MSPS ADCs Low-Pass 2x decimation filters DLLFILT RE EFIO Internal Aux ADC AUXREF Th W The World ld LLeader d iin Hi High-Performance hP f Si Signall Processing P i Solutions S l ti Using Highly Integrated RF ICs to Optimize your High Performance Radio Designs