A Fractional-N Frequency Synthesizer for Cellular and Short Range

advertisement

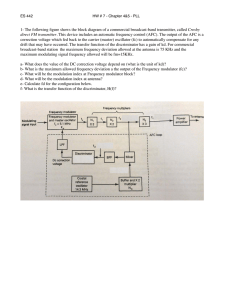

A Fractional-N Frequency Synthesizer for Cellular and Short Range Multi-standard Wireless Receiver Deping Huang1, Jin Zhou1, Wei Li1, Ning Li1, Junyan Ren1,2, Member IEEE 1. State Key Laboratory of ASIC & System, Fudan University 2. Micro-/Nano-Electronics Science and Technology Innovation Platform, Fudan University Shanghai 200433, China Email: w-li@fudan.edu.cn Abstract—This paper presents a Sigma-Delta fractional-N frequency synthesizer for multi-standard receiver. The synthesizer’s output range is 1.8~5.8GHz and covers the standards of DCS1800, WCDMA, TD-SCDMA, WLAN802.11a/b/g and Bluetooth. Frequency planning is elaborately done to make sure the synthesizer meets specifications of standards mentioned above. QVCO with a proposed phase shifter is shown to have better phase noise performance and more stable oscillation. Simulated phase noise is -119dBc/Hz at 1-MHz offset from a 4.2GHz carrier. Its FOM ranges from 181 to 187. The frequency synthesizer is fabricated in TSMC 0.13μm CMOS process. Average power consumption is 55.92mW. I. INTRODUCTION One trend of wireless communication today is integration of multiple communication standards into one chip. The increasing availability of multi-mode cellular systems in the market just illustrates this trend. Multi-standard radio, built in a low-cost CMOS technology, has recently gained a lot of interest. Simply inserting a new standalone radio into a mobile handset for each communication standard is definitely infeasible since the power and hardware consumption is unaffordable to any mobile system. What we need is a flexible multi-standard radio system which is characteristic of high reconfigurability and adaptability. One challenge for this system is the design of a frequency synthesizer that is able to generate clean and stable LO signals fulfilling requirements of different wireless communication standards. Previous works [1] [2] have done a lot to design carrier generation system whose output ranges cover major communication standards like GSM, WCDMA, WLAN, Bluetooth, etc. This work presents another frequency synthesizer which provides LO for multi-standard receiver. The output range of the synthesizer covers standards of DCS1800, WCDMA, TD-SCDMA, Bluetooth, WLAN 802.11a/b/g. Common challenge when designing multi-standard carrier generation system is trade-off between wide output range and high power efficiency. This problem can be tackled only by careful frequency planning for the system. This paper firstly describes the idea behind the frequency planning of the system. Then we present implementation of different building blocks in the proposed Σ- Δ Fractional-N frequency synthesizer. Section simulation results. II. ARCHITECTURE AND FREQUENCY PLANNING Frequency planning is the key to designing frequency synthesizer for multi-standard receiver. That’s because the performance of the receiver as well as its area and power consumption is strongly influenced by it. And the planning is also strongly correlated with the receiver’s topology. In our case, this synthesizer is designed for a direct conversion receiver. It is more desirable to separate the oscillator frequency away from the RF frequency to avoid LO pulling. In order to do this, combination of dividers and oscillator working in multiple RF frequency can be adopted. However, wide output frequency range may require wideband VCO which is difficult to implement. To resolve this problem, more than one oscillator can be used to increase the PLL’s tuning range. Multiple oscillators will increase the die area. And since oscillators have to work in a much higher frequency, it is difficult for some processes to fabricate them or will consume a huge amount of power even if they do. But the performance of spur is good for this solution because divider not only introduces no extra spurious tone but also improves the suppression of spurs near the carrier by 6dB. What’s more, divide by two circuit inherently generates quadrature signals whose precision only depends on duty cycle of the input signal. A combination of mixers and dividers following a VCO working in a lower frequency is also a solution to wide output range frequency synthesizer. It’s more feasible since This work was sponsored by National Sci & Tech Major Projects of China with grant number of 2009ZX03006-007 and National High Tech R&D (863) Program of China with grant number of 2009AA01Z261. 978-1-4244-5309-2/10/$26.00 ©2010 IEEE discusses the 2071 Fig. 1 Diagram of proposed multi-standard frequency synthesizer the VCO is operating in a lower frequency. Less power is consumed for the same reason. However, the performance of spurious tones is suffered at the output of the mixer because of mismatch and nonlinearity. The process we use is TSMC 0.13μm CMOS, it is not appropriate to operate at a high frequency for VCO. So, combination of dividers and SSBmixer is adopted to enable wideband output in our design. The presented frequency synthesizer is capable of generating receiver carriers for WCDMA, DCS1800, TDSCDMA, WLAN (802.11a/b/g) and Bluetooth standards. As shown in Fig. 1, Σ-Δ Fractional-N PLL is adopted. FractionalN architecture allows an arbitrary output frequency resolution, so it is appropriate for multi-standard receiver. Since direct conversion topology is adopted, quadrature LO signal is needed for complex signal processing. For the standards of WCDMA, GSM, TD-SCDMA, 802.11 b/g and Bluetooth, quadrature LO is generated by a divide by two circuit following the QVCO. Because their LO frequencies are relatively low, it is still plausible to generate frequency which is twice the RF frequency. What’s more, standards like WCDMA, GSM, TD-SCDMA and Bluetooth have stringent requirement on LO phase noise and spur performances. It is unacceptable to generate their carriers by a mixer. Paralleling to the divide by two path is the path of divide by four cascading a harmonic rejection SSBmixer [3] (HRSSBmixer). This path is responsible for carrier generation for 802.11a. WLAN 802.11a using Orthogonal Frequency Division Multiplexing (OFDM) has large bandwidth. As a result, the LO phase noise requirement is set by the integral noise. The specification for spurious tones is loosened and that enables SSBmixer’s output as LO signal for this standard. HRSSBmixer is used to carry out single side band up-conversion, so no filter is needed to reject the unwanted side band generated in the process of mixing. In order to realize the quadrature output, two HR-SSBmixers are needed. And each input should be quadrature in order to generate outputs with correct phase relation. So QVCO is used in this synthesizer for the purpose of providing quadrature input for the HRSSBmixers. Harmonic rejection SSBmixer is used to suppress spurious tones resulting from the third and fifth harmonic of the divide by four circuit’s output. 45 degree spaced clocks for the HR-SSBmixer are provided by divide by four circuit. Performance of image rejection and harmonic rejection of the HR-SSBmixer is strongly influenced by mismatch between transistors in the circuit itself as well as mismatch between the inputs. In order to generate precise quadrature signal, dummy circuits are often added to balance the load of VCO buffer. In our case, divide by 2 circuit and divide by 4 circuit are designed to load the VCO buffer equally. see, the oscillator does not operate in the same frequency as the output, as a result of which, LO pulling is avoided. According to the phase noise and spur specifications of different standards, outputs are allocated in different places. The object is to achieve an optimized tradeoff between performance and consumptions of hardware and power. III. CIRCUIT DESIGN AND IMPLEMENTATION A. QVCO Quadrature VCO consisting of two cross-coupled LC oscillator cores is used in this frequency synthesizer. HRSSBmixer uses the quadrature signals to carry out single side band up-conversion and provides LO for 802.11a. Conventional cross-coupled quadrature oscillator has not been widely used because of its poor phase noise performance. Two LC VCOs are coupled and LC tanks operate away from resonance frequency. As a result of which, phase noise performance is destroyed due to that the optimal quality factor of the LC tank is not reached [4]. What’s more, coupling transistors will contribute additional noise to the output. And oscillator becomes more sensitive to AM-PM conversion because of the coupling mechanism. Since outputs of the QVCO serve as inputs of HRSSBmixer, the phase relation of the quadrature outputs should be clearly determined in order to carry out correct single side band up-conversion. However, in conventional quadrature VCO, the phase relation is not deterministic due to the bimodal oscillation effect [5]. This effect shows that conventional quadrature LC oscillator may exhibit two stable oscillation states at different operating frequencies. The oscillation state here means different lead-lag phase relations of the outputs. In order to solve the two problems mentioned above, phase shifters can be introduced [4]. The bottom line is that phase shifter is added in the coupling stage and therefore no phase shift from the tank is required to meet Barkausen’s phase criteria. What’s more, QVCO will stay away from bimodal oscillation boundaries if a sufficient phase shift is maintained [5]. Design of the phase shifter is nontrivial. It should not be too complicate in case too much power is consumed and it should not de-Q the tank. The proposed phase shifter used in the QVCO is shown in Fig.2. We split the tail current source of coupling transistors and add a parallel R-C network between source terminals of coupling transistors. In this way, the resistors in the phase shifter consume no dc voltage drop which is appropriate for low power voltage situation. Since it Table 1 lists the relations between oscillator frequency and outputs of the frequency synthesizer respectively. As we can TABLE I. Frequency Planning Standards WCDMA FDD-RX Bluetooth RX WLAN a 802.11 b g TD-SCDMA RX DCS1800 RX fmin~fmax(MHz) 2110~2117 2400~2483 5015~5850 2400~2484 2400~2484 2300~2400 1805~1880 Relation fvco/2 fvco/2 5fvco/4 fvco/2 fvco/2 fvco/2 fvco/2 Fig. 2 QVCO with proposed phase shifter 2072 is not directly connected to the tank, quality factor of the tank is not affected. Phase shifter can align current and voltage in each tank. Therefore, the optimal quality factor of the LC tank can be reached. Insertion of a phase shifter also moves the QVCO operation away from the unstable boundary and eliminates bimodal oscillation. Another benefit of introducing phase shifter is that it greatly decouples phase accuracy and phase noise performance of the oscillator. Because it desensitizes the QVCO to mismatch from tail current and tank quality factor [6]. Transconductance of the coupling transistors can be written as G mc = 1+sR s Cs gm 1+g m R s 1+sR s Cs /(1+g m R s ) (1) There are one pole and one zero in the transconductance. The zero frequency is ωz=1/RsCs and the pole frequency isωp≈gm/Cs. The zero results in a phase-lead to the transconductance. Ideally, the phase shift should be 90 degree at the frequency of oscillation to align current and voltage of the tank. However, this requires that the pole frequency at least 100 times of the zero frequency which means ωp/ωz≈gmRs=100. Resistor degeneration will make coupling transconductance at resonance frequency so small that the phase accuracy of the quadrature outputs of QVCO is degraded. In fact, phase shift up to 50 degree is already enough to increase the effective tank quality factor and reduce the phase noise. The proposed QVCO uses all-PMOS device considering its lower flicker noise than NMOS. Oscillator’s output range is from 3.5GHz to 5GHz. The tail currents are adaptively controlled by Automatic Frequency Control (AFC) circuit to keep the oscillation magnitude constant and equal to the optimize level in which phase noise performance is the best. Binary weighted switched capacitor bank is used to divide the total oscillator output range up to 64 sub-ranges. The capacitor bank is also controlled by the AFC. Varactors biased in different points are connected in parallel to linearize the transfer curves of the QVCO. AM-PM up-conversion phase noise can be minimized and effective voltage range in oscillator’s control line is enlarged. counter. Divide by 4 is implemented by the first two stages of programmable divider and current mode logic (CML) to CMOS logic transfer circuit. Programmable divider is composed of cascading divide by 2/3 modules. The first two stages are controlled to divide by 2 only when AFC is enabled. C. Programmable Divider As shown in Fig. 3, the programmable divider, based on [8], consists of 7 divide by 2/3 cells. The first two stages are implemented by CML while the last five stages are implemented by TSPC logic. The divider should be with a programmable range from 75 to 124 according to the frequency of VCO and the frequency of reference. Considering the third order sigma-delta modulator, the divider should be programmable from 72 to 128. The presented divider provides division ratio from 26~28-1. For fractional-N frequency synthesizer, programmable divider is controlled by sigma-delta modulator. So it is important to correctly update the divide value every reference cycle without causing interference to the operation of programmable divider [9]. Based on the idea of [9], we add additional logic generating output enable signal for sigma-delta modulator. Instead of using fout of all divide by 2/3 cells to generate the enable signal for the modulator as [9], we only use the last six stages. In this way, additional power-hungry logic transfer buffer can be avoided. Timing analysis find that delaying the enable signal for a certain time also satisfies the timing requirement to update division ratio correctly. There is a problem existing in this divider. No logic is taking care of dynamic switching from 6 cells to 7 cells. The timing of programmable divider and sigma-delta modulator will be ruined. Simulation shows that PLL cannot be locked in this situation. This problem is being solved in a new version of the frequency synthesizer. B. AFC In order to increase the VCO’s tuning range and reduce VCO gain, switched capacitor bank is used in the resonator. AFC technique should be used to ensure that proper transfer curve of the VCO is selected. Each time a new division ratio of the synthesizer is programmed, the AFC will be enabled. Division-ratio-based AFC [7] is adopted in this design. Output of the VCO is first divided by 4 and then inputted to the Fig. 4 Layout of the synthesizer and its settling behavior Fig .5 Phase noise performance Fig. 3 Programmable divider 2073 QVCO without phase shifter In order to validate that phase shifter improves QVCO’s performance. Simulation is done to the proposed circuit and two circuits in Fig. 6. Fig. 6 (a) is a conventional QVCO. In Fig.6 (b), two LC oscillators couple in “in phase” style. LC tank in Fig.6 (b) operate in its resonance frequency. It cannot generate quadrature signals and can be seen as two parallel connected oscillators. Transistors, bias currents and LC tank are all identical in these three circuits. Fig. 7 gives the phase noise comparison result. With phase shifter, phase noise performance is improved by about 3~4dB. At some frequency offset, it is even better than parallel connected LC-VCO. We also find that the proposed QVCO operates closer to the LC tank resonance freuqncy (Fig. 6(b)) while conventional QVCO (Fig. 6 (a)) operates 115MHz away from it. This means the proposed QVCO has a larger effective quality factor. The resulted FOM ranges from 181dB to 187dB across the output range. Fig. 8 shows the Monte Carlo simulation results. Coupling factor equal 0.5 for conventional QVCO. Because of 0 Phase noise (dBc/Hz) -60 Fig5(b)-fosc=3.944GHz 100K 1M 10M 100M 90.1 90.15 90 90.05 89.9 89.75 89.95 Samples 90.3 90.43 90.18 90.05 89.8 89.93 89.68 89.55 0 89.3 [2] [5] -180 10K 50 0 output phase relation(°) CONCLUSION REFERENCES [1] [8] Offset Frequency (Hz) 100 A Σ-Δ Fractional-N frequency synthesizer generating carriers for cellular and short range wireless communication standards is presented. Through careful frequency planning and circuit design, the system is implementable on chip in 0.13μm CMOS process. By adding phase shifter to the QVCO, the synthesizer shows improved performance in phase noise. Although confined to several standards in this version, this system can be extended to cover more standards by simply adding dividers. -160 1K 150 50 V. -120 100 200 the source degeneration, proposed QVCO’s coupling factor is smaller. PSS large signal simulation finds that its coupling factor is 0.28. However, its standard deviation of output phase is better than that of conventional QVCO, which means phase accuracy of proposed QVCO is less sensitive to mismatch. -100 -140 150 Fig. 8 Monte Carlo simulation results [7] -80 200 output phase relation(°) Fig4-fosc=3.935GHz -40 250 100 [6] Fig 5(a)-fosc=4.059GHz μ=90.001 σ=59.7504m N=1000 300 89.8 250 [4] -20 μ=90.0019 σ=193.893m N=1000 300 [3] (a) (b) Fig. 6 Oscillators coupled to operate (a) in quadrature (b) in phase 350 89.43 The proposed frequency synthesizer is implemented in TSMC 0.13μm CMOS process. All circuit blocks have been integrated on chip. Layout of the die is shown in Fig.4. The chip area is about 1.86 × 1.8 mm2 with active core of 1.85 mm2. Bandwidth of the PLL is about 90 kHz; and the reference frequency is 40MHz. Power consumed by the core circuits is 1.2V × 46.6mA. As shown in Fig. 4, it takes less than 50μs for PLL to settle. The AFC time is only about 6μs. Simulation shows that image rejection ratio and third harmonic rejection ratio of HR-SSBmixer are 56dB and 64dB respectively. The circuit does well in image rejection and harmonic rejection since layout work is properly done. Phase noise simulation of the synthesizer is done at the output of QVCO. Fig.5 shows the phase noise result when oscillator working at the frequency of 4.2GHz. The phase noise is 119dBc/Hz at 1MHz offset frequency. Simulation is also carried out at the output of divide by 2 and HR-SSBmixer. Specifications of all standards can be met. QVCO with phase shifter 350 89.85 SIMULATION RESULTS Samples IV. [9] Fig. 7 Phase noise comparison 2074 Adil Koukab, Yu Lei and Michel Declercq, “Multi-standard carrier generation system for quad-band GSM / WCDMA (FDD-TDD) /WLAN (802.11 a-b-g) radio,” Proceedings of the 31th European SolidState Circuits Conference, pp.177 - 180, September 2005. Pierluigi Nuzzo, et. al. , “A 0.1-5GHz dual-VCO software-defined ΣΔ frequency synthesizer in 45nm digital CMOS,” IEEE RFIC Symposium, pp.321-324 Jun 2009. J. A. Weldon, et. al. , “A 1.75-GHz highly integrated narrow-band CMOS transmitter with harmonic-rejection mixers,” IEEE J. SolidState Circuits, vol. 36, pp. 2003–2015, Dec 2001. J. van der Tang, P. van de Ven, D. Kasperkovitz, and A. van Roermund, “Analysis and design of an optimally coupled 5-GHz quadrature LC oscillator,” IEEE J. Solid-State Circuits, vol. 37, pp. 657–661, May 2002. Shenggao Li, Issy Kipnis, Mohammed Ismail, “A 10-GHz CMOS quadrature LC-VCO for multirate optical applications,” IEEE J. SolidState Circuits, vol. 38, pp. 1626–1634, Oct 2003. A. Mirzaei, M. E. Heidari, R. Bagheri, S. Chehrazi, A. A. Abidi , “The quadrature LC oscillator: a complete portrait based on injection locking,” IEEE J. Solid-State Circuits, vol. 42, pp. 1916–1932, Sep 2007. Lei Lu, Zhichao Gong, Youchun Liao, Hao Min, Zhangwen Tang, “A 975-to-1960MHz fast-locking fractional-N synthesizer with adaptive bandwidth control and 4/4.5 prescaler for Digital TV Tuners” ISSCC Dig. of Technical Papers, pp. 396-398, Feb. 2009. C. S. Vaucher, et. al., “A family of low-power truly modular programmable dividers in standard 0.35-μm CMOS technology”, IEEE Journal of Solid-State Circuits, vol. 35, no. 7, pp. 1039-1045, July 2000 C.-M. Hsu, “Techniques for high performance digital frequency synthesis and phase control,” Ph.D. dissertation, Dept. Elect. Eng. Comput. Sci., Mass. Inst. Technol., Cambridge, MA, 2008