J. Park, F. Maloberti: "Fractional-N PLL with 90° Phase Shift Lock and

advertisement

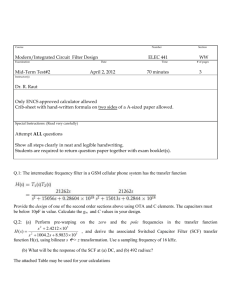

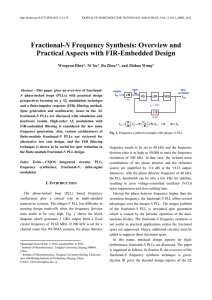

J. Park, F. Maloberti: "Fractional-­N PLL with 90° Phase Shift Lock and Active Switched-­Capacitor Loop Filter"; Proc. of the IEEE Custom Integrated Circuits Conference, CICC 2005, San Josè, 21 September 2005, pp. 329-­‐332. ©20xx IEEE. Personal use of this material is permitted. However, permission to reprint/republish this material for advertising or promotional purposes or for creating new collective works for resale or redistribution to servers or lists, or to reuse any copyrighted component of this work in other works must be obtained from the IEEE. IEEE 2005 CUSTOM INTEGRATED CIRCUITS CONFERENCE Fractional-N PLL with 90º Phase Shift Lock and Active Switched-Capacitor Loop Filter Joohwan Park(1), and Franco Maloberti(2) (1) University of Texas at Dallas, P.O.Box 830688, Richardson, TX 75083, USA. (2) Department of Electronics, University of Pavia, 27100 Pavia, Italy. joohwan@student.utdallas.edu, franco.maloberti@unipv.it Abstract-This paper describes a new possibility of fully integrated fractional-N phase locked loop (PLL). The approach uses switched-capacitor fully differential low pass filter (LPF) instead of huge continuous-time filter. The discrete-time operation has the potential to provide a phase noise enhancement (PNE) block, variable gain, to improve noise. The circuit is implemented in 2.8 mm2 including all capacitors and Ȉǻ modulator using 0.25 µm CMOS process. The proposed PLL achieves a phase noise of -102 dBc at 600 kHz and spur level of -80 dBc with mid-band frequency. Power dissipation is 30 mW with a 3-V supply. I. INTRODUCTION Mobile communication architectures use PLL able to comply with the frequency hopping requirements and provide low phase noise output in the IF receiver and the up conversion transmitter. The targets must be possibly accomplished with all the components fabricated in a single chip. This is not always possible since the filtering requirements for the low-pass filter often lead to external capacitors or demand for large silicon area that, in turn, increases the cost. In the present solutions in locked loop conditions one of the current generator of the phase frequency detector (PFD) switches on for a very short time. The noise on rise and fall time of the current pulse is affecting the accuracy of the circuit operation. Moreover, the continuous-time filtering of high frequency components is, in some extent, problematic. If the loop-bandwidth is very narrow, the phase-noise is good, but the locking time and the channel switching time increase [1]. The best would be using a dynamic control of the loop filter response that enhances the phase noise when the PLL is in the lock state. between acquisition mode and phase lock mode lead to a longer PLL settling time. This paper describes a fractional-N PLL that uses a PFD with 90º phase-shift lock. The feature reduces the rise and fall time influence and enhances the charge pump linearity. Moreover, the 90º phase-shift feature enables an operation in the sampled-data domain. Thus, it is possible to implement the loop filter using the switched capacitor technique and obtain on-chip filtering functions that can be digitally programmable. The proposed approach has been proved with a fully integrated version. The PLL employs a source couple multivibrator [5] with 133-MHz free running frequency. However, the approach can be used with other types of VCO and higher operating frequency. II. The two inputs of a PFD are the reference and the output of the fractional divider. In the lock conditions, the frequencies of the two inputs are equal and a possible phase shift is the information used to control the VCO. We observe that the reference can be the basis for a clock (at low frequency). Therefore, having the reference signal facilitates a lowfrequency sampled-data processing. Assume that the phase shift of the PFD inputs, REF and Output, is as shown in Fig. 1, 90º. A simple logic can generate the control signals X1 and X2. They are used to switch-on the equal current generators of the PFD; a third switch resets the integrating capacitor at the end of the half-period of the reference. A fractional frequency results from a periodic change of the division factor between two (or more) integer numbers. Using of a sigma delta modulator obtains a fractional control with a good noise shaping. However, even if the N/N+1 divider control is well randomized, there is extra fluctuation in the VCO control. Thus, the loop filter design becomes more challenging. The solution can be the use of programmable loop filter [2], employing dual path [3] or multiple charge pumps [4]. In general the problems associated to the uncertainty 0-7803-9023-7/05/$20.00 ©2005 IEEE. PROPOSED METHOD P-34-1 Fig. 1 – Illustration of the basic concept used in the paper 329 IV. FRACTIONAL-N PLL WITH SC FILTER LOOP Fig. 3 shows the block diagram of the designed fractional-N PLL. It is composed of a PFD (with the charge pump), sampling capacitor, switched capacitor filter, smoothing filter, voltage controlled oscillator (VCO), divider and sigma-delta modulator. Once in lock, the sigma-delta modulator will control the output to get fractional frequency and it will convert the systematic fractional sidebands to random noise. Actually, the cascade of a switched capacitor and a continuous-time section makes the loop filter. Since the clock frequency of the SC is the reference frequency, the continuous-time is a simple RC which pole is at 0.06fR. The loop filters used MIM capacitors. The resistor of the RC smoothing is a 100 KΩ poly structure. Fig. 2 – Proposed loop filter The 90º phase shift makes equal to zero the voltage across the capacitor immediately before the reset. If the shift is larger we have a negative voltage, the opposite if the shift is smaller. Obviously, the reset of the capacitor can be done through a virtual ground, thus obtaining the input of a sampled-data circuit. Observe that it is problematic using the method for 0º phaseshift: The integration of the current into a capacitance is obviously possible but the timing of measurement and the reset phase can be properly defined only using a delayed version of the reference. III. SWITCHED CAPACITOR LOOP FILTER Fig. 2 shows a possible fully differential loop filter to be associated with the 90º phase shift PFD. The charge stored on the sampling capacitances at the end of phase 1 is the input of the low-pass active filter. Assuming that the reference signal is in the MHz range, the required bandwidth of the OTA is few ten of MHz, thus requiring limited power consumption. The reference frequency and the maximum swing VM allowed by the current generators of the PFD determine the relationship between the capacitor Cs and the current in the PFD, IPFD. Assume that full-scale input signal of the SC filter is VM. With 0º phase shift, the upper current generator is switched on for 1/(2·fR) while the lower one never switches on. Thus Cs ⋅ VM = IPFD 2 ⋅ fR The VCO is a modified version of the source-coupled multivibrator. The architecture was selected just to demonstrate the capability to fully integrate the PLL. The free-running oscillation frequency is relatively low (133-MHz). The method is quite general: the use of oscillator with LC tank would give a higher free-running frequency with the need of a pre-scalar. A detailed description of the VCO is given below. The resolution obtained by the second-order sigma delta is 1MHz/27. The design uses a standard cell approach and the total area is 0.5 x 0.4 mm. A. VCO Description The circuit diagram of the source-coupled multivibrator is shown Fig. 4. It is the CMOS version of a well know bipolar configuration. The oscillation frequency depends on the capacitor size and amount of current through it. Two additional sections (in the dashed blocks) enable the frequency control. The two sections change the core bias currents in the positive or negative direction under the control of a differential signal. The capacitance C is 1.1pF, the currents I1 and I2 are 1mA and 0.2mA respectively. The resulting range of frequency variation is ±25MHz. The degeneration resistances in the additional blocks help in improving the linearity of the control block. Simulation results show that by optimizing the transistor sizes for minimizing the 1/f noise while keeping the speed leads to good linearity and reasonable phase noise. (1) with VM= 0.4V and fR= 1MHz a current IPFD= 0.8µA gives Cs= 1pF. The ratio between CS and CR gives the dc gain of the SC filter. The value of the sampling capacitance and the capacitances of the SC filter are suitable for a fully integrated implementation. The filter in Fig. 2 is a simple low-pass. Either using a single OTA or with more than one OTA is possible to realize more complex filtering functions. Moreover, the use of digitally programmable capacitances enables a digital control of the loop filter. 330 P-34-2 Fig. 3 – Discrete time PLL The next stage is the SC loop filter with programmable gain. A sensing block detects the voltage level at the output of the buffer and changes the gain by 6dB. The control is simple but suitable for demonstrating the flexibility of the used approach. Fig. 6 shows the plot of the forward signal as a function of the sensing voltage. The response is non-linear with a jump at the transition points. The region with low gain is for operation in the locked mode. The threshold is ±5mV and is big enough to account for the fluctuations due to noise and spurs contributions. A signal above |5mV| indicates the non-locked mode: the gain jumps up by 6 dB. The given response is the optimum for limiting the locking time degradation. Simulation results, verified by experimental measurement show that with a full gain the locking time is 180 µsec with the phase noise enhancement the locking time is 200 µsec. Fig. 4 – Modified VCO with current control circuit V. PHASE NOISE ENHANCEMENT The use of an active sampled-data control instead of a simple continuous-time filter provides good flexibility and programmability. In order to reduce the phase noise, it is necessary to desensitize the VCO control when the loop is in the lock zone. This is what is done in [4] is to use digitally programmable multiple charge pumps. The action is equivalent to a programmable gain in the signal at the output of the charge pump. This chip includes a gain control section that, at the same time decouple the charge pump section by the loop SC filter. The circuit schematic is shown in Fig. 5. It includes two OTA. The first is a inverting unity-gain buffer. Fig. 6 – Variable gain with PNE Fig. 5 – Phase noise enhancement block and fully differential LPF P-34-3 331 VI. EXPERIMENTAL RESULT The fully differential phase locked loop discussed in previous sections has been fabricated in a 0.25-µm CMOS technology with 2.8 mm2 of active area (Fig. 7). Because the LPF size is drastically decreased, the switch capacitor PLL becomes suitable for a full integration. With proper shielding, the noise coupling is blocked from digital block to analog and VCO. In addition, large on-chip PMOS capacitor is used to maintain a small bounce on the supply. The power dissipation is 30 mW from a 3-V supply. Fig. 8 shows the voltages across the sampling capacitors in lock conditions. The signal has the expected triangular shape due to the charging and discharging phases. The trigger of the scope synchronizes itself during the first and second of the reference period. The fractional-N synthesizer locks properly at 128.3-MHz. A 128/129 dual divider brings the frequency of the VCO down to the 1MHz used by the reference. The free-running frequency of the VCO is 134.6-MHz, close to the designed value 133-MHz. Fig. 9 shows the measured phase noise without and with the PNE function. Results show that the PNE reduces the spur level below -80 dBc. Fig. 9 – Phase noise measurement: without PNE (solid) with PNE (dashed) Moreover, the phase noise at 600 kHz is as low as -102 dBc; 5 dB better than without the enhancement circuit. Multiple gain values and a smart digital control possibly permit 15 dB of phase noise improvement. The spur level is not completely satisfactory. Continuous-time solutions obtain better results. However, the result is still comparable with other published figures [3]. VII. CONCLUSION In the paper, we demonstrate possibility of a fully on-chip design and phase noise enhancement in the Ȉǻ fractional-N PLL. A switched capacitor LPF enables on-chip implementation being only 50pF used for the fully differential LPF. The used capacitance is at least ten times smaller than a continuous-time counterpart. The use of switched capacitor active processing offers the benefit of digital control filtering. As an example the chip includes a phase noise enhancement circuit: it reduces the loop gain in the lock conditions and permits a 5 dB reduction of the phase noise. Therefore, the proposed approach and the experimental verifications open new perspective for the design of fully integrated fractional-N PLL. Fig. 7 – PLL die photograph REFERENCES [1] [2] [3] [4] Fig. 8 – Sampling capacitor waveform 332 [5] P-34-4 E. Temporiti, G. Albasini, I. Bietti, R. Castello and M. Colombo, “A 700-kHz bandwidth Ȉǻ fractional synthesizer with spurs compensation and linearization techniques for WCDMA application,” IEEE J. SolidState Circuits, vol. 39, Sep. 2004. P. Jacobs, J. Janssens, T. Geurts and J.Crols, “A 0.35µm CMOS fractional-N transmitter for 315/433/868/915 MHz ISM applications,” European Solid-State Circuits, Sept. 2003. Z. Shu, K. L. Lee and B. H. Leung, “A 2.4-GHz ring-oscillator-based CMOS frequency synthesizer with a fractional divider dual-PLL architecture,” IEEE J. Solid-State Circuits, vol. 39, Mar. 2004. D. Boerstler, “A low-jitter PLL clock generator for microprocessors with lock range of 340-612 MHz,” IEEE J. Solid-State Circuits, vol. 34, Apr. 1999. P. Gray, P. Hurst, S. Lewis and R. Meyer, Analysis and design of analog integrated circuits, Fourth Ed., New York: John Wiley, 2001.