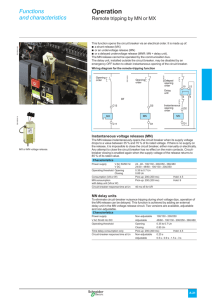

Design and Operation Principles of DC Circuit Breakers

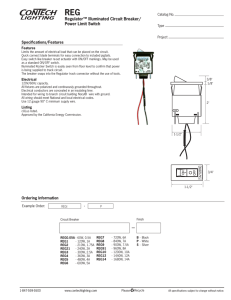

advertisement