To do the analysis and design of simple MOSFET amplifiers

advertisement

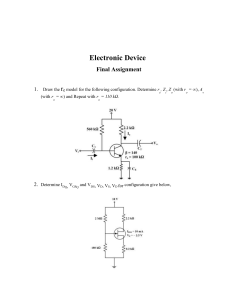

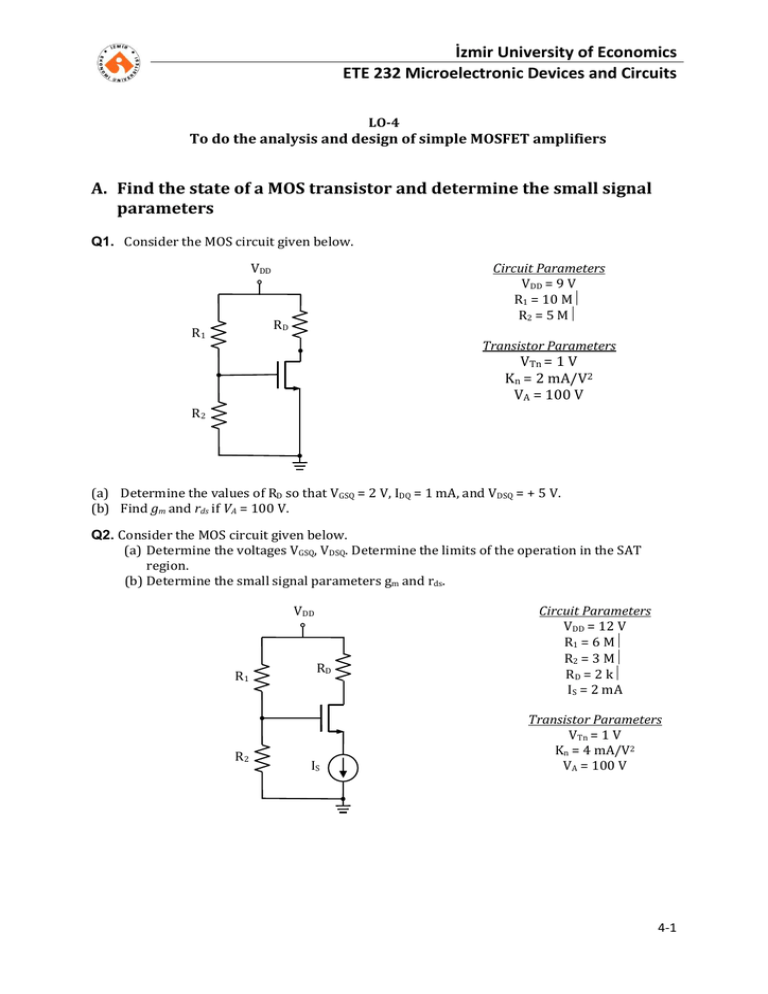

İzmir University of Economics ETE 232 Microelectronic Devices and Circuits LO-4 To do the analysis and design of simple MOSFET amplifiers A. Find the state of a MOS transistor and determine the small signal parameters Q1. Consider the MOS circuit given below. VDD Circuit Parameters VDD = 9 V R1 = 10 MΩ R2 = 5 MΩ RD R1 Transistor Parameters VTn = 1 V Kn = 2 mA/V2 VA = 100 V R2 (a) Determine the values of RD so that VGSQ = 2 V, IDQ = 1 mA, and VDSQ = + 5 V. (b) Find gm and rds if VA = 100 V. Q2. Consider the MOS circuit given below. (a) Determine the voltages VGSQ, VDSQ. Determine the limits of the operation in the SAT region. (b) Determine the small signal parameters gm and rds. VDD R1 R2 RD IS Circuit Parameters VDD = 12 V R1 = 6 MΩ R2 = 3 MΩ RD = 2 kΩ IS = 2 mA Transistor Parameters VTn = 1 V Kn = 4 mA/V2 VA = 100 V 4-1 Q3. A MOS amplifier core circuit is given below. VDD Rin R1 Circuit Parameters VDD = 15 V R1 = 10 MΩ R2 = 5 MΩ RS = 100 KΩ RD Transistor Parameters R2 VTn = 1 V Kn = 2 mA/V2 VA = 100 V RP (a) Determine the values of RD and RP so that VGSQ = 2 V, IDQ = 1 mA, and VDQ = + 6 V. (b) Find gm and ro if VA = 100 V. (c) Draw a complete AC small-signal equivalent circuit for the amplifier assuming all capacitors behave as short circuits at signal frequencies. B. DC and AC small signal analysis of MOS transistor amplifier circuits Q4. The figure below shows a common source (CS) amplifier employing the classical biasing scheme. The input signal vs is coupled to the gate through a very large capacitor. The source of the transistor is connected to ground at signal frequencies via a very large capacitor. The output voltage signal that develops at the drain is coupled to a load resistance via a very large capacitor. Circuit Parameters VDD VDD = 15 V R1 = 10 MΩ Rout R2 = 5 MΩ RL = 7.5 KΩ Rin RD R1 C3 RS = 100 KΩ RS C1 Transistor Parameters + vS R2 C2 RL VO RP VTn = 1 V Kn = 2 mA/V2 VA = 100 V (c) (d) (e) (f) Draw the DC equivalent circuit. Determine the values of RD and RP so that VGSQ = 2 V, IDQ = 1 mA, and VDQ = + 7.5 V. Find gm and ro if VA = 100 V. Draw a complete AC small-signal equivalent circuit for the amplifier assuming all capacitors behave as short circuits at signal frequencies. (g) Find Rin and Rout. (h) Determine vgs/vs, vo/vgs, and vo/vs ratios. 4-2 Q5. Consider the CS amplifier given below. All capacitors are large enough so that they behave as short circuits at signal frequencies. (c) Draw the DC model of the circuit. (d) Determine the voltages VGSQ, VDSQ. Determine the limits of the operation in the SAT region. (e) Determine the small signal parameters gm and ro. (f) Draw the AC small signal equivalent circuit. (g) Determine the overall voltage gain Av = vo/ vs. VDD RD R1 Circuit Parameters VDD = 12 V R1 = 6 MΩ R2 = 3 MΩ RD = 2 kΩ RL = 7.5 kΩ IS = 2 mA C3 C1 + vS RL C2 R2 VO IS - Transistor Parameters VTn = 1 V Kn = 4 mA/V2 VA = 100 V C. DC and AC load line analysis for simple transistor amplifier circuits Q6. Consider the amplifier given below. VDD R1 RS RD C3 C1 + vS R2 C2 RL vO RP - (i) (j) (k) (l) (m) (n) (o) (p) (q) Circuit Parameters VDD = 15 V RS = 100 kΩ R1 = 10 MΩ R2 = 5 MΩ RL = 7.5 kΩ RD = 7.5 kΩ RP = 3 kΩ Transistor Parameters VTn = 1 V Kn = 2 mA/V2 VA = 100 V Determine RP so that the circuit given has the Q point values of VGSQ = 2 V, IDQ = 1 mA, and VDSQ = + 4.5 V. Draw the DC load line on iD vs vDS graph. Locate Q point on the DC load line. Draw the AC load line. Draw the boundary curve of the LIN-SAT regions. Determine the limits of the output voltage vDS for linear undistorted operation. Determine peak-to-peak value of the output small signal voltage vds. If vs = Vp sinω0t volts, determine Vp for the undistorted output voltage and express also the output voltage for this input. Discuss also the limits on vgs to neclect vgs2 term in the circuit analysis. 4-3 Q7. The circuit given below has the Q point values of VGSQ = 2 V, IDQ = 1 mA, and VDSQ = + 6 V. VDD R1 RD Circuit Parameters VDD = 12 V R1 = 6 MΩ R2 = 3 MΩ RD = 2 kΩ RL = 7.5 kΩ IS = 2 mA C3 C1 + vS R2 C2 RL VO IS - Transistor Parameters VTn = 1 V Kn = 4 mA/V2 VA = 100 V (a) (b) (c) (d) (e) (f) Locate Q point on the iD vs vDS graph. Draw the AC load line. Draw the boundary curve of the LIN-SAT regions. Determine the limits of the output voltage vDS for linear undistorted operation. Determine peak-to-peak value of the output small signal voltage vds. If vs = Vp sinω0t volts, determine Vp for the undistorted output voltage and express also the output voltage for this input. (g) Discuss also the limits on vgs to neclect vgs2 term in the circuit analysis. 4-4 Q8. Consider the following amplifier. The DC and AC load lines of this amplifier are given below. VDD Circuit Parameters RG = 4 MΩ RD = 6 kΩ Rout RD Rin Transistor Parameters C3 C1 VTn =1 V Kn = 1 mA/V2 VA = ∞ + RG RL C2 vS VGG vO RP - iD V1 =10.5 volts I1 V2 =15 volts VDSQ =7.5 volts AC load line I2 IDQ = 1mA DC load line IDQ vDS V0 (a) (b) (c) (d) VDSQ V1 V2 Determine the voltage VDD and the resistances RP and RL. Determine the voltage VGG. Determine the AC small signal voltage gain AV = vO/vS. Determine the total voltage vD if vS = 0.1 sin ω0t volt. Microelectronics, Donald A. Neamen, Fourth Edition, 2010 A. Common Drain (Source Follower) Amplifier Q9. Problem 4.33. (Text book. pp. 272) Q10. Problem 4.34. (Text book. pp. 273) Q11. Problem 4.37. (Text book. pp. 273) B. Common Gate Amplifier Q12. Problem 4.48. (Text book. pp. 276) Q13. Problem 4.49. (Text book. pp. 276) Q14. Problem 4.50. (Text book. pp. 276) 4-5