Output Stages

advertisement

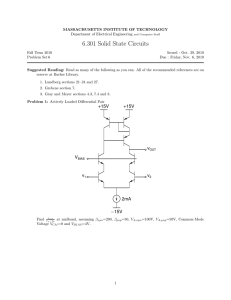

Output Stages • Output stage must deal with large signal swings • Small signal model assumption is not valid, but emitter follower behaves somewhat linearly • Emitter follower is not power efficient + R4 2300Ω VCC 15V R3 3E3Ω R1 20E3Ω + R2 20E3Ω VEE -15V Q7 Q4 Q2 Q1 + Q5 VI SIN Q8 R7 28600Ω Q9 Q3 Q6 R5 157E2Ω R6 3E3Ω Lecture 18-1 Output Stages • The linearity of the output stage is of primary importance • Minimize output signal distortion • Design goodness is measured in terms of total harmonic distortion (THD) RMS of output signal harmonics RMS of output signal fundamental frequency • THD should be much less than 1% for a good stereo receiver • Other concern is with delivering a lot of power without wasting power on the output transistors • Output stages are classified into various types • We’ll look briefly at class A, class B and class AB Lecture 18-2 Class A • Large signal emitter follower with a current source bias VCC vi Q1 i L vo I RL -VEE • “I” must be greater than the largest negative load current Lecture 18-3 Class A • Assuming vBE is small, it behaves somewhat linearly: VCC vi Q1 i L vo I RL -VEE Lecture 18-4 Class A • Offset is added to VIN so that output is zero for zero ac input + VCC 15V IREF 500mA VI Q1 + 760.000 mV - + VIN SIN Q3 Q2 + VOUT + 4.486 mV - RL 100Ω VEE -15V Lecture 18-5 Class A • Large signal response is fairly linear, even with large load currents 0.0 0.1 time 0.2 ms 20 V 10 0 -10 VOUT VI Lecture 18-6 Class A Power Dissipation • Power dissipation can be excessive, even with no ac input signal • For example, when vo=0, what is the power dissipation on the transistor? VCC + 15V IREF 500mA Q1 + VIN SIN VOUT Q3 Q2 + RL 100Ω VEE -15V Lecture 18-7 Class B -- Push-Pull Output Stage • Designed so that both transistors cannot be conducting at the same time using a pair of emitter followers VCC vi QN i L vo QP RL -VCC Lecture 18-8 Class B • The class B is simpler to design, and no offset is required for VIN + VCC 15V VI + 0.000 pV - + Q1 Custom VIN SIN Q2 Custom VOUT + 0.000 pV - + RL 10Ω VCCN -15V Lecture 18-9 Class B • Large signal response is still fairly linear, even with larger load current 0.0 0.1 time 0.2 ms 10 V 0 -10 VOUT VI Lecture 18-10 Class B Crossover Distortion • The problem is the deadband region for which both QP and QN are off • Produces unwanted noise for an audio signal 40 50 60 70 80 90 100 110 time us 10 V 0 -10 VOUT VI Lecture 18-11 Class B Power Dissipation • dc power dissipation is zero • Avg. power can be calculated for each transistor • The postive load current is supplied by QN, and the negative is supplied by QP 0.0 0.1 0.2 0.3 0.4 0.5 0.6 time ms 1 A 0 -1 IRL Lecture 18-12 Class B Power Dissipation • The instantaneous power is the same for both the push and the pull 0.0 0.1 0.2 0.3 0.4 0.5 time 0.6 ms 10 0 -10 IRL*VOUT VOUT Lecture 18-13 Class AB • The most difficult aspect of the class AB design is creating the VBB bias voltages + VCC 15V Q1 Custom + VI + 0.000 pV - + VIN SIN + VBB1 0.8V VBB2 0.8V Q2 Custom VOUT + 0.000 pV - + RL 10Ω VCCN -15V Lecture 18-14 Class AB • Input and output are now overlapping, with no cross-over distortion 0.0 0.1 time 0.2 ms 10 V 0 -10 VOUT VI Lecture 18-15 More Elaborate Multi-Stage Amplifiers • Now you can “sort of” recognize all of the major portions of a 741 opamp Lecture 18-16 Cascode Amplifier • Most differential IC stages will use a cascode stage or something similar to one VCC VCC RC RC vo1 vo2 vref + vd I _ VEE Lecture 18-17 Cascode Amplifier • Cascode amplifiers are often used for generating high output impedance and/ or high frequency operation VCC RC vo vi Lecture 18-18 Cascode Amplifier VCC RC vo vi Lecture 18-19

![Iin Vin Vin and Iin are the values given in [Series Impedance] Vload](http://s2.studylib.net/store/data/018206929_1-d327defc9b9e133751f2a98335f9c6fb-300x300.png)