lecture 060 – push-pull output stages

advertisement

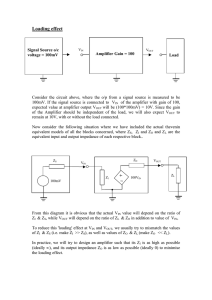

Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-1 LECTURE 060 – PUSH-PULL OUTPUT STAGES (READING: GHLM – 362-384, AH – 226-229) Objective The objective of this presentation is: Show how to design stages that 1.) Provide sufficient output power in the form of voltage or current. 2.) Avoid signal distortion. 3.) Be efficient 4.) Provide protection from abnormal conditions (short circuit, over temperature, etc.) Outline • Push-Pull MOS (Class B) • Push-Pull BJT (Class B) • Summary ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-2 PUSH-PULL MOS OUTPUT STAGES (Class AB and B) Push-Pull Source Follower VDD VDD Can both sink and source M6 M1 VGG current and provide a slightly M5 M1 lower output resistance. VSS VBias VSS iOUT vIN VDD VSS iOUT vOUT VBias M2 VDD RL VDD M4 M2 VDD vOUT RL Efficiency: vIN M3 Depends on how the VSS Fig. 060-01 VSS VSS transistors are biased. • Class B - one transistor has current flow for only 180° of the sinusoid (half period) vOUT(peak)2 2RL PRL π vOUT(peak) ∴ Efficiency = P = = 2 VDD˚-VSS VDD 1 2vOUT(peak) (VDD˚-VSS)2˚ πRL Maximum efficiency occurs when vOUT(peak) =VDD and is 78.5% • Class AB - each transistor has current flow for more than 180° of the sinusoid. Maximum efficiency is between 25% and 78.5% ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-3 Illustration of Class B and Class AB Push-Pull, Source Follower Output current and voltage characteristics of the push-pull, source follower (RL = 1kΩ): 2V 1mA vG1 iD1 1V 0mA vout vG1 vG2 0V 0mA -1mA iD2 -2V 0 2 1 Vin(V) Class B, push-pull, source follower -1 vG2 vout -1V iD2 -2V -2 1mA iD1 1V 0V -1V 2V -2 -1mA 0 2 1 Vin(V) Class AB, push-pull,VIN source follower -1 Fig. 060-02 Comments: • Note that vOUT cannot reach the extreme values of VDD and VSS • • • IOUT+(max) and IOUT-(max) is always less than VDD/RL or VSS/RL For vOUT = 0V, there is quiescent current flowing in M1 and M2 for Class AB Note that there is significant distortion at vIN =0V for the Class B push-pull follower ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-4 Small-Signal Performance of the Push-Pull Follower Model: vgs1 + + vin gm1vgs1 + + vin - - C1 vgs1 gmbs1vbs1 rds1 gm2vgs2 gmbs2vbs2 rds2 RL C2 + vout - - C1 gm1vin 1 RL g gm1vout gmbs1vout rds1 gm2vin gm2vout m2gmbs2vout rds2 C2 + vout Fig. 060-03 vout gm1 + gm2 vin = gds1+gds2+gm1+gmbs1+gm2+gmbs2+GL 1 Rout = gds1+gds2+gm1+gmbs1+gm2+gmbs2 (does not include RL) If VDD = -VSS = 2.5V, Vout = 0V, ID1 = ID2 = 500µA, and W/L = 20µm/2µm, Av = 0.787 (RL=∞) and Rout = 448Ω. A zero and pole are located at -(gm1+gm2) -(gds1+gds2+gm1+gmbs1+gm2+gmbs2+GL) z= p = . C1 C1+C2 These roots will be high-frequency because the associated resistances are small. ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-5 Push-Pull, Common Source Amplifiers Similar to the class A but can operate as class B providing higher efficiency. VDD M2 VTR2 iOUT vIN vOUT VTR1 RL M1CL VSS Fig. 060-04 Comments: • The batteries VTR1 and VTR2 are necessary to control the bias current in M1 and M2. • The efficiency is the same as the push-pull, source follower. ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-6 Practical Implementation of the Push-Pull, Common Source Amplifier VDD M6 M5 M1 M3 VGG3 iOUT vIN vOUT M2 M4 VGG4 M7 CL RL M8 VSS Fig. 060-05 VGG3 and VGG4 can be used to bias this amplifier in class AB or class B operation. Note, that the bias current in M6 and M8 is not dependent upon VDD or VSS (assuming VGG3 and VGG4 are not dependent on VDD and VSS). ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-7 Illustration of Class B and Class AB Push-Pull, Inverting Amplifier Output current and voltage characteristics of the push-pull, inverting amplifier (RL = 1kΩ): vG2 2V iD1 1V vG1 iD2 iD1 0V iD2 -1V vOUT -2V -2V 2mA 2V 1mA 1V 0mA 0V -1mA -1V -2mA -2V 2mA vG2 vG1 iD1 1mA iD1 0mA iD2 vOUT iD2 -1mA -2mA -2V 0V 1V 2V vIN Class AB, push-pull, inverting amplifier. Fig.060-06 -1V 0V 1V 2V vIN Class B, push-pull, inverting amplifier. -1V Comments: • Note that there is significant distortion at vIN =0V for the Class B inverter • Note that vOUT cannot reach the extreme values of VDD and VSS • IOUT+(max) and IOUT-(max) is always less than VDD/RL or VSS/RL • For vOUT = 0V, there is quiescent current flowing in M1 and M2 for Class AB ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-8 Use of Negative, Shunt Feedback to Reduce the Output Resistance Concept: VDD Error Amplifier vIN - Error Amplifier M2 + iOUT vOUT + CL M1 VSS RL Fig. 060-07 rds1||rds2 Rout = 1+Loop Gain Comments: • Can achieve output resistances as low as 10Ω. • If the error amplifiers are not balanced, it is difficult to control the quiescent current in M1 and M2 • Great linearity because of the strong feedback • Can be efficient if operated in class B or class AB ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-9 Simple Implementation of Neg., Shunt Feedback to Reduce the Output Resistance VDD M2 R1 R2 iOUT vIN vOUT CL M1 RL Fig. 060-08 VSS R1 gm1+gm2 Loop gain ≈ R +R g +g +G 1 2 ds1 ds2 L˚ rds1||rds2 Rout = R1 gm1+gm2 1+R1+R2gds1+gds2+GL ∴ Let R1 = R2, RL = ∞, IBias = 500µA, W1/L1 = 100µm/1µm and W2/L2 = 200µm/1µm. Thus, gm1 = 3.316mS, gm2 = 3.162mS, rds1 = 50kΩ and rds2 = 40kΩ. 50kΩ | |40kΩ 22.22kΩ ∴ Rout = = (Rout = 5.42kΩ if RL = 1kΩ) 3316+3162 1+0.5(143.9) = 304Ω 1+0.5 25+20 ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-10 What about the use of BJTs in CMOS Technology? VDD VDD M3 VDD Q1 iB M2 vout vout iB Q1 M2 M3 CL VSS p-well CMOS VSS CL VSS n-well CMOS Fig. 060-09 Comments: • Can use either substrate or lateral BJTs. • Small-signal output resistance is 1/gm which can easily be less than 100Ω. • Unfortunately, only PNP or NPN BJTs are available but not both on a standard CMOS technology. • In order for the BJT to sink (or source) large currents, the base current, iB, must be large. Providing large currents as the voltage gets to extreme values is difficult for MOSFET circuits to accomplish. • If one considers the MOSFET driver, the emitter can only pull to within vBE+VON of the power supply rails. This value can be 1V or more. ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-11 PUSH-PULL BJT OUTPUT STAGES (Class AB and B) Simple Class B Output Stage vOUT VCC Q1 Saturates VCC-VBE1 Slope ≈ 1 Q1 on Q2 off Q1 vIN RL Q2 + vOUT - VBE(on) VBE(on) VEE+VBE2+VCE1(sat) VEE Q2 Saturates vIN VCC+VBE1-VCE1(sat) Slope ≈ 1 Q1 off Q2 on VEE+VBE2 Fig. 060-10 Class B operation: Two active devices are used to deliver the power instead of one. Each device conducts for alternate half cycles. Efficiency can approach 78.5% Can suffer from crossover distortion - the transition from one device to the other. ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-12 Class AB Output Stage vOUT VCC IQ VCC Slope ≈ 1 Q1 Q3 Q4 Q2 RL vIN Q1 Saturates VCC-VBE1 vIN + vOUT - VEE VBE(on) Q2 Saturates VEE+VEB2 Fig. 060-11 IQ sets up the bias current in Q1 and Q2 when there is no input signal. Each transistor is biased so that there is a region in the middle where both are on (Class AB) ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-13 Power Considerations in the Class B Output Stage Voltage and current waveforms for a Class B amplifier: vin 2T VCC T VCC Q1 IQ t vout ic1 Vout(peak) Q3 Q4 ic2 Q2 vin + vout - RL 2T T ic1 t Ic1(peak) VEE 2T T ic2 2T T t t Ic2(peak) Fig. 060-12 ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-14 Efficiency Considerations of the Class-B Push-Pull Output Stage Load line for one device in a class-B stage: iC1 Load Line VCC RL Peak device dissipation Constant Power Curve VCE1(sat) Quiescent Point 0 0 0.5VCC VCC Load Line 2VCC-VCE1(sat) vCE1 Fig. 060-13 Efficiency: 1 [Vout(peak)]2 PL = 2 RL Ic(peak) 1 T 2 VCC ⌠ and Psupply = 2VCCIsupply = 2VCC T ⌡iC(t)dt = 2VCC π = π RL Vout(peak) 0 PL π Vout(peak) VCC ∴ η= P = supply 4 ⇒ π ηmax = 4 = 78.6% π VCC -VCE(sat) Max. efficiency for the above class-B push-pull output stage is η max =4 VCC ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-15 709 Output Stage 4 VCC 10 VCC IQ RL = 10kΩ 5 3 2 + Q2 RL 1 vOUT Q1 vOUT - Q3 0 RL = 1kΩ -5 vIN 5 VEE -10 0.6 Fig. 060-14 0.61 709 Output Stage Voltage Transfer Function .MODEL BJTN NPN IS=1E-14 BF=100 VAF=50 .MODEL BJTP PNP IS=1E-14 BF=50 VAF=50 Q1 4 3 2 BJTN Q2 5 3 2 BJTP Q3 3 1 5 BJTN VCC 4 0 DC 10V VEE 5 0 DC -10V 0.62 0.63 0.64 vIN 0.65 0.66 0.67 VIN 1 5 RL 2 0 1KILOHM R1 4 3 20KILOHM .DC VIN 0.60 0.67 0.001 .PRINT DC V(2) .PROBE .END This stage assumes that feedback will be used around the amplifier which will linearize the nonlinearity of the output stage. ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-16 741 Output Stage VCC 7 Q13B 6 Q13C Q13A 5 10 Q14 5 4 R10= 40kΩ 1 Q18 2 RL 3 Q20 + vOUT - vOUT Q19 0.22mA 9 15 0 -5 Q23 Q17 -10 vIN Fig. 060-15 8 VEE 741 Output Stage Voltage Transfer Function - RL = 1Kilohm .MODEL BJTN NPN IS=1E-14 BF=100 VAF=50 .MODEL BJTP PNP IS=1E-14 BF=50 VAF=50 Q23 8 1 3 BJTP Q20 8 3 2 BJTP Q14 7 5 2 BJTN Q17 1 9 8 BJTN Q18 5 4 3 BJTN Q19 5 5 4 BJTN Q13A 5 6 7 BJTP Q13B 1 6 7 BJTP 3.0 ECE 6412 - Analog Integrated Circuits and Systems II -15 0.62 0.63 0.64 vIN 0.65 0.66 0.67 Q13C 6 6 7 BJTP VCC 7 0 DC 15V VEE 8 0 DC -15V IBIAS 6 0 220UA VIN 9 8 DC 0.645 R10 4 3 40KILOHM RL 2 0 1KILOHM .DC VIN 0.625 0.665 0.0005 .PRINT DC V(2) .PROBE .END © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-17 Quasi-Complementary Output Stages Quasi-complementary connections are used to improve the performance of the PNP or PMOS transistor. Composite connections: E + VEB B - E + IE VEB Q1 IC1 VSG IE - B - G Q2 + S VSG M1 ID1 G - Q2 IC C IC S + ID ID D C D Fig. 060-16 PMOS Equivalent: PNP Equivalent: VEB K P ’W 1 IC = (1+β 2) IC1 = (1+β 2) Isexp Vt ID = (1+β 2) ID1 = (1+β 2) 2L1 (VGS-VT)2 ∴ The composite has the beta of an ∴ The composite has an enhanced K’ NPN ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-18 Overload Protection For circuits that can provide large amounts of output current, it is necessary to provide short-circuit current protection. Example: iOUT VCC iC2 ii RLim = 0 iC1 iB1 Q1 RLim ≠ 0 ILim Q2 RLim iOUT Fig. 060-17 Short-Circuit 0 0 ii iOUT = iC1+iC2 ≈ iC1 ∴ iOUT = β 1iB1= β 1(ii -iC2) vBE2 iC1RLim But iC2 ≈ Is2exp V ≈ Is2exp V t t iC1RLim ∴ iOUT = β 1ii - Is2exp V t As iOUT increases, Q2 turns on and pulls base current away from Q1 limiting the output current. ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002 Lecture 060 – Push-Pull Output Stages (1/6/02) Page 060-19 SUMMARY Requirements of Output Stages • The objectives are to provide output power in form of voltage and/or current. • In addition, the output amplifier should be linear and be efficient. • Low output resistance is required to provide power efficiently to a small load resistance. • High source/sink currents are required to provide sufficient output voltage rate due to large load capacitances. • Types of output stages considered: Class B or AB stage with push-pull (maximum efficiency was 78.6%) • Quasi-complementary devices help improve the performance of the p-type devices • Protection circuits prevent large currents from flowing in the output devices • For large load capacitors all that is required from an output stage is large current, the output resistance does not have to be small ECE 6412 - Analog Integrated Circuits and Systems II © P.E. Allen - 2002