To be published in Appl. Phys. Lett.

advertisement

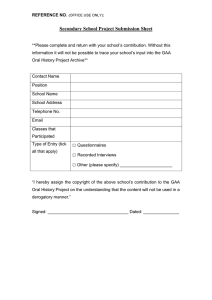

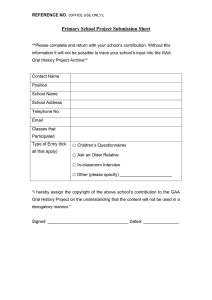

To be published in Appl. Phys. Lett. Encapsulated gate-all-around InAs nanowire field-effect transistors Satoshi Sasaki,1, a) Kouta Tateno,1 Guoqiang Zhang,1 Henri Suominen,1 Yuichi Harada,1 Shiro Saito,1 Akira Fujiwara,1 Tetsuomi Sogawa,1 and Koji Muraki1 NTT Basic Research Laboratories, NTT Corporation, Atsugi, Kanagawa 243-0198, Japan (Dated: 28 October 2013) We report the fabrication of lateral gate-all-around InAs nanowire field-effect transistors whose gate overlaps the source and drain electrodes and thus fully encapsulates the nanowire channel. They feature large drive current and transconductance that surpass those of conventional non-gate-overlap devices. The improved device characteristics can be attributed to the elimination of access resistance associated with ungated segments between the gate and source/drain electrodes. Our data also reveal a correlation between the normalized transconductance and the threshold voltage, which points to a beneficial effect of our wet-etching procedure performed prior to the atomic-layer-deposition of the gate dielectric. a) sasaki.s@lab.ntt.co.jp 1 Integration of high-mobility group III-V semiconductor materials onto the Si platform is being pursued as an important technology for future electronic devices, aiming primarily at the reduced power consumption expected from the high on-current operation at low supply voltage.1 Low off-current, which implies low stand-by power consumption, is another important requirement. In this view, thin-body devices with multiple gates, in particular, those with gate-all-around (GAA) geometry, in which the channel is completely surrounded by the gate, are advantageous because of the improved electrostatic control. Self-assembled semiconductor nanowires (NWs) are promising candidates for such thin-body channel materials, and are receiving considerable attention as building blocks for the next-generation nanoelectronics devices.2–4 InAs is one of the most suitable NW materials for application to high-speed, low-power-consumption field-effect transistors (FETs), in view of its intrinsic high electron mobility in excess of 30000 cm2 /Vs at room temperature. GAA NW-FETs in both vertical5–8 and lateral9,10 geometry have been reported for InAs. However, these previous reports found drastically degraded electron mobility compared to the bulk value, which was ascribed to the strong surface-roughness and ionized-impurity scattering resulting from the large surface-to-volume ratio.11,12 In fact, by exploiting such extreme sensitivity to the surface impurities, NW-FETs have proved capable of being utilized as an efficient charge sensor,13 which, in turn, highlights the importance of appropriate surface passivation. Here, we report the fabrication and DC electrical characterization of lateral GAA InAs NW-FETs. The GAA structure was realized by adopting a two-step gate-electrode formation method, in which a NW conformally coated with a gate dielectric is sandwiched between the lower planar gate and the upper encapsulating gate. This method allows the gate electrode to overlap the source/drain electrodes and thereby produces a substantial increase in the drive current compared with the previously reported non-gate-overlap NW-FETs,5–10 by eliminating the parasitic resistance arising from the gap region (underlap region) between the gate and source/drain electrodes. Our data also reveal a correlation between the normalized transconductance and the threshold voltage, which points to a beneficial effect of our wet-etching procedure performed prior to the atomic-layer-deposition (ALD) of the gate dielectric. The InAs NWs were grown in a low-pressure metal-organic vapor phase epitaxy system14,15 using Au colloids with a diameter of 20 nm dispersed on a GaAs (100) substrate as a catalyst. Trimethylindium (TMIn) and tertiarybutylarsine (TBAs) were supplied as In and As sources 2 FIG. 1. (Color online) (a) Schematic of the Si/SiO2 device substrate prepatterned with Ti/Au source/drain leads and lower gate. (b) Schematic of the lower gate showing its cross-sectional structure with a transferred nanowire on top. (c) Device structure after deposition of Al/Al2 O3 source/drain electrodes and at the stage of an overlapping upper gate deposition. (d) Schematic of the cross-section along the NW axis showing the gate-overlap structure. (e) Schematic of the cross-section perpendicular to the NW axis at the center of the FET showing the GAA structure. (f) False color SEM image of the fabricated device. Green regions denote Al ohmic contacts with oxidized surfaces. Bright parts marked by solid triangles are Ti/Au lead lines connecting the source/drain electrodes to the probing pads. The region enclosed by the dotted line denotes the central part of the device depicted in Figs. (b) - (e). 3 at flow rates of 1.5 - 2.3 and 45 - 160 µmol/min, respectively, with the substrate temperature at 350 - 400 ◦ C. The as-grown NWs were wet-etched with diluted HCl (HCl:H2 O = 1:5) for about 20 seconds in order to remove natural oxides and possible impurities on the NW surface along with several monolayers of InAs. This was performed inside a glove box with an oxygen and water vapor concentration of less than 0.1 ppm and 0.5 ppm, respectively. As we shall see later, this etching is likely to remove the surface InAs layer with specific morphologies producing donor-like states,16–18 and thus impacts the FET operation. The etched NWs were transferred to the ALD chamber without exposure to air and conformally coated with 6 nm of Al2 O3 at 250 ◦ C, produced using trimethylaluminium (TMA) and H2 O. This Al2 O3 thickness corresponds to an equivalent oxide thickness (EOT) of 2.7 nm. After the ALD, the NWs were sonicated in isopropanol and drop-cast onto a Si/SiO2 substrate prepatterned with Ti/Au lower gate electrodes and source/drain lead lines [Fig. 1(a)]. As the cross-sectional view in Fig. 1(b) shows, the lower gate has a two-layer structure, with its bottom layer designed to be wider than the top layer. As we shall see later, this two-layer structure is essential to eliminate unwanted ungated regions between the lower gate and the source/drain electrodes, allowing the underhung regions of the lower gate to vertically overlap the source/drain electrodes. The underhung regions are covered with SiO2 of 40 nm thickness, such that the source/drain electrodes can be defined without shorting them [Fig. 1(c) and 1(d)]. Source/drain electrodes were fabricated by first removing the surface oxides on the NW in the contact regions via Ar plasma etching and then evaporating Al in-situ without breaking vacuum.19 The lateral distance between the Al electrodes and the exposed lower gate metal is typically 40 nm, designed to be larger than the alignment error of the electron-beam lithography machine. Electrical connection was made through the prepatterned Ti/Au leads that contact the outer ends of the Al electrodes. The total resistance of the ohmic contacts and Ti/Au leads, estimated from a comparison of two-probe and four-probe resistances, ranges between a few hundred Ω and a few kΩ depending on the length of the metal lead lines. For electrical isolation from the upper gate, the Al surface was oxidized in an O2 plasma to form an Al2 O3 insulator. The upper gate was fabricated by evaporating Ti/Au at an angle from both sides of the NW to ensure better adhesion of the gate metal to the NW sidewalls. Figure 1(e) schematically shows the fabricated GAA structure in a cross-sectional view perpendicular to the NW axis. A scanning electron micrograph (SEM) image of our typical GAA InAs NW-FET device is shown in Fig. 1(f). 4 FIG. 2. (Color online) (a) Output characteristics of the GAA NW-FET at room temperature with gate length Lg = 220 nm and channel diameter d = 70 nm. These dimensions were estimated from an SEM image with an error of less than 10 nm. (b) Transfer characteristics of the same NW-FET. The transconductance for Vd = 0.5 V is also plotted. Logarithmic plot of Id versus Vg for Vd = 0.1 V is shown in the inset. (c) Normalized maximum transconductance at Vd =0.1 V versus threshold voltage for several NW-FETs fabricated at the same time. The numbers beside each data point represent the gate length in nm unit. The solid circle indicates a data point for our best device shown in (a) and (b). 5 DC electrical characterization of the GAA InAs NW-FETs was performed using a semiconductor parameter analyzer (Agilent B1500A) at room temperature. Figure 2(a) depicts the output characteristics of a GAA NW-FET with gate length (equal to source-drain separation) Lg = 220 nm and channel diameter d = 70 nm. The figure shows drain current Id plotted versus drain voltage Vd for different values of gate voltage Vg varied between −1 and 2 V in 0.5 V steps. Figure 2(b) shows the transfer characteristics (Id versus Vg ) for Vd = 0.1 and 0.5 V, plotted together with transconductance, gm = dId /dVg , for Vd = 0.5 V. These data show n-type FET operation with the threshold voltage Vt = 0.39 V, which was determined by linearly extrapolating Id from the Vg value at which the transconductance max max reaches a maximum value, gm [see the dotted line in Fig. 2(b)]. For Vd = 0.5 V, gm is as large as 120 µS, which corresponds to 550 µS/µm when normalized by the total wire circumference, w = πd. The values of on-current, Idon = 40 µA, estimated at the gate overdrive voltage Vg − Vt = 23 Vd = 0.33 V, and the maximum drive current, Idmax = 160 µA, obtained at Vg = 2.5 V, correspond to 180 and 720 µA/µm, respectively, when normalized max by w. These normalized values, gm /w of 550 µS/µm and Idon /w of 180 µA/µm, exceed max the values, gm /w = 520 µS/µm and Idon /w = 150 µA/µm, reported for a vertical GAA max InAs NW-FET with a much shorter gate length of Lg = 50 nm6 . Our normalized gm /w and Idon /w are also larger than those reported for other short-channel vertical GAA NWFETs7,8 and long-channel lateral NW-FETs.9–12,20,21 As for gate-overlap, but not GAA, InAs max NW-FETs, Blekker et al. reported gm /w of 30 µS/µm at Vd = 0.02 V for a device with max Lg = 200 nm.22 This is comparable to, but slightly smaller than our gm /w of 160 µS/µm at Vd = 0.1 V when the difference in Vd is taken into account. Thus, in terms of the on-state characteristics, our GAA NW-FET outperforms the existing FETs with a channel made of a homogeneous NW of group III-V materials. Therefore, it is worth comparing our device with those employing core-shell type NWs23,24 and that employing a NW with doped source/drain segments25 as a channel material, for which even higher performance is reported. In terms of transconductance, our device with 550 µS/µm at Vd = 0.5 V is outperformed by these devices with 800 µS/µm (Ref. 23), 1.42 mS/µm (Ref. 24), and 1.23 mS/µm (Ref. 25) at Vd = 0.5 V, by a factor of 1.5 - 2.6. Let us now discuss the impact of pre-ALD wet-etching we employed. Our NW-FET shown above has positive Vt while, in general, negative Vt is expected because InAs has a naturally formed electron accumulation layer with the Fermi level pinned above the conduction band 6 edge. Our pre-ALD etching removes the InAs layer with specific surface morphologies that act as donors,16–18 which would increase Vt . In Fig. 2(c), we plot normalized maximum max /w at Vd =0.1 V versus Vt for several NW-FETs fabricated at the transconductance gm same time including the one shown above (solid circle). It can be seen that Vt scatters greatly, ranging from negative to positive values, most likely due to the fluctuation in the wet-etching depth and/or in the initial carrier concentration, making it difficult to quantify the influence of the pre-ALD etching on Vt . Nevertheless, Fig. 2(c) reveals a clear trend that, for similar Lg , the on-state performance improves as Vt becomes more positive, and the best device has the maximum Vt .26 This suggests a beneficial effect of the pre-ALD wet-etching on the FET characteristics. Another important metric, which characterizes the off-state properties of FETs, is the subthreshold slope (SS), defined as dVg /d log Id below Vt . As shown in the inset to Fig. 2(b), the above device has a SS of 270 mV/decade, which is several times larger than the theoretical limit of 60 mV/decade at room temperature. Although the smallest SS of 140 mV/decade we obtained in another device is better than that in InAs GAA NW-FETs reported previously,8,10 it is still larger than the theoretical limit. Given the ideal electrostatic control realized by using the GAA geometry, the SS values we obtained suggest room for improvement in the NW/gate dielectric interface quality. One straightforward direction would be to increase the pre-ALD wet-etching time as Fig. 2(c) suggests. Further optimization of the ALD condition would be also necessary, for example, by increasing the flushing time to completely remove the residual Cl left after the wet-etching. We could also apply the present fabrication method to InAs/InP core-shell NWs since the epitaxially grown InP shell is know to greatly improve the interface quality.23,27 To gain insight into the improved on-state properties, we also examined a GAA NWFET fabricated using the same two-step gate formation method, but without a gate-overlap [see the SEM image and the schematic shown in the insets to Fig. 3]. The device has ungated segments, about 200-nm long each, of the NW on both sides of the gated region (Lg = 220 nm), similar to the devices studied in Refs. 9 and 10. The solid line in Fig. 3 shows the transfer characteristics at Vd = 0.5 V of this NW-FET. The data for the gateoverlap device shown in Fig. 2(b) is plotted together for comparison (the dashed line). The two devices happen to have almost the same Vt ≃ 0.39 V. It is clearly seen that overall the gate-overlap device has a much larger conductance, which is attributable to the reduction in 7 FIG. 3. (Color online) Comparison of the transfer characteristics between the GAA NW-FET with gate-overlap and the one without gate-overlap, having almost identical d = 70 nm and Lg = 220 nm. The insets show an SEM picture of the latter device (the scale bar is indicating a length of 200 nm) and its schematic structure. FIG. 4. (Color online) The Id −Vg and gm −Vg characteristics of a GAA NW-FET with Lg = 2.5 µm. The inset shows an SEM image of this device before the upper gate deposition. The scale bar indicates a length of 1 µm. the parasitic resistance arising from the ungated NW segments28 . In addition, the complete enclosure of the NW channel by the gate metal may enhance the screening of the Coulomb scattering potential due to residual ionized impurities on the NW surface, and thereby contribute to the large drive current via improved electron mobility. 8 We now estimate field-effect mobility µFE with a routinely used expression intended for a long-channel device in the diffusive transport limit µFE L2g gm = , Cg Vd (1) where Cg is the gate capacitance. For diffusive transport, conductance is expected to scale with the inverse of the total channel length, which, however, is not the case for the shortchannel devices shown in Fig. 3. The conductance of the non-gate-overlap device is much larger than what is expected from its total channel length (2/3 of which is ungated) that is three times that of the gate-overlap device. This indicates that these short-channel devices are not suitable for estimating field-effect mobility using Eq. (1). Therefore, we analyze the result for a long-channel NW-FET device with Lg = 2.5 µm, whose SEM image is shown in the inset to Fig. 4. One advantage of our gate-overlap geometry is that it eliminates the need for the rather complex equation12,21 that one must otherwise resort to for the correction of the parasitic resistance, thus providing more solid ground for the use of Eq. 1. Employing a simple coaxial capacitor model that takes into account a tapering of this NW, with d varying max from 35 nm to 70 nm over the 2.5 µm length, Cg = 6.1 fF is calculated. Using gm = 7.4 µS obtained in the linear regime (Vd = 0.1 V) as shown in Fig. 4, µFE = 760 cm2 /Vs is estimated for this long-channel device. This value is nearly an order of magnitude larger than that of a similar GAA NW-FET reported previously.10 For compariosn, we also fabricated a long-channel GAA NW-FET (Lg = 2.2 µm) using the standard approach, i.e., without gate-overlap or pre-ALD wet etching, and obtained a much lower µFE of 210 cm2 /Vs. This clearly demonstrates the advantage of our approach. However, µFE of 760 cm2 /Vs is still an order of magnitude smaller than the highest values of µFE = 6000 ∼ 7000 cm2 /Vs reported for NW-FETs having a much thicker gate dielectric.11,21 The smallness of the µFE value we obtained can be partially explained by inaccuracy in the estimated Cg value, inherent to the oversimplified model neglecting the effects of a finite length of NW, interface states, and semiconductor capacitance (quantum capacitance).29,30 The impact of quantum capacitance is particularly enhanced for a thin and high-k gate dielectric layer as in the present case, leading to the overestimation of Cg 11 and hence the underestimation of µFE . As demonstrated in Ref. 9, the actual value of Cg directly measured on an individual GAA NW-FET is much smaller than that calculated with the simple coaxial capacitor model. Accordingly, as customarily done, the above value of µFE = 760 cm2 /Vs should be regarded 9 as a lower bound for the actual electron mobility. In summary, we have fabricated GAA InAs NW FETs whose gate overlaps the source and drain electrodes and thus fully encapsulates the channel. A device with a short gate length, Lg = 220 nm, features normalized maximum drive current of 720 µA/µm and transconductance of 550 µS/µm at room temperature. These values demonstrate the best on-state characteristics for FETs with a channel made of a homogeneous NW of group III-V materials, which can be attributed to the reduction in access resistance and to the pre-ALD treatment by wet-etching. The authors are grateful to H. Murofushi for technical assistance in device fabrication, and to T. Hayashi, N. Maeda and K. Kanisawa for valuable discussions. REFERENCES 1 J. A. del Alamo, Nature 479, 317 (2011). 2 C. Thelander, P. Agarwal, S. Brongersma, J. Eymery, L. F. Feiner, A. Forchel, M. Scheffler, W. Riess, B. J. Ohlsson, U. Gosele, and L. Samuelson, Mater. Today 9, 28 (2006). 3 W. Lu, P. Xie, and C. M. Lieber, IEEE Trans. Electron Devices 55, 2859 (2008). 4 L. E. Wernersson, C. Thelander, E. Lind, and L. Samuelson, Proc. IEEE 98, 2047 (2010). 5 T. Bryllert, L.-E. Wernersson, L. E. Froberg, and L. Samuelson, IEEE Electron Device Lett. 27, 323 (2006). 6 C. Thelander, L. E. Froberg, C. Rehnstedt, L. Samuelson, and L.-E. Wernersson, IEEE Electron Device Lett. 29, 206 (2008). 7 C. Thelander, C. Rehnstedt, L. E. Froberg, E. Lind, T. Martensson, P. Caroff, T. Lowgren, B. J. Ohlsson, L. Samuelson, and L.-E. Wernersson, IEEE Trans. Electron Devices 55, 3030 (2008). 8 T. Tanaka, K. Tomioka, S. Hara, J. Motohisa, and T. Fukui, Appl. Phys. Express 3, 025003 (2010). 9 S. Dhara, S. Sengupta, H. S. Solanki, A. Maurya, A. P. R., M. R. Gokhale, A. Bhattacharya, and M. M. Deshmukh, Appl. Phys. Lett. 99, 173101 (2011). 10 K. Storm, G. Nylund, L. Samuelson, and A. P. Micolich, Nano Lett. 12, 1 (2012). 11 A. C. Ford, J. C. Ho, Y.-L. Chueh, Y.-C. Tseng, Z. Fan, J. Guo, J. Bokor, and A. Javey, Nano Lett. 9, 360 (2009). 10 12 S. A. Dayeh, E. T. Yu, and D. Wang, Small 5, 77 (2009). 13 J. Salfi, I. G. Savelyev, M. Blumin, S. V. Nair, and H. E. Ruda1, Nat. Nanotechnol. 5, 737 (2010). 14 G. Zhang, K. Tateno, S. Suzuki, H. Gotoh, and T. Sogawa, J. Phys. Chem. C 115, 2923 (2011). 15 K. Tateno, G. Zhang, H. Gotoh, and T. Sogawa, Nano Lett. 12, 2888 (2012). 16 M. Noguchi, K. Hirakawa, and T. Ikoma, Phys. Rev. Lett. 66, 2243 (1991). 17 L. Olsson, C. Andersson, M. Hakansson, J.Kanski, L. Ilver, and U. Karlsson, Phys. Rev. Lett. 76, 3626 (1996). 18 K. Kanisawa and T. Fujisawa, Proc. of 14th International Conference on Thin Films and Reactive Sputter Deposition 2008 (ICTF14/RSD2008) , 108 (2008). 19 T. Nishio, T. Kozakai, S. Amaha, M. Larsson, H. A. Nilsson, H. Q. Xu, G. Zhang, K. Tateno, H. Takayanagi, and K. Ishibashi, Nanotechnology 22, 445701 (2011). 20 Q.-T. Do, K. Blekker, I. Regolin, W. Prost, and F. J. Tegude, IEEE Electron Device Lett. 28, 682 (2007). 21 S. A. Dayeh, D. P. R. Aplin, X. Zhou, P. K. L. Yu, E. T. Yu, and D. Wang, Small 3, 326 (2007). 22 K. Blekker, B. Munstermann, A. Matiss, Q. T. Do, I. Regolin, and W. Brockerhoff, IEEE Trans. Nanotechnol. 9, 432 (2010). 23 X. Jiang, Q. Xiong, S. Nam, F. Qian, Y. Li, and C. M. Lieber, Nano Lett. 7, 3214 (2007). 24 K. Tomioka, M. Yoshimura, and T. Fukui, Nature 488, 189 (2012). 25 A. W. Dey, C. Thelander, E. Lind, K. A. Dick, B. M. Borg, M. Borgstrom, P. Nilsson, and L.-E. Wernersson, IEEE Electron Device Lett. 33, 791 (2012). 26 Here, Vt is smaller than 0.39 V due to its Vd dependence in the present device. 27 J. van Tilburg, R. Algra, W. Immink, M. Verheijen, E. Bakkers, and L. Kouwenhoven, Semicond. Sci. Technol. 25, 024011 (2010). 28 If a typical ohmic contact resistance of 2 kΩ is subtracted from the observed resistances, the non-gate-overlap device has roughly twice as much intrinsic resistance as the gateoverlap one in the whole Vg region. This means that the resistance difference associated with the ungated segments has similar Vg dependence due to the fringing gate electric field effect. 29 D. R. Khanal and J. Wu, Nano Lett. 7, 2778 (2007). 11 30 K. Alam, Semicond. Sci. Technol. 24, 085003 (2009). 12