Review And Analysis Of Dc Converter Switching

advertisement

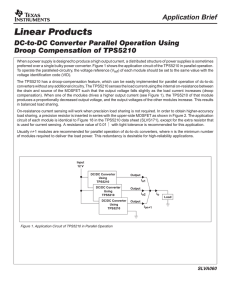

International Journal of Computer and Advanced Engineering Research (IJCAER) Volume 02– Issue 01, February 2015 REVIEW & ANALYSIS OF DC CONVERTER SWITCHING TECNIQUES & TOPOLOGIES Pankaj Mohan[1] , P.G. Scholar, Electrical Engineering Department, SSSIST, Bhopal Prabodh Khampariya[2] , Assistant Professor, Electrical Engineering Department, SSSIST, Bhopal ABSTRACT An area of prime concern for all designers today is to be able to design a switching power supply that is able to operate in all the power systems. Switching mode power supplies typically operate over a single voltage range, of 90 -130 VAC or 200 -270 VAC. For applications requiring higher voltage ranges a specialised design is needed. This paper presents a descriptive design methodology and analysis outcomes of an interleaved fly-back converter with zerovoltage-switched active switches having two identical parallel operated Fly-back converters with two separated transformers. Because of the interleaved operation the converter can approximately share resultant load current between the secondary’s of the two transformers due to which the transformer conductive losses and the rectifier diodes conduction losses can be decreased. These methods enhance conversion efficiency by cutting on the switching loss of high frequency active switches. Recently, two identical or different converters are combined together to form a new converter which is soft-switched providing high efficiency. These attempts are also implemented on Fly-back converters. Transformer pair is series-connected to form an active-clamped Fly-back converter. In addition, interleaved operation is carried out on Fly-back converters. Interleaved operation of this topology is done to reduce the current ripple and the current balancing between paralleled converters is considered. An interleaved active-clamping converter though requires four switches and diodes and higher magnetic component count including transformers and inductors, which increases the circuit complexity and cost [11]-[14]. The DC offset current of an active clamp Fly-back converter deteriorates the transformer utilization and increases transformer size resulting in low power rating of the converter. The power losses and stress on the switching devices can be evenly altered by paralleling two or more converters. Interleaved structures can significantly reduce output current ripple, reducing the output inductance and capacitance to half its value for the same output rating. This paper also proposes an interleaved Fly-back converter. Two Fly-back converters are connected in parallel at input and output ports in addition to an auxiliary inductor with two rectifying diodes for each converter. Thus both the active switches are operated with ZVS, while the rectifying diodes are smoothly moved out of conduction to provide reduced reverse-recovery loss. To extend the power output range in converters Burst-mode control scheme is implemented[15]. The operation principle and design details are described in the proceeding sections. Key Words: Active clamping circuit (ACC), Forward-Flyback converter (FF), interleaved converter, Zero-voltage switching (ZVS) I. INTRODUCTION Forward and Fly-back converters are widely used in power industry because of their simplicity, low cost and relative efficiency. The transformer in a Fly-back converter isolates the electric supply and stores magnetic energy furnishing circuit isolation and energy transformation. Hard switching operation of forward and Fly-back converters imposes high voltage/current spikes on connected switches because of transformer leakage inductances along with switching losses resulting in lower conversion efficiency. A passiveclamping circuit can assist dissipation of the stored energy in the leakage inductance [2]. In recent years, activeclamping techniques has become popular among both converters types [3]–[13] to absorb the stored energy and to suppress the voltage spikes. In the forward converter, active clamping also completes the energy retuning process. The active-clamping converters thus have a higher efficiency owing to zero-voltage-switching (ZVS) operation of the main switch, which is fulfilled with the help of the auxiliary switch. Fly-back converter though seems to be conservative from the efficiency point of view, yet many applications and circuit modifications presented. Fly-back converters are applied for ac–dc conversion companied by power-factorcorrection function [2]–[4]. Publications dealing with efficiency enhancement of Fly-back converters have been greatly researched [5]–[8]. Synchronous rectification is used to reduce the power loss in the output rectifying diode [5]. An auxiliary switch and additional passive elements to fulfil zero-voltage switching (ZVS) and zero-current switching (ZCS) for the main switch has also been presented [6]-[8]. II CONVERTER SWITCHING TECHNIQUES The difference between the supply voltage and that required by silicon creates a huge drop across the regulator, contributing to switching losses and ultimately limiting the device’s switching frequency. Moreover, limited switching frequency is a drawback because it forces engineers to use larger magnetic and other passive components for filtering circuits, increasing the solution size and working against power density. The technique that enables faster switching frequency at higher input voltage and voltage drop is Zero Voltage Switching (ZVS). This technique, uses pulse width modulation (PWM)-based operation with an additional separate phase to the PWM timing to allow for ZVS operation. ZVS enables the voltage regulator to be soft switched, avoiding the switching losses that are typically incurred during conventional PWM operation and 6 International Journal of Computer and Advanced Engineering Research (IJCAER) Volume 02– Issue 01, February 2015 timing. The effect of using conventional or soft switching technique are explained below: [A] Hard-switching Most contemporary non-isolated buck voltage regulators experiences high-switching losses due to the simultaneous occurrence of high-current and -voltage stress imposed on the regulator’s integrated metal oxide semiconductor fieldeffect transistor (MOSFET) switch during the turn-on and turn-off transitions. These losses increase with switching frequency and input voltage and limit maximum frequency operation, efficiency, and power density. Hard switching occurs during the overlap between voltage and current when switching the MOSFET on and off. Figures 1 illustrate where the switching losses occur. Figure 1: Voltage regulator losses during voltage/current overlap on MOSFET switches The downside of fast switching is an increase in electromagnetic interference (EMI) emanating from the voltage regulator circuitry. One way to minimize EMI effects, while still taking advantage of fast switching to enhance efficiency, is to select a switching regulator that employs an improved hard-switching technique called quasiresonant switching. During quasi-resonant switching shown in figure 2 the MOSFET is turned on when the voltage across drain and source is at a minimum. This allows the device to operate with a more modest rate of change in voltage or current, and thus reduces EMI. Figure 3: Soft-switching MOSFET current and voltage waveform Soft switching (ZVS) can best be defined as conventional PWM power conversion during the MOSFET’s on-time but with ―resonant‖ switching transitions. The technique can be considered PWM power utilizing a constant off-time control which varies the conversion frequency, or on-time to maintain regulation of the output voltage. For a given unit of time, this method is similar to fixed-frequency conversion using an adjustable duty cycle. During the ZVS switch off-time, the regulator’s L-C circuit resonates traversing the voltage across the switch from zero to its peak and back down again to zero when the switch can be reactivated, and lossless ZVS facilitated. The MOSFET transition losses are zero regardless of operating frequency and input voltage representing a significant savings in power, and a substantial improvement in efficiency (Figure 5). Such attributes make ZVS a good technique for highfrequency, high-voltage converter designs. Figure 4: Conventional PWM vs ZVS Two other advantages of ZVS are that it reduces the harmonic spectrum of any EMI and allows higher frequency operation resulting in reduced, easier-to-filter noise and the use of smaller filter components. Figure 2: Quasi-resonant switching waveform for a Flyback converter [B] Soft switching During soft switching the voltage falls to zero before the MOSFET is turned on or off, eliminating any overlap between voltage and current and minimizing losses. An additional advantage is that the smooth switching waveforms minimize EMI. [C] Zero-voltage switching Figure 5 shows a schematic for a ZVS buck topology. This circuit is identical to a conventional buck regulator except for an added clamp switch connected across the output inductor. The switch is added to allow energy stored in the output inductor to be used to implement ZVS. Figure 5: ZVS buck topology 7 International Journal of Computer and Advanced Engineering Research (IJCAER) Volume 02– Issue 01, February 2015 The ZVS buck converter operates in three main states. They are defined as Q1 on phase, Q2 on phase, and clamp phase. Q1 turns on at zero current. Current ramps up in the MOSFET and the output inductor to a peak current. During the Q1 on phase, energy is stored in the output inductor and charge is supplied to the output capacitor. During the Q1 on phase, the power dissipation in Q1 is dominated by MOSFET on-resistance and the switching loss is negligible. Next, Q1 turns off rapidly followed by a very short body diode conduction time (adding negligible power dissipation). Next, Q2 turns on and the energy stored in the output inductor is delivered to the load and output capacitor. When the inductor current reaches zero, the synchronous MOSFET Q2 is held on long enough to store some energy in the output inductor from the output capacitor. Once the controller has determined that there is enough energy stored in the inductor, the synchronous MOSFET turns off and the clamp switch turns on, clamping the VS node to VOUT. When the clamp phase ends, the clamp switch is opened. The energy stored in the output inductor resonates with the parallel combination of the Q1 and Q2 output capacitances, causing the VS node to ring towards VIN. This ring discharges the output capacitance of Q1, diminishes the gate-to-drain (Miller) charge of Q1 and charges the output capacitance of Q2. This allows Q1 to turn on in a lossless manner when the VS node is nearly equal to V IN. III FLY-BACK AND FORWARD TOPOLOGIES The standard topologies of the single switch MOSFET flyback and forward converters are shown in figure 6 and 7, which are best suited for applications at power level below 150 W and dc line voltages below 200 V. Their operating principles are described briefly below. Each topology has advantages and drawbacks, which are compared in Table 1. The transformer of the fly-back is operated in the indirect power transfer mode. When the switch is turned on, a rising current flows through the primary winding, thus energy is stored in the core of the transformer. When the switch is turned off, the dotted end of the secondary winding reverses the voltage polarity. Thus, the rectifier diode is forward biased and the stored energy is transferred to the output via the secondary winding and the rectifier. Periodical switching of the switch will keep the power continuously flowing through input to the output. By modulating the pulse width of each switching signal, the output voltage is regulated. The transformer of the forward is operated in the direct power transfer mode. When the switch is turned on, an amount of energy is transferred to the output via the transformer and the rectifier. When the switch is switched off, the core of the transformer is reset by a tertiary winding. Periodical switching of the switch will keep the power flowing from the input to the output. By modulating the pulse width of each switching signal, the output voltage is regulated. Table 1: Comparison based power levels[16] The fly-back The forward topology topology 1, Simpler circuitry: 1. Less rms and Advantages no output inductor, peak currents, only one rectification 2. Less ripple in the diode in output stage output voltage 2.Simpler 3. Smaller output Transformer structure capacitor needed. 3. Better regulation of outputs against load variations in multi outputs applications. 1. Output inductor Drawbacks 1. Higher RMS and peak currents and two more 2. Larger ripples in diodes are needed, the output voltage 2. Additional 3.Bigger output winding set of capacitor needed power transformer needed to reset core, 3. Poor regulation of outputs against the Ioad variations Figure 7 : Forward converter topology IV. INTERLEAVED ZVS FLY-BACK CONVERTER The two paralleled Fly-back converters of an interleaved fly back ZVS converter are composed of MOSFET switches, transformers, and rectifying diodes. The components of both the converters are assumed to be identical. Two Fly-back converters are operated at tandem to energize the output load with just one extra inductor Ls, to fulfill the requirements of ZVS. Figure 6: Fly-back converter topology 8 International Journal of Computer and Advanced Engineering Research (IJCAER) Volume 02– Issue 01, February 2015 Figure 8 : Interleaved Fly-back converter with ZVS.[15] Certain simplifying assumptions can be made for the above shown circuit, such as The forward voltage drops on MOSFET S1-S2 and diodes D1 D2 are neglected, The output capacitor Co is large such that voltage ripple is negligible, Both the transformers have large magnetizing inductances Lm1 and Lm2 such that currents ILm1 and ILm2 can be approximated to be constants, Output capacitances of MOSFETs, CS1 = CS2 = Cs . V. CONVERTER OPERATION The circuit operation can be divided into eight modes. The former four modes define the ON state to turn-OFF transient of S1 , while S2 undergoes OFF-state to zero-voltage turnON transition. The latter four modes are similar counterpart with the interchanged roles of S1 and S2 . They are detailed as followed. Mode I [t0 < t < t1]: At t0 , voltage across S2 , vDS1 , rises up to nVin + Vo and turns diode D2 ON, which causes the current originally flowing through S2 detours to D2 and energize the load. During Mode I, both S1 and D2 are in conduction state, thus inductor Ls will bear a voltage of nVin + Vo, which makes current iLs to linearly decrease at a slope of (nVin + Vo )/Ls and linearly increase of iS1 . As iLs falls down to zero, ILm1 passes through S1 thoroughly. From this moment on, iLs reverses. At the end of this mode, iD2 ceases and iS1 is the sum of ILm1 and ILm2 .The current iLs during this mode can be equated as follows: ...(1) Figure 9: Operating modes of Interleaved ZVS fly-back converter Mode II [t1 < t < t2]: Since diode D2 is OFF, capacitance Cs2 is no longer clamped at the voltage level of nVin + Vo . The stored energy in Cs2 is able to be released by the resonance of this capacitance with Ls . When voltage vDS2 resonates to zero, the next mode is entered. The related equations during this mode are listed as follows: ...(2) ...(3) Mode III [t2 < t < t3]: At t2 , voltage vDS2 declines to zero; however, the inductor current iLs does not rest and continues flowing through the anti parallel diode DS2 of S2 . Under the assumption of zero-voltage drops on switches and diodes, the inductor current freewheels through S1 and DS2 . Current iLs is kept constant throughout this mode. It should be noticed that the conduction of DS2 clamps the voltage across S2 at zero level, which provides an adequate interval for ZVS on S2 . The related equations for this mode are as follows: ...(4) ...(5) Mode IV [t3 < t < t4]: At the onset of this mode, switch S1 is turned off, which forces currents iLm1 and iLs to bypass through capacitor CS1 . This bypassing transfers energy from inductors to CS1 and slightly reduces the magnitude of iLs . When voltage vDS1 rises to nVin + Vo , D1 will be forward-biased and initialize the next mode. Current iLs and voltage vDS1 are equated as follows: ..(6)&(7) VI CONTROLLER ARCHITECTURE This controller has several built-in PWM signal generators, whose duty ratio and phase delay can be configured separately. This feature is convenient for interleaving triggering signal generation. Figure6 is the control diagram 9 International Journal of Computer and Advanced Engineering Research (IJCAER) Volume 02– Issue 01, February 2015 of the proposed circuit. The output voltage is divided and low-pass filtered to compare with the preset Vref . The voltage error ve is adapted through a PI control algorithm to obtain the required error-amending control-force signal uv. The load current io is monitored to quickly perceive the load change. Filtered current command io is then imposed upon the control force uv and via frequency mapping into gating signals ga1 and ga2 . suggests that the converter is much superior in performance to the conventional fly-back or forward converter topologies. The converter requires only one additional inductor is needed to obtain the ZVS characteristics. The converter is able to provide high efficiency and low ripple output. Figure 10: Controller Block Diagram VII. DESIGN PARAMETERS To verify the principle of the proposed converter shown in figure 8, a 200w prototype converter parameters are as follows: Load delivering capability= 50W to 600W Input dc voltage range Vin =120-190V Output voltage VO=160 Rated output current IO=1.5A Magnetising inductors Lm1 & Lm2 =840µH Inductors Ls =260 µH Filtering Capacitors Co=470 µF Switching frequency fs=200 kHz Effective duty ratio = 0.6154 Turns ratio n= 76:4 Conversion efficiency = 0.83 to 0.91 Figure 11: Device Voltages & Current Waveforms VII. THEORETICAL WAVEFORMS The fly-back converter topology discussed in sections IV to VII shall provide least possible ripple content for a much higher voltage rating. The theoretical waveforms for the device voltages and currents have been shown in Figure 11. Also the converter efficiency variation pattern is also shown in figure 12, which reveals that the efficiency varies between 83 to 92% for power variations form 50 to 600 watts. VIII. CONCLUSION This paper reviews DC converter switching techniques along with feed forward and fly back topologies of DC converters. An interleaved Fly-back converter with ZVS feature has also been presented in detail with the design equations and reference waveforms. Study presented reveals that the fly back topology provides higher simpler structure, higher voltages with lower ripples and is capable in operating over a wider range of power outputs. Also it is seen that the converter performance is greatly characterised by the switching technique as in the case soft switching is seen to reduce the stresses on switching devices and thus helps in economic selection of converter switch ratings. Apart from this a fly-back converter structure with ZVS is also presented; a detailed study of the shown topology Figure 12: Efficiency vs Output power The circuit can operate over a power range from 50W to 600W. Since this circuit is controlled by varying frequency to track the output power variation, burst-mode control scheme has been embedded into the controller to prevent too high-operation frequency under low-load situation. The highest efficiency obtained by this converter topology is 91% and the least efficient operation too provides about 83% efficiency at very low-power output. REFERENCES [1] M. S. G¨oksu and I. Alan, ―250 W flyback SMPS design for a big size CTV,‖ IEEE Trans. Consum. Electron., vol. 49, no. 4, pp. 911–916, Nov.2003. 10 International Journal of Computer and Advanced Engineering Research (IJCAER) Volume 02– Issue 01, February 2015 [2] Y. C. Chang and C. M. Liaw, ―Design and control for a charge-regulated flyback switch-mode rectifier,‖ IEEE Trans. Power Electron., vol. 24, no. 1, pp. 59–74, Jan. 2009. [3] K. I. Hwu and Y. T. Yau, ―An interleaved AC–DC converter based on current tracking,‖ IEEE Trans. Ind. Electron., vol. 56, no. 5, pp. 1456–1463, May 2009. [4] H. F. Liu and L. K. Chang, ―Flexible and low cost design for a flyback AC/DC converter with harmonic current correction,‖ IEEE Trans. Power Electron., vol. 20, no. 1, pp. 17–24, Jan. 2005. [5] J. J. Lee, J. M. Kwon, E. H. Kim, W. Y. Choi, and B. H. Kwon, ―Singlestage single-switch PFC flyback converter using a synchronous rectifier,‖ IEEE Trans. Ind. Electron., vol. 55, no. 3, pp. 1352–1365, Mar. 2008. [6] B. R. Lin, C. E. Huang, K. Huang, and D. Wang, ―Design and implementation of zero-voltage-switching flyback converter with synchronous rectifier,‖ in Proc. Inst. Elect. Eng.—Electr. Power Appl., vol. 153, no. 3, pp. 428–428, May 2006. [7] E. Adib and H. Farzanehfard, ―Family of zero current zero voltage transition PWM converters,‖ IET Power Electron., vol. 1, no. 2, pp. 144–153, Mar. 2008. [8] C. M. Wang, ―A novel ZCS-PWM flyback converter with a simple ZCSPWM commutation cell,‖ IEEE Trans. Ind. Electron., vol. 55, no. 2, pp. 749–757, Feb. 2008. [9] Y. C. Hsieh, T. C. Hsueh, and H. C. Yen, ―An interleaved boost converter with zero voltage transition,‖ IEEE Trans. Power Electron., vol. 24, no. 4, pp. 973–978, Apr. 2009. [10] W. H. Li and X. N. He, ―A family of isolated interleaved boost and buck converters with winding-crosscoupled inductors,‖ IEEE Trans. Power Electron., vol. 23, no. 6, pp. 3164–3173, Nov. 2008. [11] Y. K. Lo and J.-Y. Lin, ―Active-clamping ZVS flyback converter employing two transformers,‖ IEEE Trans. Power Electron., vol. 22, no. 6, pp. 2416–2423, Nov. 2007. [12] B. R. Lin, H. K. Chiang, and C. Y. Cheng, ―Softswitching converter based on bi-flyback topology,‖ Electron. Lett., vol. 44, no. 21, pp. 1272–1274, Oct. 2008. [13] T. Qian and B. Lehman, ―Coupled input-series and output-parallel dual interleaved flyback converter for high input voltage application,‖ IEEE Trans. Power Electron., vol. 23, no. 1, pp. 88–95, Jan. 2008. [14] D. Wang, X. N. He, and J. J. Shi, ―Design and analysis of an interleaved flyback—Forward boost converter with the current autobalance characteristic,‖ IEEE Trans. Power Electron., vol. 25, no. 2, pp. 489–495, Feb. 2010. [15] Yao-Ching Hsieh, Ming-Ren Chen, Hung-Liang Cheng, ―An Interleaved Flyback Converter Featured With Zero-Voltage Transition‖, IEEE Transactions On Power Electronics, Vol. 26, No. 1, pp 79-84, January 2011 [16] Meghdad Taheri, Jafar Milimonfared, Alireza Namadmalan, ―Analysis, Design and Implementation of a New Chokeless Interleaved ZVS Forward-Flyback Converter‖, Journal of Power Electronics, Vol. 11, No. 4, pp 499-506, July 2011 11