EMIF06-SD02F3

6-line IPAD™, EMI filter and ESD protection for SD card

Features

■

ESD protection (IEC standard)

■

EMI Filtering

■

Level translator

■

Signal conditionning

■

Integrated power supply with:

– Thermal shutdown (TSD)

– Under voltage lockout (UVLO)

– Short-circuit current limitation (ISC)

– Power on/off feature with Enable pin.

Benefits

■

EMI Low-pass-filter and ESD protection (up to

15 kV on external pins)

■

Integrated pull up resistors to prevent bus

floating

)

(s

)

s

(

ct

u

d

o

Flip Chip

24 bumps

r

P

e

t

e

l

o

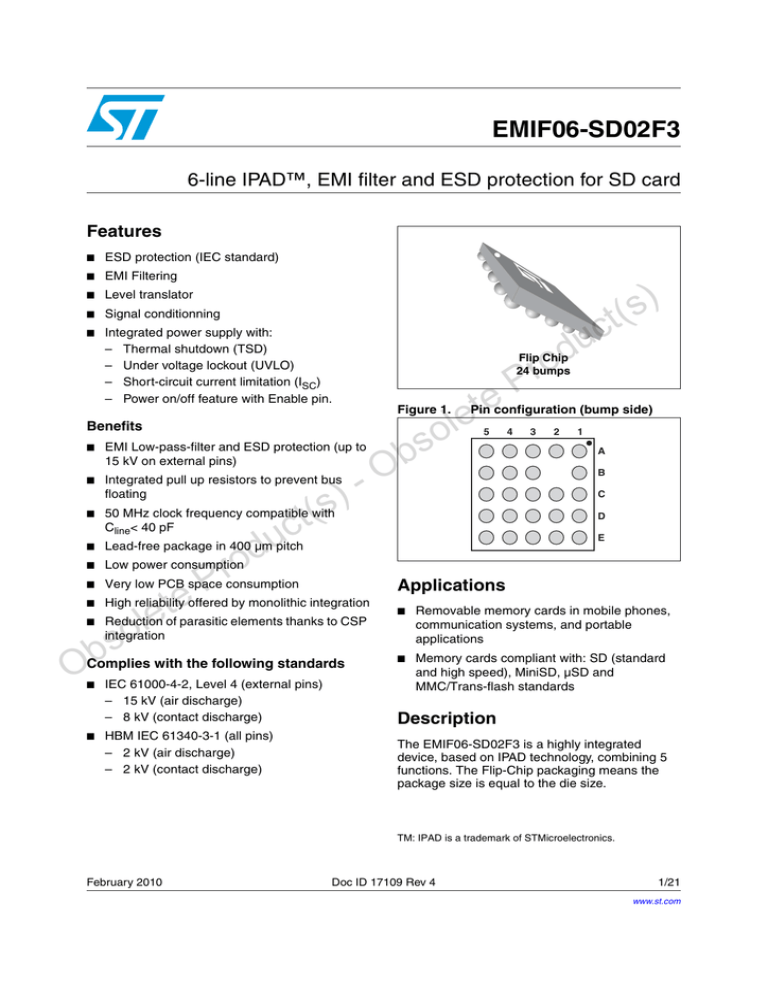

Figure 1.

s

b

O

Pin configuration (bump side)

5

50 MHz clock frequency compatible with

Cline< 40 pF

■

Lead-free package in 400 µm pitch

■

Low power consumption

■

Very low PCB space consumption

■

High reliability offered by monolithic integration

■

Reduction of parasitic elements thanks to CSP

integration

e

t

e

ol

du

o

r

P

s

b

O

IEC 61000-4-2, Level 4 (external pins)

– 15 kV (air discharge)

– 8 kV (contact discharge)

■

HBM IEC 61340-3-1 (all pins)

– 2 kV (air discharge)

– 2 kV (contact discharge)

2

1

A

B

D

E

Applications

Complies with the following standards

■

3

C

ct

■

4

■

Removable memory cards in mobile phones,

communication systems, and portable

applications

■

Memory cards compliant with: SD (standard

and high speed), MiniSD, µSD and

MMC/Trans-flash standards

Description

The EMIF06-SD02F3 is a highly integrated

device, based on IPAD technology, combining 5

functions. The Flip-Chip packaging means the

package size is equal to the die size.

TM: IPAD is a trademark of STMicroelectronics.

February 2010

Doc ID 17109 Rev 4

1/21

www.st.com

21

Contents

EMIF06-SD02F3

Contents

1

Functional description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3

2

Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

3

Passive integration and low pass filter . . . . . . . . . . . . . . . . . . . . . . . . . . 8

4

Data transmission . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

5

)

s

(

ct

4.1

Test circuit from host to SD . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.2

Test circuit from SD to host . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

4.3

Measurement of tskew (SD to host) from rising edge CLK.h . . . . . . . . . . . 12

4.4

Measurement of tskew.f (read mode) from rising edge CLK.h . . . . . . . . . . 12

u

d

o

r

P

e

t

e

l

o

Low drop out voltage regulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

5.1

Line regulation and transient line regulation . . . . . . . . . . . . . . . . . . . . . . . 16

5.2

Load regulation and transient load regulation . . . . . . . . . . . . . . . . . . . . . 17

5.3

Dropout definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

)

(s

s

b

O

6

Ordering information scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

7

Package information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

8

Ordering information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

9

t

c

u

d

o

r

t

e

l

o

s

b

O

2/21

P

e

Revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

Doc ID 17109 Rev 4

EMIF06-SD02F3

1

Functional description

Functional description

A SIDE (Host-CPU) pin list:

VccA, Enable, Dat123.dir, CMD.dir, CMD.h, CLK.h, CLK -f, Dat0.dir, Dat0.h, Dat1.h, Dat2.h,

Dat3.h, Vbat

B SIDE (SD-Card) pin list:

WP, CD, VccB, CMD-B, CLK-B, Dat0-B, Dat1-B, Dat2-B, Dat3-B

Table 1.

Pin definition

Pin Name

Bump

Type

Side

VccA

B3

Power input

A

Power supply (1.8v)

VccB

B4

Power output

B

Power supply (internally generated, 2.9 V)

Vbat

A4

Power input

A

Battery power supply

GND

C4

Ground

-

Ground

GND

C3

Ground

-

Ground

Enable

C2

Input

A

Internal power supply enable

CMD.dir

A2

Input

A

Command direction

CMD.h

D2

IO

A

CLK.h

C1

Input

A

CLK-f

E2

Output

A

Dat0.dir

A3

Input

A

Data direction

Dat0.h

D1

A

Data host

Dat123.dir

E3

u

d

o

Input

A

Data direction

Dat1.h

Clock feedback

Data host

A

Data host

B1

IO

A

Data host

E4

Input to CPU

A

Write protect

CD

D3

Input to CPU

A

Card detect

CMD-B

D4

IO

B

Command direction

CLK-B

C5

Output

B

Clock output

Dat0-B

D5

IO

B

Data SD

Dat1-B

E5

IO

B

Data SD

Dat2-B

A5

IO

B

Data SD

Dat3-B

B5

IO

B

Data SD

e

t

e

l

Note:

Clock input

A

WP

O

A side command

IO

Dat3.h

o

s

b

t

e

l

o

IO

Pr

u

d

o

r

P

e

A1

Dat2.h

E1

IO

)

s

(

ct

bs

O

)

s

(

t

c

Description

In Table 5, 6, 7, and 10, collective names are used for groups of pins. The names used are:

*.dir = CMD.dir, Dat0.dir, Dat123.dir

*.h = CMD.h, CLK.h, Dat0.h, Dat1.h, Dat2.h, Dat3.h

*-B = CMD-B, CLK-B, Dat0-B, Dat1-B, Dat2-B, Dat3-B

ViA = All A side input pins

ViB = All B side input pins.

Doc ID 17109 Rev 4

3/21

Functional description

Table 2.

EMIF06-SD02F3

Function table

Command signals

A side signals direction

B side signal direction

Dat1.h

Enable

CMD. dir Dat0.dir Dat123.dir CMD.h

CLK.h

CLK-f

Dat0.h

Dat2.h

Dat1-B

CMD-B CLK-B

Dat0-B

Dat3.h

Dat2-B

Dat3-B

H

H

X

X

IN

IN

OUT

X

X

OUT

OUT

X

X

H

L

X

X

OUT

IN

OUT

X

X

IN

OUT

X

X

H

X

H

X

X

IN

OUT

IN

X

X

OUT

OUT

X

H

X

L

X

X

IN

OUT

OUT

X

X

OUT

IN

X

H

X

X

H

X

IN

OUT

X

IN

X

OUT

H

X

X

L

X

IN

OUT

X

OUT

X

OUT

L

X

X

X

X

X

Z

X

X

L*

Note:

)

s

(

ct

u

d

o

Z

X

OUT

X

IN

L*

L*

1

When A side signals direction is INPUT, SD-CARD is WRITTEN by CPU-Host (i.e B side

signals direction is OUTPUT)

When A side signals direction is OUTPUT, SD-CARD is READ by CPU-Host (i.e B side

signals direction is INPUT)

2

For B side signals when Enable = L:

* Defined by internal pull-down (cf Block Diagram for pins CMD.B and data bus Dat[0…3].B)

r

P

e

Figure 2.

t

e

l

o

Configuration

)

(s

s

b

O

VccA 1.8 V

Vbat

t

c

u

od

Pr

IPAD

Feedback Clk

CMD

ete

l

o

s

b

O

4/21

Low drop out

voltage regulator

VccB

CMD Dir

ESD

2 kV

CPU

Dir0

Dir1-3

Clk

Clk

CMD

Data 0 - 3

WP, CD

Doc ID 17109 Rev 4

CMD

ESD (15 kV)

and EMI

Data 0 - 3

Mini

SD

EMIF06-SD02F3

Functional description

Figure 3.

Block diagram

Vbat

VccA

VccA

VCCA

15KV

2

kV

LDO

V

REF

VREF

2KV

2

kV

A

Enable

2KV

2

kV

VccB

VCCB

VccB

R,C

500

500KW

kΩ

15 kV

15KV

REN

VccA

VCCA

CMD.dir

REF

VccB

VCCB

OTP

UVLO

)

s

(

ct

VccB

VCCB

2KV

2

kV

R9

15KW

15

kΩ

du

CMD.h

2KV

2

kV

CLK.h

ro

CLK-f

2KV

2

kV

Dat0.dir

so

2KV

2

kV

)-

Dat0.h

2KV

2

kV

b

O

s

(

t

c

Dat123.dir

P

e

let

2KV

2

kV

VccB

VCCB

R10

CMD-B

15 kV

15KV

CLK-B

15 kV

15KV

EMI

Filters

70KW

70

kΩ

Dat0-B

15 kV

15KV

VccB

VCCB

2KV

2

kV

u

d

o

Dat1.h

e

t

e

ol

bs

2KV

2

kV

Pr

R11

70KW

70

kΩ

Dat1-B

VccB

VCCB

R12

15 kV

15KV

70KW

70

kΩ

Dat2.h

Dat2-B

2KV

2

kV

15 kV

15KV

Dat3.h

Dat3-B

2KV

2kV

O

R7

VccA

VCCA

R14

470KW

470k

Ω

15KV

15

kV

VccA

VCCA

Level-Shifters

Level-shifters

-

100KW

100k

Ω

R13

100KW

100

kΩ

WP

CD

15KV

15kV

15KV

15

kV

EMIF06

EMIF06 -SD02F3

SD02F3

GND

Doc ID 17109 Rev 4

5/21

Characteristics

EMIF06-SD02F3

2

Characteristics

Table 3.

Absolute maximum ratings

Symbol

Parameter

Value

A SIDE (Host-CPU)

All pins: HBM IEC61340-3-1

VccA, Enable, Dat123.dir, CMD.dir, CMD.h, CLK.h,

CLK -f, Dat0.dir, Dat0.h, Dat1.h, Dat2.h, Dat3.h, Vbat

Air discharge

Contact discharge

2

2

ESD

kV

B SIDE (SD-Card)

External pins : IEC 61000-4-2, level 4

VccB, CMD-B, CLK-B, Dat0-B, Dat1-B, Dat2-B,

Dat3-B, WP, CD

Tjmax

Rth (j-a) (1)

Pdmax

Tstg

Air discharge

Contact discharge

Thermal resistance from junction to ambient

Board: epoxy FR4, copper thickness = 40 µm, 4 layers

e

t

e

l

Maximum power dissipation:

Pdmax= (Tjmax - Taopmax)/ Rth (j-a)

so

Vbat, VccB, Enable

b

O

CMD-B, CLK-B, Dat0-B, Dat1-B, Dat2-B, Dat3-B

)-

VccA

s

(

t

c

Dat123.dir, CMD.dir, CMD.h, CLK.h, CLK -f, Dat0.dir,

Dat0.h, Dat1.h, Dat2.h, Dat3.h, WP, CD

u

d

o

)

s

(

ct

15

8

u

d

o

Maximum junction temperature

Storage temperature range

Voltage

Unit

Pr

150

°C

64

°C/W

1

W

-55 to +150

°C

-0.3 to 5.5

-0.3 to VccB + 0.3

-0.3 to 3.3

V

-0.3 to VccA+0.3

1. VccB is an internally generated power supply, no external voltage should be applied on this pin other than a current clamp.

The thermal resistance depends on printed circuit board layout. To dissipate the heat efficiently away from Flip Chip

bumps, it is better to make copper planes the largest possible as well as considering thermal vias usage.

r

P

e

t

e

l

o

s

b

O

6/21

Doc ID 17109 Rev 4

EMIF06-SD02F3

Table 4.

Characteristics

Recommended operating conditions

Symbol

Parameter

Conditions

Min.

Typ.

Max.

Unit

1.8

1.92

V

5

V

200

mA

VccA

Power supply

1.62

Vbat

Battery power supply

3.1

Iout

VccB output current

0.10

Cbat

External battery

capacitance

Ceramic capacitor

Cout(1)

External output

capacitance

Ta = -40 °C to +85 °C, Vbias = 0 V to 3.3 V

Multi-layer ceramic capacitor type like:

C20RX7R1C225K

ESR(2)

Equivalent series

resistance for Cout

F = 1 Hz to 10 MHz

Multi-layer ceramic capacitor type like:

C20RX7R1C225K

Taop

Ambient operating

temperature

Tjop

Juntion operating

temperature

Pdop

Maximum power

dissipation

Enable

Enable input voltage

Internal pins

(except

Enable, with

WP and CD)

WP, CD, Dat123.dir,

CMD.dir, CMD.h,

CLK.h,

CLK-f, Dat0.dir,

Dat0.h, Dat1.h,

Dat2.h, Dat3.h

2.20

2.20

0

3

-30

u

d

o

bs

O

)

s

(

t

c

u

d

o

3.0

(+35%)

µF

)

s

(

ct

200

mΩ

85

°C

125

°C

625

mW

0

VccA

V

0

VccB

V

0

VccA

V

r

P

e

t

e

l

o

Pdop = (Tjop - Taop)/Rth (j-a)

µF

1.4

(-35%)

-30

External

CMD-B, CLK-B, Dat0pins (without B, Dat1-B,

WP and CD) Dat2-B, Dat3-B

100

25

25

r

P

e

t

e

l

o

1. Cout = 2.2 µF is minimum allowable capacitance value to guarantee LDO stability

2. Values for ESR include the VccB - Cout resistance path and Cout - GND resistance path. These resistance paths need to be

minimized in PCB design.

s

b

O

Doc ID 17109 Rev 4

7/21

Passive integration and low pass filter

Table 5.

EMIF06-SD02F3

LDO - Current levels in recommended operating conditions

Symbol

Test conditions(1)

Parameter

Quiescent current consumption

IccA_OFF

VEN = 0.4 V, Vbat = 3.4 V, VccA = 1.92 V

*.dir, *.h, *-B = GND, WP = CD = VccA

All other pins floating

1

µA

Quiescent current consumption

Ibat_OFF

VEN = 0.4 V, Vbat = 5 V, VccA = 1.92 V

*.dir, *.h, *-B = GND

All other pins floating

1

µA

160

220

µA

Quiescent current consumption

(Ground pin current) Ibat + IccA

Iout = 100 µA

Level shifter disactivated

Iout = 50 mA

*.dir = 0 V, Vbat = 3.4 V

VEN = VccA = VCLK.h = 1.8 V I = 100 mA

out

All other pins floating

Iout = 200 mA

320

375

µA

470

550

IQ_OFF

IQ_ON

Min. Typ. Max. Unit

Table 6.

ct

750

u

d

o

1. See Note: on page 3 for definition of collective names of pins, for example *.dir

(s)

900

µA

µA

Level shifter - Current levels in recommended operating conditions

Symbol

r

P

e

Test conditions(1)

Parameter

Min.

let

Typ.

Max.

Unit

IccA_ON

Quiescent current on VccA

VEN = VccA = 1.92 V, Vbat = 3.4 V

*.dir = VccA, ViA = *.h = VccA

3

10

µA

IccB_ON

Quiescent current on VccB

VEN = VccA = 1.92 V, Vbat = 3.4 V

*.dir = 0 V, VccB = 3.05 V, ViB = VccB

15

30

µA

o

s

b

O

)

1. See Note: on page 3 for definition of collective names of pins, for example *.dir

s

(

t

c

3

Passive integration and low pass filter

Figure 4.

Circuit diagram of EMIF06-SD02F3 (without LDO)

u

d

o

r

P

e

R14

R13

VccA

CLK.h

CMD.h

Data0.h

Data1.h

Data2.h

Data3.h

Enable

R12

R10

R11

s

b

O

level

Shifter

Host side

R9

t

e

l

o

VccB

Card side

ESD

2 kV

R3

R4

R5

R6

15 kV

R7

ESD 15 kV

REN

ESD 15 kV

WP

CD

15 kV

15 kV

G ND

GND

Note:

8/21

CLK B

CMD B

Data0 B

Data1 B

Data2 B

Data3 B

R1

R2

15 kV

G ND

GND

VBR in 14 V technology for pins: CMD-B, CLK-B, Dat0-B, Dat1-B, Dat2-B, Dat3-B, WP, CD

VBR in 8 V technology for pins: Vcc-B, CLK.h, CLK-f, CMD.h, Dat0.h, Dat1.h, Dat2.h, Dat3.h

Doc ID 17109 Rev 4

EMIF06-SD02F3

Table 7.

Passive integration and low pass filter

Components

Symbol

Test conditions(1)

Parameter

Min.

Typ. Max.

Unit

Cin-A

Input capacitance for A Vbat = 3.4 V, *.dir = VEN = VccA

side

F = 1 MHz, Vdc = 0 V, ±30 mV, VAC = 30mV

5

35

pF

Cin-B

Input capacitance for B Vbat = 3.4 V, *.dir = GND, VEN = VccA

side

F = 1 MHz, Vdc = 0 V, ±30 mV, VAC = 30mV

25

35

pF

CEMIF

Capacitance seen on

B side from EMIF filter

15

pF

40

Ω

R1, R2, R3, R4,

EMIF resistors(3)

R5, R6(2)

Rline

Tj = 25 °C

Line resistance

(4)

at 20 mA

40

50

70

Tj = 25 °C

49

R9

EMIF resistor

(4)

Tj = 25 °C

10.5

15

R7

EMIF resistor(4)

Tj = 25 °C

329

470

(4)

Tj = 25 °C

(4)

R10, R11, R12 EMIF resistors

R13

EMIF resistor

R14

EMIF resistor

Tj = 25 °C

REN

Resistor(4)

Tj = 25 °C

e

t

e

ol

Ω

91

kΩ

19.5

kΩ

611

kΩ

)

s

(

t

c

u

d

o

r

P

60

70

100

130

kΩ

70

100

130

kΩ

500

kΩ

1. See Note: on page 3 for definition of collective names of pins, for example *.dir

2.

These values are guaranteed by design and statistical process control.

3. 20% tolerance in resistance value

4. 30% tolerance in resistance value

)-

Figure 5.

Frequency response with level

shifters internally bypassed(1)

s

(

t

c

dB

u

d

o

0.00

- 5.00

so

- 20.00

b

O

dB

0.00

- 60.00

- 80.00

- 25.00

- 100.00

F (Hz)

F (Hz)

- 30.00

100.0k

Crosstalk response with level

shifters internally bypassed(1)

- 40.00

let

- 15.00

Figure 6.

- 20.00

r

P

e

- 10.00

s

b

O

1.0M

10.0M

100.0M

f/Hz

a1- a5

c1 - c5

e1- e5

1.0G

- 120.00

100.0k

b1- b5

d1- d5

1.0M

a1- b5

d1- e5

10.0M

100.0M

1.0G

c1 - d5

1. Measurement in 50 Ω environment

Doc ID 17109 Rev 4

9/21

Data transmission

4

EMIF06-SD02F3

Data transmission

All values in the tables below are guaranteed across the operating temperature and voltage

range unless otherwise specified.

Table 8.

DC voltage levels on host side

Symbol

Parameter

VIHA

Test

conditions

Min.

Typ.

High level input voltage

0.65 x VccA

VccA

VILA

Low level input voltage

0

0

VOHA

High level output

voltage

VOLA

Low level output voltage

Table 9.

Ioh = -6 mA

VILB

Low level input voltage

VOHB

High level output voltage

VOLB

Low voltage output voltage

s

(

t

c

)-

Min.

e

t

e

ol

du

s

b

O

0.45

o

r

P

0.7 x VccB(1)

Ioh = -8 mA

V

)

s

(

ct

0

High level input voltage

VIHB

0.35 x VccA

V

Iol = 7 mA

Test

conditions

Parameter

Unit

V

VccA - 0.45

DC voltage levels on SD side

Symbol

Max.

Typ.

V

Max.

Unit

VccB

VccB(1) - 0.7

Iol = 8 mA

0

V

0.3 x VccB

(1)

2.9

0

V

V

0.7

V

1. VccB is defined in power supply block.

Table 10.

Symbol

o

r

P

Test conditions(1)

5

µA

ILSD

Leakage current on

SD pin

Vbat = 3.4 V, VCLK.h = VccA,

VCMD = VDat0 = VDat1 = VDat2 = VccB

VDat3 = *.dir = GND

5

µA

ISCH

Short circuit current

on host side

SD input = H, host = 0 V

SD input = 0 V, host = VccA = 1.8 V

*.dir = 0 V, Vbat = 3.4 V, Tj = 25 °C

25

mA

ISCSD

Short circuit current

on SD side

Host input = H, SD = 0 V

Host input= L, SD = VccB, Tj = 25 °C

*.dir = VccA = 1.8 V, Vbat = 3.4 V

60

mA

1. See Note: on page 3 for definition of collective names of pins, for example *.dir

10/21

Min. Typ. Max. Unit

VEN = *.dir = VccA = 1.92 V,

ViA = VccA or GND, Vbat = 3.4 V

ete

b

O

du

Parameter

Leakage current on

host pin

ILH

l

o

s

DC current levels

Doc ID 17109 Rev 4

EMIF06-SD02F3

Data transmission

Figure 7.

Symbol definitions of tplh, tphl, tr and tf for AC characteristics in Table 11

VccA or VccB

INPUT

50%

50%

0V

tphl

tplh

70%

VccA or VccB

70%

50%

OUTPUT 20%

50%

20%

0V

tr

Table 11.

tf

AC characteristics

Symbol

Parameter

tphl

Propagation delay hl from host to SD

tplh

Propagation delay lh from host to SD

tphl

Propagation delay hl from SD to host

tplh

Propagation delay lh from SD to host

tr

Test conditions

Section 4.2

3.5

7

3.5

7

Pr

3

7

3

7

1.5

3

ns

ns

Rise time from host to SD

Section 4.1

Rise time from SD to host

Section 4.2

0.5

3

Section 4.1

1.9

3

Section 4.2

0.5

3

O

)

Fall time from SD to host

Delay differences from host to SD

tskew.f

tskew delay from SD to host

tp_clkf

Propagation delay for CLK feedback

tr_clkf

Rise time for CLK feedback

od

Pr

t(s

uc

ns

o

s

b

tskew

tf_clkf

e

t

e

l

)

s

(

ct

Typ Max Unit

u

d

o

Section 4.1

Fall time from host to SD

tf

Min

Fall time for CLK feedback

ns

Section 4.1 Section 4.3

-1.5

0

1.5

ns

Section 4.2 Section 4.4

-1.5

0

1.5

ns

6.5

14

ns

Section 4.2

0.5

3

ns

Section 4.2

0.5

3

ns

e circuit from host to SD

Test

t

e

ol

4.1

s

b

O

Test circuit from host to SD is shown in Figure 8. Timings are measured for the whole line cell (shifter

+ EMI + ESD) on an external load Csd = 15 pF (board capacitance 5 pF + SD card capacitance 10 pF).

4.2

Test circuit from SD to host

Test circuit from SD to host is shown in Figure 9. Timings are measured for the whole line cell (shifter

+ EMI + ESD) on an external load Chost = 5 pF (board capacitance + host capacitance).

Figure 8.

Test circuit from host to SD

HOST

Figure 9.

Test circuit from SD to host

HOST

SD

Csd =15 pF

SD

Chost = 5 pF

Doc ID 17109 Rev 4

11/21

Data transmission

4.3

EMIF06-SD02F3

Measurement of tskew (SD to host) from rising edge CLK.h

Figure 10. Example of measurement of tskew (SD to host) from rising edge CLK.h

CLK.h

CLK-B

15pF

CLK.f

DAT.dir = « 1 »

Dat-B

DAT.h

15pF

CPU

EMIF06-SD02F3

MiniSD card

tskew= Tp(CLK.h CLK -B) - Tp(Datx.h Datx-B)

VccA

Dat.h

50%

0V

Tp(Datx.h Datx -B)

)

s

(

ct

VccB

50%

Dat x- B

u

d

o

0V

VccA

CLK.h

50%

r

P

e

0V

Tp(CLK.h

CLK -B)

VccB

let

50%

CLK -B

0V

4.4

o

s

(read b

mode) from rising edge CLK.h

O

)

Measurement of tskew.f

Figure 11. Example of measurement of tskew.f (read mode) from rising edge CLK.h

s

(

t

c

CLK.h

u

d

o

e

t

e

l

o

s

b

O

Pr

CLK-B

delay

CLK.f

15pF

DAT.dir = « 0 »

5pF

Dat-B

DAT.h

5pF

CPU

EMIF06-SD02F3

CLK.f ) – [ Tp(CLK.h

tskew.f = Tp (CLK.h

MiniSD card

CLK -B) + Tp(Datx-B Datx.h)]

VccA

CLK.h

50%

0V

Tp(CLK.h

CLK -B)

VccB

CLK -B

50%

0V

VccB

50%

Datx-B

0V

Tp(Datx-B Datx .h)

VccA

Datx .h

50%

0V

Tp ( CLK.h

CLK. f )

VccA

50%

CLK. f

0V

Datx.h = Dat0.h, Dat1.h, Dat2.h, Dat3.h, CMD.h

Datx-B = Dat0-B, Dat1-B, Dat2-B, Dat3-B, CMD.B

12/21

Doc ID 17109 Rev 4

EMIF06-SD02F3

5

Low drop out voltage regulator

Low drop out voltage regulator

Figure 12. Low drop out voltage regulator schematic

Power

Management

ASIC

VBAT

V

bat

VCCA

V

ccA

CBAT

C

bat

BAT

CVCCA

C

VccA

VCCA

V

ccA

VBAT

V

bat

2kV

2

kV

vref

V

ref

UVLO

)

s

(

ct

+

A

TSD

Base Band

ASIC

VEN

VEN

V

VCCA

ccA

EN

LOGIC

Level

LS

Shifter

ro

R,C

15kV

15

kV

2kV

2 kV

REN

P

e

Req = 135 Ω

500 kΩ

t

e

l

o

EMIF06-SD02F3 (LDO part only)

Gnd

GND

)

(s

du

VCCB

VccB

V

VBAT

bat

GND

Gnd

VCCB

VccB

COUT

C

out

Mini-SD

Card

s

b

O

t

c

u

d

o

r

P

e

t

e

l

o

s

b

O

Doc ID 17109 Rev 4

13/21

Low drop out voltage regulator

Table 12.

Static parameters, VEN = VccA unless otherwise specified, level shifter disactivated,

*.dir = 0, CLK.h = VccA , all other pins floating

Symbol

Vout

EMIF06-SD02F3

Parameter

Test conditions

Regulated output

voltage (VccB)

Min.

Typ.

Max.

Unit

Vbat = 3.4 V

Iout = 100 mA

Tj = 25 °C

2.81

(-3%)

2.90

2.99

(+3%)

V

Vbat = 3.4 V

Iout = 100 mA

Tj = -30 to 125 °C

2.81

(-3%)

2.99

(+3%)

V

Vbat = 3.1 to 5 V

Iout = 0.1 to 200 mA

Tj = -30 to 125 °C

2.75

(-5%)

3.05

(+5%)

V

LiR

Line regulation

Vbat = 3.4 to 5 V (Section 5.1)

Iout = 100 mA

Tj = 25 °C

LdR

Load regulation

Vbat = 3.4 V

Iout = 1 to 200 mA (Section 5.2)

Tj = 25 °C

VDO

ISC

TSD

Dropout voltage

Short circuit current

limitation

UVLO

14/21

Pr

Thermal shutdown

temperature

e

t

e

l

Under voltage lockout

)

(s

Vbat = 5 V

Vout = 0 V

Tj = 25 °C

t

c

u

od

so

b

O

Vout(nom) - 100 mV

(Section 5.3)

Tj = -30 to 85 °C

Vbat = 3.4 V

Tj = -30 to 125 °C

(s)

3

t

c

u

20

mV

50

100

mV

Iout = 50 mA

25

37

mV

Iout = 100 mA

50

75

mV

Iout = 200 mA

100

150

mV

d

o

r

P

e

t

e

l

o

s

b

O

500

mA

Shutdown

(Temp ↑)

150

°C

Reset

(Temp ↓)

130

°C

Hysteresis

20

°C

Shutdown

(Vbat ↓)

2.3

2.5

2.7

V

Reset

(Vbat ↑)

2.35

2.55

2.75

V

Hysteresis

Doc ID 17109 Rev 4

50

mV

EMIF06-SD02F3

Table 13.

Low drop out voltage regulator

Dynamic parameters (VEN = VccA unless otherwise specified)

Symbol

Parameter

Test conditions

Min. Typ. Max. Unit

LiTr

Line transient peak voltage

Vbat = 3.4 V ↑↓ 4 V, ttr = 30 µs, Iout = 200 mA

Tj = 25 °C (Section 5.1)

Cout = 2.2 µF, ESR = 5 mΩ

LdTr

Load transient peak voltage

Iout = 1 mA ↑↓ 200 mA, ttr = 10 µs, Vbat = 3.4 V

Tj = 25 °C (Section 5.2)

Cout = 2.2 µF, ESR = 5 mΩ

Power supply rejection ratio

Vbat = 3.4 V

Iout = 100 mA

Tj = 25 °C

Cout = 2.2 µF, ESR = 5 mΩ

PSRR

Tstart

Tstop

F = 1 kHz

Vout ↑ 95% Nom, Vbat = 5 V, Iout = 200 mA

Tj = -30 °C to 125 °C

Cout = 2.2 µF, Enable L → H

Discharge time

Vout ↓ 10% Nom, Vbat = 3.4 V, Iout = 1 mA

Tj = 25 °C

Cout = 2.2 µF, Enable H → L

ete

mV

9

mV

45

db

)

s

(

t

35

F = 10 kHz

Settling time

4.2

o

r

P

c

u

d

30

600

db

200

µs

µs

l

o

s

)

(s

b

O

t

c

u

d

o

r

P

e

t

e

l

o

s

b

O

Doc ID 17109 Rev 4

15/21

Low drop out voltage regulator

5.1

EMIF06-SD02F3

Line regulation and transient line regulation

The line regulation (LiR) is a static variable that indicates the change in the output voltage of

the voltage controller ΔVout (at constant load) when there is a change ΔVbat at the input

voltage. By contrast the line transient response (LiTr) represents dynamic peak value to be

observed during the change in input voltage.

Thermal effects due to changes in the junction temperature are circumvented with pulsed

voltage during the test and are to be taken into account separately.

Figure 13 shows the boundary conditions for trise, tfall, and ΔVbat to be taken as the basis of

the measurement of the line transient response without additional decoupling of the supply

voltage by a buffer capacity Cbat. The values defined in the specification apply, however,

only in the case of decoupling of the supply voltage with such a capacity Cbat, as a result of

which the values for trise and tfall are influenced to some extent.

)

s

(

ct

Figure 13. Line regulation and transient line regulation

Vbat

Static and dynamic line regulation

r

P

e

VbatH

t

e

l

o

VbatL

trise = ttr

Vout

tfall = ttr

s

b

O

Vrise

)

(s

LiR

u

d

o

Time

Vfall

Time

Line Regulation: LiR=f(VbatH,VbatL)

Line Transient: LiTr = MAX( Vrise, Vfall) –LiR(VbatH,VbatL)

od

t

c

u

r

P

e

t

e

l

o

Transient line regulation measurement

Typcial values at 25° C

Vbat

4V

X: 0.2 ms/div

Y: 100 mV/div

3.4 V

Vout

X: 0.2 ms/div

Y: 4 mV/div

s

b

O

5

Line regulation (LiR) and Line transient (LiTr)

versus temperature (typical values

4

3

LiR (mV)

LiTr (mV)

2

1

0

-10

16/21

25

Doc ID 17109 Rev 4

85

Temperature ( °c)

EMIF06-SD02F3

5.2

Low drop out voltage regulator

Load regulation and transient load regulation

The load regulation (LdR) is a static variable that indicates the change in output voltage of

the voltage controllor ΔVout (at constant input voltage) in the event of a change in the load

current ΔIout. By contrast the load transient response (LdTr) represents the dynamic peak

value to be observed during load variation.

Thermal effects due to changes in the junction temperature are circumvented by testing with

pulsed load and are to be taken into account separately.

The figure shows the boundary conditions for trise, tfall, and ΔIout to be taken as the basis for

the measurement of the load transient response.

Figure 14. Load regulation and transient load regulation

Iout

)

s

(

ct

Static and dynamic load regulation

IoutH

IoutL

r

P

e

tfall = ttr

trise = ttr

Vout

Vrise

)

(s

u

d

o

t

e

l

o

LdR

s

b

O

Vfall

Load Regulation: LdR=f(IoutH,IoutL)

Load Transient: LdTr = MAX( Vrise, Vfall) –LdR(IoutH,IoutL)

t

c

u

X: 50µs/div

Y: 50mA/div

d

o

r

t

e

l

o

Time

Transient load regulation measurement

(typical values at 25° C)

Iout

P

e

Time

Vccb

s

b

O

X: 50µs/div

Y: 10mV/div

Load regulation (LdR) and Load transient (LdTr)

versus temperature (typical values

60

50

40

LdR (mV)

LdTr (mV)

30

20

10

0

-10

25

Doc ID 17109 Rev 4

85

Temperature ( °c)

17/21

Ordering information scheme

5.3

EMIF06-SD02F3

Dropout definition

The dropout voltage (VDO) is measured by decreasing the input voltage till the output voltage will drop

by 100 mV compared to the output voltage measured at the specified minimum supply voltage (3.1 V).

Worst case for dropout is maximum die temperature and maximum current load. This is done statically.

Figure 15. Dropout definition

V(Vout)

V(Vbat)

3.100e+00

2.888e+00

)

s

(

ct

2.873e+00

VDO

u

d

o

100 mV

2.772e+00

r

P

e

2.888e+00

-2.122e-01

3.100e+00

Base

6

t

e

l

o

s

b

O

Ordering information scheme

)

(s

Figure 16. Ordering information scheme

t

c

u

d

o

r

P

e

t

e

l

o

s

b

O

EMI filter

Number of lines

Information

x = resistance value (ohm)

z = capacitance value / 10 (pF)

or

2 letters = application

2 digits = version

Package

F = Flip Chip

3 = Lead-free, pitch = 400 µm

18/21

Doc ID 17109 Rev 4

EMIF

yy

-

xx zz

F3

EMIF06-SD02F3

7

Package information

Package information

In order to meet environmental requirements, ST offers these devices in different grades of

ECOPACK® packages, depending on their level of environmental compliance. ECOPACK®

specifications, grade definitions and product status are available at: www.st.com.

ECOPACK® is an ST trademark.

400 µm ± 40

475 µm

)

(s

ct

u

d

o

r

P

e

Solder mask opening:

300µm minimum

)

s

(

ct

u

d

o

r

P

e

t

e

l

o

2.55 mm ± 30 µm

Figure 18. Footprint recommendations

Copper pad Diameter:

220µm recommended

260µm maximum

605 µm ± 55

255 µm± 40

2.55 mm ± 30 µm

475 µm

400 µm ± 40

Figure 17. Flip Chip dimensions

s

b

O

Figure 19. Marking

Dot, ST logo

ECOPACK status

xx = marking

z = manufacturing location

yww = datecode

(y = year

ww = week)

x x z

y ww

t

e

l

o

Solder stencil opening :

220µm recommended

s

b

O

Doc ID 17109 Rev 4

19/21

Ordering information

EMIF06-SD02F3

Figure 20. Flip Chip tape and reel specifications

Dot identifying Pin A1 location

1.75 ± 0.1

Ø 1.55 ± 0.1

4.0 ± 0.1

2.0 ± 0.05

STE

STE

STE

xxz

yww

xxz

yww

xxz

yww

)

s

(

ct

u

d

o

4.0 ± 0.1

2.74

3.5 ± 0.1

8.0 ± 0.3

2.74

0.20 ± 0.02

0.69 ± 0.05

r

P

e

User direction of unreeling

All dimensions in mm

t

e

l

o

8

Ordering information

Table 14.

)

(s

t

c

u

Ordering information

Order code

d

o

r

EMIF06-SD02F3

Note:

s

b

O

Marking

Package

Weight

Base qty

Delivery mode

HF

Flip Chip

7.45 mg

5000

Tape and reel (7”)

P

e

More information is available in the application note :

AN2348 :"Flip Chip : Package description and recommendations for use"

AN1751 : EMI Filters: Recommendations and measurements

t

e

l

o

s

b

O9

Revision history

Table 15.

20/21

Document revision history

Date

Revision

Changes

05-Feb-2007

1

First issue

26-Feb-2007

2

Last corrections.

19-Sep-2007

3

Updated graphic in Section 5.1.

10-Feb-2010

4

Updated pocket depth in Figure 20.

Doc ID 17109 Rev 4

EMIF06-SD02F3

)

s

(

ct

Please Read Carefully:

u

d

o

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries (“ST”) reserve the

right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any

time, without notice.

r

P

e

All ST products are sold pursuant to ST’s terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no

liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

t

e

l

o

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this

document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products

or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such

third party products or services or any intellectual property contained therein.

)

(s

s

b

O

UNLESS OTHERWISE SET FORTH IN ST’S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED

WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS

OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

t

c

u

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT

RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING

APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY,

DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE

GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER’S OWN RISK.

d

o

r

P

e

t

e

l

o

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void

any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any

liability of ST.

s

b

O

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2010 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 17109 Rev 4

21/21