BiCMOS Technology

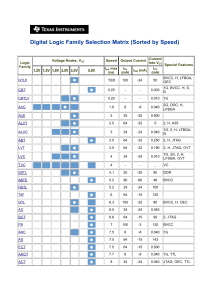

advertisement

BiCMOS Technology Processes, Trends, and Applications Emmanuel A. Gonzalez, E.C.E. gonzaleze@dlsu.edu.ph Department of Electronics and Communications Engineering College of Engineering De La Salle University – Manila, Philippines Technical Report November 29, 2004. Rev. 0 ABSTRACT This paper presents an investigation on the processes, trends, and applications of the BiCMOS technology in the fields of microelectronics and communication electronics. The investigation will focus on the design perspectives and different modifications that were developed to provide a very-high performance BiCMOS integrated circuit for both digital and mixed-signal applications. E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications CHAPTER 1 INTRODUCTION The evolution and adaptation of the microelectronics industry to the BiCMOS technology and its extended families provide a paradigm shift in the development of high-speed, low-power digital and analog integrated circuits. It has been proven in most literatures (see references) that the integration of bipolar and CMOS technologies are advantageous when used in optimized microelectronic circuitry in different applications such as telecommunications, mixed-signal, and radio-frequency microelectronics. However, some problems still arise when it comes to the design of such integrated circuits due to its complexity. Nevertheless, researchers still found ways to solve such problems using different circuit configuration techniques. In this chapter, a review on the bipolar and CMOS technologies is presented, concentrating on their basic properties, features and advantages when applied to microelectronic circuitry. The hybridization of bipolar and CMOS technologies is also discussed in this chapter, showing its effectiveness that causes its emergence, including factors that have driven the addition of bipolar technology to CMOS, resulting into the emergence BiCMOS technology. REVIEW OF BIPOLAR TECHNOLOGY Bipolar transistors are three terminal devices formed by layering alternate n- and p-type regions. The cross-section of its process is shown in Figure 1.1. The three terminals termed as the emitter, base, and collector corresponds to the n+, p, and n sections (i.e. n+ means heavily or highly doped region), for an npn transistor. Current flow relies on the motion of electrons from the emitter n+ region to the collector n-type, which is controlled by the p-type base. Figure 1.1. Cross-section for an integrated NPN bipolar junction transistor. (Source: J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992.) 2 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications BIPOLAR JUNCTION TRANSISTOR SATURATION If both base-to-collector and base-to-emitter junctions are forward biased, the transistor turns into the saturation state, forming a conduction path from the collect to the emitter. A saturated bipolar transistor is usually characterized with the parameters shown in Table 1.1. Table 1.1. Typical parameters for a saturated BJT. VCE , sat ≅ 0.3 V VBE , sat ≅ 0.7 V T = 25 C (room temperature) o However, a saturated bipolar logic can be slow as it stores excess base charge which must be removed to stop conduction. Left on its own, the charge must be diffused before turning off. One method for removing excessive base charge is to use Shottky-clamped transistors which keep the transistor out of saturation, and other is found from the BiCMOS technique, which provides additional circuitry to remove the excess base charge. BIPOLAR JUNCTION TRANSISTOR CUTOFF A bipolar junction transistor is said to be off or “cut-off” when the base-to-emitter and base-to-collector junctions are reverse biased. It this situation, only leakage current flows from collector to emitter. BIPOLAR JUNCTION TRANSISTOR CAPACITANCES Switching characteristics of bipolar transistors are characterized by their parasitic capacitances. For large-signal models, parasitic depletion capacitance such as base-emitter, base-collector, and collector-emitter capacitances are identified. In general, each capacitance is characterized by a zero-bias value which is a function of the junction area and the zero-bias depletion width, as shown in (1.1). Depletion capacitance however is non-linear in nature and also varies with reverse bias voltage depicted in (1.2). The inclusion of the depletion capacitances is important when the junction is in reverse-bias. C0 = C (VR ) = εA D0 C j0 m (1 + VR φ0 ) (1.1) (1.2) Another capacitance exhibited by bipolar transistors is the diffusion capacitance which is important in any forward-biased pn junction. This is due to the fact that diffusion charge carriers 3 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications of opposite polarity give capacitance. Its value is dependent on the forward voltage on the pn junction and the zero-bias value, as depicted in (1.3). The inclusion of the diffusion capacitance is important when the junction is in forward-bias. C ′ = C0 eV φT (1.3) Figure 1.2. Cross-section for an integrated metal-oxide semiconductor transistor. (Source: J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992.) REVIEW OF CMOS TECHNOLOGY The CMOS technology nowadays proved to be the most cost-effective solution for digital circuitry since the birth of the MOS transistor (cross-section shown in Figure 1.2), and the CMOS inverter. One of the main advantages of the CMOS technology is its applications to lowpower microelectronics. However, one trade-off of this technology is its switching speed, which is characterized to be four to five times slower than bipolar transistors. One main reason is its parasitic capacitance that is inherited in the CMOS itself, which is discussed in the next section. MOSFET CAPACITANCES Parasitic capacitances are inherent in MOSFETs which must be accounted in circuit analysis and design. The simplest parasitic capacitance model of a MOSFET is shown in Figure 1.3. Basically these capacitances originate from the gate capacitance, overlap capacitance, depletion capacitance, and channel capacitances. 4 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 1.3. Parasitic capacitances inherited in a MOS transistor. (Source: J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992.) GATE CAPACITANCE The gate capacitance is characterized by the physical separation of the gate metal conductor and the semiconductor by the gate oxide, which is a function of the capacitance per unit area, the channel length and width, as depicted in (1.4). Cg = CoxWL (1.4) OVERLAP CAPACITANCE The overlap capacitance is a parasitic that is measured beyond the normal p-type channel region on both the drain and source sides, which is a function of the overlap length, and is depicted in Figure 1.4 and (1.5). 5 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 1.4. Capacitance estimates. (Source: J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992.) Col = Cox Lo (1.5) GATE OVERHANG CAPACITANCE The gate overhang capacitance is a parasitic that is due to the gate-bulk overlap, which is a function of the gate-bulk overhang width, field-oxide length, and overlap lengths, as depicted in (1.6). Co ,GB = CFOX ( L + 2 Lo ) W0 6 (1.6) E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications DEPLETION CAPACITANCE The depletion capacitance is characterized from the ionized dopants in the vicinity of the junction, and is a function of the reverse-bias voltage. Its variation to reverse-bias voltage is nonlinear in nature. CHANNEL CAPACITANCES Parasitic channel capacitances are as important as the previous parasitics. The important values are for the gate-to-source, gate-to-drain, and gate-to-bulk capacitances, which varies with applied voltage conditions. These values are obtained from a full computer simulation, and is required for characteristics verification. THE EMERGENCE OF BiCMOS TECHNOLOGY A BiCMOS circuit consist of both bipolar junction transistors and MOS transistors on a single substrate, as shown in Figures 1.5 and 1.6. The reason behind the hybridization is to combine the high-speed switching and high-output driving capabilities of the bipolar transistors and the low-power and high-density characteristics of the CMOS circuit. Some of the factors that have driven the addition of bipolar technology for CMOS were discussed by Stogdale, et. al., (Stogdale, 1992) such as enhanced output drive capability, enhanced gate drive capability, specialized analog applications, high-speed logic (especially for ECL-BiCMOS), and power switching capabilities. Figure 1.5. BiCMOS cross-section. (Source: J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992.) 7 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 1.6. BiCMOS cross-section. (Source: J. M Rabaey, Digital Integrated Circuits: A Design Prespective, New Jersey: Prentice-Hall, Inc., 1996.) 8 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications CHAPTER 2 THE BiCMOS INVERTER A CMOS inverter forms the basic circuit for the development of a generalized CMOS logic family, thus, the introduction of BiCMOS inverters forms the same as to the BiCMOS logic circuit family. In this chapter, the discussion on a typical BiCMOS inverter is presented, which will eventually provide as a backgrounder on the concepts of understanding the advantages and disadvantages of BiCMOS inverters in the proceeding chapters. THE BASIC BiCMOS INVERTER AND ITS OPERATION Figure 2.1. A generic BiCMOS inverter. (Source: J. M Rabaey, Digital Integrated Circuits: A Design Prespective, New Jersey: Prentice-Hall, Inc., 1996.) A generic BiCMOS inverter, which also works as a template in the design of BiCMOS circuits, is shown in Figure 2.1. The circuit in Figure 2.1 is composed of a PMOS and NMOS transistor, M2 and M1, two NPN bipolar junction transistors, Q2 and Q1, and two impedances which act as loads, Z2 and Z1. When input, Vin, is high (VDD), the NMOS transistor, M1, turns on, causing Q1 to conduct, while M2 and Q2 are off, as depicted in Figure 2.2. As a result, a low (GND) voltage is translated to the output Vout. On the other hand, when the input is low, the M2 and Q2 turns on, while M1 and Q1 turns off, resulting to a high output level at the output, see Figure 2.3. In steady-state operation, Q1 and Q2 never turns on or off simultaneously, resulting to a lower power consumption. This also results to a push-pull bipolar output stage. Transistors M1 and M2, on the other hand, works as a phase-splitter, which results to a higher input impedance. 9 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 2.2. The equivalent circuit of Figure 2.1 with a high input signal. (Source: J. M Rabaey, Digital Integrated Circuits: A Design Prespective, New Jersey: Prentice-Hall, Inc., 1996.) Figure 2.3. The equivalent circuit of Figure 2.1 with a low input signal. (Source: J. M Rabaey, Digital Integrated Circuits: A Design Prespective, New Jersey: Prentice-Hall, Inc., 1996.) IMPEDANCES Z1 and Z2 The impedances Z2 and Z1 are used to bias the base-emitter junction of the bipolar transistor and to ensure that base charge is removed when the transistors turn off. Let us take an example when the input voltage makes a high-to-low transition. With this high-to-low transition, M1 turns off first. To turn off Q1, the base charge must be removed, which can be achieved by Z1. With this effect, transition time reduces. However, there exists a short time when both Q1 and Q2 are on, making a direct path from the supply (VDD) to the ground. This results to a current spike that is large and has a detrimental effect on both the noise and power consumption, which makes the turning off of the bipolar transistor fast as an importance. 10 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications BiCMOS TOPOLOGIES Figure 2.4. Alternative topologies for BiCMOS inverters. (Source: J. M Rabaey, Digital Integrated Circuits: A Design Prespective, New Jersey: Prentice-Hall, Inc., 1996.) For practical designs, the use of resistive elements, shown in Figures 2.1 to 2.3, are very disadvantageous due to their size. Slightly modified BiCMOS circuits are shown in Figure 2.4. In the first circuit (Figure 2.4a), the passive impedances, Z1 and Z2, are replaced with active impedances (NMOS transistors) that only turns on when needed. Unfortunately, a diode voltage drop is lost at the high and low ends of the output, which makes the circuit’s property a disadvantage. Figure 2.4b has the same property with Figure 2.4a. The only difference is its improved transient response. Figure 2.4c presents the resolution for the problems encountered in Figures 2.4a and 2.4b, which does not suffer from a reduced voltage swing. The resistor, R1, in combination with M2, provides a resistive path between VDD and Vout, and slowly pulls the output to VDD once Q2 is turned off. OTHER TOPOLOGIES Embabi, et. al., (Embabi, 1991), presented a brief paper on two BiCMOS buffer circuits that offer near rail-to-rail output voltage swing, which was a problem in the previous section. Hence, they also offer higher noise margins and operating speed, at the benefit of low powersupply voltages. The first and second implementations of their circuits are shown in Figure 2.5. Figure 2.5a consists of a multi-drain CMOS input stage. Transistors Pd and Nd act as discharging elements for Q1 and Q2, respectively, giving solution to the base-charge problem in the previous section. Transistors Q11 and Q22 act as input/output controlled switch. The complementary pair Q1 and Q2 act as the output driver. Figure 2.5b is an improved version of Figure 2.5a. 11 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 2.5. Schematic diagrams of the (a) first and (b) second implementations of complementary BiCMOS buffers. (Source: S. H. K. Embabi, et. al., “New full-voltage-swing BiCMOS buffers,”IEEE Journal of Solid-State Circuits, vol. 26, no. 2, Feb. 1991, pp. 150-153. ) 12 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications CHAPTER 3 ADVANTAGES AND DISADVANTAGES OF BiCMOS OVER CMOS The emergence of BiCMOS gates came from the hybridization of bipolar transistors and CMOS transistors, which have their own distinct advantages. As discussed in Chapter 1, the combination of a bipolar transistor’s high switching speed and high output drive capability and CMOS’ low-power and high-density characteristics made BiCMOS technology advantageous over CMOS technology. However, disadvantages still arise especially when it comes to lowering the supply voltage, and wafer fabrication complexity. In this chapter, the advantages and disadvantages of BiCMOS over CMOS technology are presented, showing significant factors into the variations on BiCMOS design which is discussed in Chapter 5. ADVANTAGES Low power consumption. The BiCMOS gates perform in the same manner as the CMOS inverter when it comes to power consumption, because both gates display almost no static power consumption. The dissipation is done by the discharging of the capacitors. When comparing BiCMOS and CMOS in driving small capacitive loads, their performance are comparable, however, making BiCMOS consume more power than CMOS. On the other hand, driving larger capacitive loads makes BiCMOS in the advantage of consuming less power than CMOS, because the construction of CMOS inverter chains are needed to drive large capacitance loads, which is not needed in BiCMOS. The advantage of BiCMOS over CMOS in power consumption was also verified by Chen and Kumar in (Chen, 1994), after designing a digital BiCMOS carry look-ahead adder. By implementing BiCMOS driver cells, they found out that BiCMOS can drive much larger capacitive loads as compared to static CMOS cells, thus having lower power consumption. High switching speed at large values of capacitive loads. The BiCMOS inverter exhibits a substantial speed advantage over CMOS inverters, especially when driving large capacitive loads. This is due to the bipolar transistor’s capability of effectively multiplying its current. The time delay of a BiCMOS inverter consists of two components: (1) the fixed components that is proportional to the lumped internal capacitance, Cint, composed of the MOS’s 13 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications diffusion capacitances, bipolar’s junction capacitances, and base-charge capacitances, and (2) the load capacitance, CL, in which, its effect is substantially reduced by the ( β F + 1) current multiplier introduced by the bipolar junction transistor. The expressions in (3.1) and (3.2) approximate the time delay from low-to-high, and high-to-low transitions, respectively. K 2CL βF +1 KC = K3Cint + 4 L βF +1 tdLH = K1Cint + (3.1) tdHL (3.2) However, for very low capacitive loads, the CMOS gate is faster than its BiCMOS counterpart due to small values of Cint. This makes BiCMOS ineffective when it comes to the implementation of internal gates for logic structures such as ALUs, where associated load capacitances are small. A plot of the propagation delay of BiCMOS and CMOS gates as a function of the load capacitance CL, is shown in Figure 3.1, with an accompanied simulation on Figure 3.2. Figure 3.1. Propagation delay of BiCMOS and CMOS gates as a function of CL. (Source: J. M Rabaey, Digital Integrated Circuits: A Design Prespective, New Jersey: Prentice-Hall, Inc., 1996.) Figure 3.2. Simulated propagation delays of CMOS and BiCMOS gates as a function of CL. (Source: J. M Rabaey, Digital Integrated Circuits: A Design Prespective, New Jersey: Prentice-Hall, Inc., 1996.) 14 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 3.3. Simulated propagation delays of CMOS and BiCMOS gates as a function of CL. (Source: S. K. Embabi, A. Bellaouar, M. I. Elmasry, and R. A. Hadaway, “New full-voltage-swing BiCMOS buffers,” IEEE Journal of Solid-State Circuits,” vol. 26, no. 2, Feb. 1991, pp. 150-153.) The high switching speed capability of the BiCMOS is also verified in Embabi’s paper (Embabi, 1991), in the development of a full-voltage-swing BiCMOS buffers. A comparison between CMOS and BiCMOS switching speed with load capacitance is shown in Figure 3.3. High resistance to process deviations and temperature changes. The resistance to process deviations and temperature changes of the BiCMOS is the reason behind the success of the development of a BiCMOS 1-Mbit DRAM by Watanabe, et. al., (Watanabe, 1989) and Kitsukawa, et. al., (Kitsukawa, 1987). They were able to derive a set of equations that determine the DRAM’s sensitivity to changes in temperature and process deviations for a 1.3 micron technology. 15 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications DISADVANTAGES The advantages of BiCMOS with CMOS has been presented in the previous section emphasizing on its low-power and high-speed capability, including its robustness with temperature and process deviations. However, BiCMOS has also some disadvantages when compared to CMOS which is presented in the next sections. Speed degradation in the low supply voltage region. One stringent problem introduced by Sakurai in (Sakurai, 1992) about BiCMOS circuit is its speed degradation in the low supply voltage region. Since the supply voltage for CMOS technology gradually decreased from 5V to less than 2V in the passed years, an optimization technique must be introduced. A measure on the measured delay with supply voltage is shown in Figure 3.4. Figure 3.4. Measured propagation delays of CMOS and BiCMOS gates as a function of VDD. (Source: T. Sakurai, “A review on low-voltage BiCMOS circuits and a BiCMOS vs. CMOS speed comparison,” Proceedings of the 35th Midwest Symposium on Circuits and Systems, vol. 1, Aug. 9-12, 1992, pp. 564-567.) BiCMOS having greater manufacturing complexity than CMOS. The addition of NPN and PNP transistors into the CMOS process exhibits greater amounts of manufacturing complexity. This is due to the technology’s viewpoint of having a better performance requirement, thus the implementation of bipolar transistors for high switching speed capabilities. Due to the greater complexity in developing BiCMOS circuits, strict care should be taken. Greater complexity also increases testing, verification, and database management. However, several approaches are being taken to resolve the speed degradation of a conventional BiCMOS circuit without the introduction of process complexity (Alvarez, 1991). 16 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications CHAPTER 4 THE BiCMOS PROCESS BiCMOS requires both bipolar junction and CMOS transistors, in which CMOS requires both nMOS and pMOS transistors. In the creation of CMOS, one complication is that an nchannel MOSFET requires a p-type background, while a p-channel MOSFET requires an n-type background. A CMOS process basically fabricates the circuit in bulk silicon. Another method which is much more superior to the use of bulk silicon is to use an insulating substrate. However, the latter method is costly than the previous one. In this chapter, CMOS process examples are described eventually bringing out different BiCMOS process examples. This section examines the different techniques in building CMOS and BiCMOS circuits. BULK CMOS The terms tubs and wells are common and required in building CMOS circuits, in which they have opposite polarities of the substrate to accommodate both n- and p-channel transistors. Figure 4.1. An n-well bulk CMOS process. (Source: J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992.) Figure 4.1 shows the cross-section of an n-well CMOS inverter. The CMOS inverter in the figure considers a p-type substrate. To be able to build a pMOS, a diffused n-well must be created onto the p-substrate. 17 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 4.2. A p-well bulk CMOS process. (Source: J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992.) Figure 4.2 shows the cross-section of a p-well CMOS inverter considering an n-type substrate. An nMOS is build by diffusing a p-well onto the n-substrate. Figure 4.3. A twin-tub bulk CMOS process. (Source: J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992.) Figure 4.3 shows the cross-section of a twin-tub bulk CMOS. This configuration provides distinct n-well and p-well regions in a lightly dopes epitaxial layer. This is a complicated approach, but provides self-isolation using reverse-biased pn junctions. It also helps solve latchup problems inherent in the circuit. BiCMOS PROCESS The cross-section of the BiCMOS inverter is shown in Figure 4.4. The figure shows a typical oxide-isolated chip with n- and p-channel MOSFETs and npn BJTs. Important aspects of a BiCMOS process include device characteristics, integration density, interconnect levels, and compatibility with existing CMOS designs. 18 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 4.4. The BiCMOS process. (Source: J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992.) 19 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications CHAPTER 5 BiCMOS VARIATIONS For several decades, scientists and engineers develop different forms and variations of BiCMOS circuits for specialized applications. In this chapter, these variations are described and applications of such variations are presented. ECL-BiCMOS The ECL-BiCMOS variation is described in the paper of Liu, et. al., (Liu, 1993). This technology offers not only high density CMOS capability, but also features high speed bipolar for ECL and mixed analog and/or digital applications. The paper also presents the development of a super self-aligned BiCMOS technology with a CMOS gate delay of 50 psec and a maximum frequency of 34 MHz. Figure 5.1 shows the bipolar ECL and CMOS gate delays of three BiCMOS generations. Figure 5.1. ECL bipolar and CMOS gate delays. (Source: T. M. Liu, T.-Y. Chiu, and R. G. Swartz, “High performance BiCMOS technology,” Proceedings of the IEEE 1993 Custom Integrated Circuits Conference, May 912, pp. 24.1.1-24.1.5.) TS-FS-BiCMOS The development of a Transiently-Saturated, Full-Swing BiCMOS was introduced by Hiraki et. al., in (Hiraki, 1992). The paper presents the advantage of this technology of having its delay weakly dependent of the output capacitance and is much more advantageous than CMOS and BiCMOS. 20 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications M-BiCMOS The M-BiCMOS variation is describe in Alavarez’s paper (Alvarez, 1991). It was emphasized that the real power of BiCMOS is in mixing and matching different design techniques effectively in one design. Thus, the Mixing and Matching of these designs, (i.e. CMOS, ECL, and BiCMOS circuits), makeup the M-BiCMOS variation. In his paper, a comparison of a CMOS, BiCMOS, and M-BiCMOS gate delay with supply voltage is presented as shown in Figure 5.2. Figure 5.2. CMOS, BiCMOS, and M-BiCMOS gate delay vs. suuply voltage. (Source: A. R. Alvarez, “BiCMOS – Has the promise been fulfilled?,” Technical Digest, International Electron Devices Meeting, Dec. 8-11, 1991, pp. 13.1.1-13.1.4.) B2M-BiCMOS A full-swing BiCMOS logic circuit called bipolar bootstrapped multi-emitter BiCMOS (B2M-BiCMOS) is introduced in Wu and Tseng’s paper, (Wu, 1996). The technology was tested in a multi-input NAND gates with a supply voltage of 2V and an output loading capacitance of 0.5pF. The results showed that the B2M-BiCMOS is much more feasible in many low-voltage BiCMOS applications. Several design techniques were used such as: (1) bipolar bootstrapping for fast full-swing operation, (2) introduction of multi-emitter logic in the pull-up section for complex logic circuits, and (3) a novel pull-down circuit also for complex logic circuits. A pulldown circuit that was used for a 5-input NAND gate is shown in Figure 5.3. For a 3-input NAND gate, the pull-up and pull-down sections are shown in Figure 5.4. 21 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 5.3. A pull-down circuit for a 5-input NAND B2M-BiCMOS gate. (Source: C.-Y. Wu and T.-K. Tseng, “Bipolar bootstrapped multi-emitter BiCMOS (B2M-BiCMOS) logic for low-voltage applications,” Proceedings of the Third IEEE International Conference on Electronics, Circuits, and Systems, Oct. 13-16, 1996, vol. 2, pp. 11741177.) Figure 5.3. A 3-input NAND B2M-BiCMOS gate. (Source: C.-Y. Wu and T.-K. Tseng, “Bipolar bootstrapped multiemitter BiCMOS (B2M-BiCMOS) logic for low-voltage applications,” Proceedings of the Third IEEE International Conference on Electronics, Circuits, and Systems, Oct. 13-16, 1996, vol. 2, pp. 1174-1177.) 22 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications CHAPTER 6 FEATURES OF ADVANCED BiCMOS TECHNOLOGIES BiCMOS technology has a lot of features and different approaches to BiCMOS technology are emerging with argues that there is not one BiCMOS process which can address all applications. Each application draws on different aspects of Bipolar/CMOS mixture to function effectively. The technological requirements of each will depend on the final application of the technology, which was described by Stogdale and Hunt in (Stogdale, 1992). 1. Good current drive capability: for application to bipolar buffered BiCMOS gates and output stages: a. Good current drive capability – low collector series resistance, buried layers. 2. Good performance in analog applications: a. High precision analog components, resistors, capacitors, etc. b. Well controlled device characteristics: Gain, Early voltage, Noise, etc. c. Tight control of parameters with temperature and operating current. d. Operating Voltage < 5V. e. High dynamic range. 3. High-speed performance: For applications in ECL logic the bipolar transistors are specifically optimized for lower power high speed performance, in particular: a. Very low gate delays and low power delay product. b. Minimized parasitic resistances and capacitances. c. Highly advanced processing techniques for minimization of feature sizes. d. Highly optimized emitter base structure with low transit time. 4. Good performance in power switching. Smart power applications etc,; a. Low series resistances; low sensitivity buried layers. b. High junction breakdown voltage characteristics. c. Good performance at high currents. 23 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications CHAPTER 7 APPLICATIONS OF BiCMOS There are endless applications for the BiCMOS technology, ranging from microprocessors and memories, to communications devices. This chapter presents some BiCMOS applications with its advantages over conventional CMOS counterparts. MEMORIES The group of Kitsukawa, (Kitsukawa, 1987), and Watanabe, (Watanabe, 1989), presented an experimental 1-Mbit BiCMOS DRAM, with its cross-section shown in Figure 7.1. Three developments were presented: (1) high soft error immunity, (2) high-speed circuit configuration of eight NMOS subarrays combined with BiCMOS peripherals and circuitry, and (3) lower power dissipation and peak current due to the development of BiCMOS voltage and current limiters. Figure 7.1. Cross-section of a 1-Mbit BiCMOS DRAM. (Source: G. Kitsukawa, et. al., “An experimental 1-Mbit BiCMOS DRAM,” IEEE Journal of Solid-State Circuits, vol. sc-22, no. 5, Oct. 1987, pp. 657-662.) In 2000, Nambu, et. al., developed a 550-ps access 900-MHz 1-Mbit BiCMOS SRAM employing the high-speed ECL technology, (Nambu, 2000). Three techniques were used to achieve an ultrahigh-speed SRAM which are: (1) the use of a BiCMOS word decoder/driver with an nMOS level-shift circuit, (2) a sense amplifier with a voltage-clamp circuit, and (3) a BiCMOS write circuit with a variable-impedance bitline load. With these techniques, delay times were reduce to as much as 54% and power dissipation to as much as 74% without sacrificing speed. A photomicrograph of the test chip is shown in Figure 7.2. 24 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 7.2. A photomicrograph of a BiCMOS SRAM. (Source: H. Nambu, et. al., “A 550-ps access 900-MHz 1-Mb ECL-CMOS SRAM,” IEEE Journal of Solid-State Circuits, vol. 35, no. 8, Aug. 2000, pp. 1159-1168.) ADDERS Chen and Kumar in (Chen, 1992), developed a BiCMOS carry look-ahead adder, which is believed to be a major component in an ALU. The paper presents a systematic method of implementing a BiCMOS adder design which is optimized with respect to area and time. With this method, it was shown that the BiCMOS adder achieved improvement by shortening the delay to as much as 80%. Figure 7.3 shows some BiCMOS black cells. Two papers by the group of Ueda, (Ueda, 1993) and (Ueda, 1996) present two 64-bit adders by using pass transistor BiCMOS circuits. The adder was fabricated using a 0.5 micron BiCMOS process with single polysilicon and double-metal interconnections. Experimental results show that the BiCMOS adder was 25% better than the conventional CMOS adder. The schematic diagram of the full-adder circuit is shown in Figure 7.3. MIXERS A high linear BiCMOS double balanced mixer for direct conversion applications is described in the paper of Belkhiri, et. al., in (Belkhiri, 2004). A comparison of his work with other recent mixers are shown in Figure 7.5. The double balanced mixer schematic diagram is shown in Figure 7.6. 25 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 7.3. Different BiCMOS black cells used in a 32-bit adder. (Source: C.-I. H. Chen and A. Kumar, “Area-time optimal digital BiCMOS carry look-ahead adder,” IEEE Asia-Pacific Conference on Circuits and Systems, Dec. 5-8, 1993, pp. 115-120.) Figure 7.4. A BiCMOS full-adder circuit. (Source: K. Ueda, H. Suzuki, K. Suda, Y. Tsujuhashi, and H. Shinohara, “A 64-bit adder by pass transistor BiCMOS circuit,” IEEE 1993 Custom Integrated Circuits Conference, pp. 12.2.112.2.4.) 26 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications Figure 7.5. A comparison of the BiCMOS mixer with other recent mixers. [3] Æ (Yamaji, 1998), [4] Æ (Ellinger, 2002), [7] Æ (Golgfarb, 2003), and [8] Æ (Sheng, 2003). (Source: C. Belkhiri, S. Toutain, and T. Razban, “A broadband highly linear BiCMOS mixer for direct conversion applications,” IEEE Microwave and Wireless Components Letters, vol. 14, no. 8, Aug. 2004, pp. 374-376.) Figure 7.6. A BiCMOS double balanced mixer schematic diagram. (Source: C. Belkhiri, S. Toutain, and T. Razban, “A broadband highly linear BiCMOS mixer for direct conversion applications,” IEEE Microwave and Wireless Components Letters, vol. 14, no. 8, Aug. 2004, pp. 374-376.) 27 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications ACKNOWLEDGEMENT REFERENCES [Alvarez, 1991] A. R. Alvarez, “BiCMOS – Has the promise been fulfilled?,” Technical Digest, International Electron Devices Meeting, Dec. 8-11, 1991, pp. 13.1.1-13.1.4. [Belkhiri, 2004] C. Belkhiri, S. Toutain, and T. Razban, “A broadband highly linear BiCMOS mixer for direct conversion applications,” IEEE Microwave and Wireless Component Letters, vol. 14, no. 8, Aug. 2004, pp. 374-376. [Chen, 1992] C.-I. H. Chen and A. Kumar, “Area-time optimal digital BiCMOS carry lookahead adder,” IEEE Asia-Pacific Conference on Circuits and Systems (APCCAS ’94), Dec. 58, 1994, pp. 115-120. [Ellinger, 2002] F. Ellinger, R. Vogt, and W. Bächtold, “Compact monolithic integrated resistive mixers with low distortion for HIPERLAN,” IEEE Transactions on Microwave Theory Technology, vol. 50, Jan. 2002, pp. 178-182. [Embabi, 1991] S. H. K. Embabi, A. Bellaouar, M. I. Elmasry, and R. A. Hadaway, “New fullvoltage-swing BiCMOS buffers,” IEEE Journal of Solid-State Circuits, vol. 26, no. 2, Feb. 1991, pp. 150-153. [Golgfarb, 2003] M. Golgfarb, E. Balboni, and J. Cavey, “Even harmonic double-balanced active mixer for use in direct conversion receivers,” IEEE Journal on Solid-State Circuits, vol. 38, Oct. 2003, pp. 1762-1766. [Hiraki, 1992] M. Hiraki, et. al., “A 1.5V full-swing BiCMOS logic circuit,” ISSC’92 Digest of Technical Papers, Feb. 1992, pp. 48-49. [Kitsukawa, 1987] G. Kitsukawa, R. Hori, Y. Kawajiri, T. Watanabe, T. Kawahara, K. Itoh, Y. Kobayashi, M. Oohayashi, K. Asayama, T. Ikeda, and H. Kawamoto, “An experimental 1Mbit BiCMOS DRAM,” IEEE Journal of Solid-State Circuits, vol. sc-22, no. 5, Oct. 1987, pp. 657-662 [Liu, 1993] T. M. Liu, T.-Y. Chiu, and R. G. Swartz, “High performance BiCMOS technology,” Proceedings of the IEEE 1993 Custom Integrated Circuits Conference, May 9-12, pp. 24.1.124.1.5. [Nambu, 2000] H. Nambu, K. Kanetani, K. Yamasaki, K. Higeta, M. Usami, M. Nishiyama, K. Ohhata, F. Arakawa, T. Kusunoki, K. Yamaguchi, A. Hotta, and N. Homma, “A 550-ps 28 E. A. Gonzalez, BiCMOS Technology: Processes, Trends, and Applications access 900-MHz 1-Mb ECL-CMOS SRAM,” IEEE Journal of Solid-State Circuits, vol. 35, no. 8, Aug. 2000. [Rabaey, 1996] J. M Rabaey, Digital Integrated Circuits: A Design Prespective, New Jersey: Prentice-Hall, Inc., 1996 [Sakurai, 1992] T. Sakurai, “A review on low-voltage BiCMOS circuits and a BiCMOS vs. CMOS speed comparison,” Proceedings of the 35th Midwest Symposium on Circuits and Systems, vol. 1, Aug. 9-12, 1992, pp. 564-567. [Sheng, 2003] L. Sheng and L. E. Larson, “An Si-SiGe BiCMOS direct-conversion mixer with second-order and third-order nonlinearity cancellation for WCDMA applications,” IEEE Transactions on Microwave Theory Technology, vol. 51, Nov. 2003, pp. 2211-2220. [Stogdale, 1992] N. Stogdale and P. Hunt, “BiCMOS – A technology for all seasons?,” IEEE Colloquium on Technology and Application of Combined Bi-Polar and CMOS Semiconductor Processes, Feb. 17, 1992, pp 1/1 – 1/5. [Ueda, 1993] K. Ueda, H. Suzuki, K. Suda, Y. Tsujihashi, and H. Shinohara, “A 64-bit adder by pass transistor BiCMOS circuit,” IEEE 1993 Custom Integrated Circuits Conference, pp. 12.2.1-12.2.4. [Ueda, 1996] K. Ueda, H. Suzuki, K. Suda, H. Shinohara, and K. Mashiko, “A 64-bit carry look ahead adder using pass transistor BiCMOS gates,” IEEE Journal of Solid-State Circuits, vol. 31, no. 6, Jun. 1996, pp. 810-818. [Uyemura, 1992] J. P. Uremuya, Circuit Design for CMOS VLSI, Massachusetts: Kluwer Academic Publishers, 1992. [Watanabe, 1989] T. Watanabe, G. Kitsukawa, Y. Kawajiri, K. Itoh, R. Hori, Y. Ouchi, T. Kawahara, and T. Matsumoto, “Comparison of CMOS and BiCMOS 1-Mbit DRAM performance,” IEEE Journal of Solid-State Circuits, vol. 24, no. 3, Jun. 1989, pp. 771-778. [Wu, 1996] C.-Y. Wu and Y.-K. Tseng, “Bipolar bootstrapped multi-emitter BiCMOS (B2MBiCMOS) logic for low-voltage applications,” Proceedings of the Third IEEE International Conference on Electronics, Circuits, and Systems, Oct. 13-16, 1996, vol. 2, pp. 1174-1177. [Yamaji, 1998] T. Yamaji, H. Tanimoto, and H. Kokatsu, “An I/Q active balanced harmonic mixer with LM2 cancelers and a 45˚ phase splitter,” IEEE Journal on Solid-State Circuits, vol. 33, Dec. 1998, pp. 2240-2246. 29