Code Generation Infrastructure for a Multi

advertisement

Code Generation Infrastructure for a MultiModal Synchronous MoC

Alessandro Pinto

United Technologies Research Center, Berkeley, CA

pintoa@utrc.utc.com

Acknowledgment: Nikola Trcka, Andrzej Banaszuk,

UTRC, East Hartford, CT

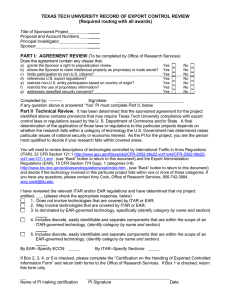

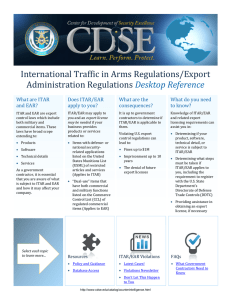

This document contains no data subject to the EAR or the ITAR

OBJECTIVES

Summary

Library of

components (multiple

abstraction levels)

Model editor

Code generators

Language definition

(syntax/semantics)

Code

Inputs to formal verification

Run time environment

Formal verification engines

Hardware/Network

2

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

OBJECTIVES

Summary

Library of

components (multiple

abstraction levels)

Model editor

• Application domain Language

• Flexibility/Usability Concrete

Codesyntax

generators

• Hardware/Efficiency Low level code/ Language

Language definition

• Properties Verification

(syntax/semantics)

• All of above Code generators

Code

Inputs to formal verification

Run time environment

Formal verification engines

Hardware/Network

3

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

OUTLINE

Application domain

Synthesis / Scope

Language selection

Run time environment / Code generation

Verification

Conclusions / Future work

4

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

APPLICATION DOMAIN

Autonomous systems

(Source: CMU)

(Source: MIT)

Knowledge

Planning

Execution

(Source: VT)

5

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

SPECIFICATION LANGUAGE

A Multi-Modal, Multi-Rate Synchronous Language

S

P

I

Cmd

onCmd

S (1)

P (1)

I (2)

onRpt

Rpt

EP

S (1)

P (1)

I (2)

EP (2)

PL

EX

AM

AM (1)

EX (2)

PL (4)

A. Ghosal, T.A. Henzinger, C. M. Kirsch, D. Iercan, and A. Sangiovanni-Vincentelli.

A Hierarchical Coordination Language for Interacting Real-Time Tasks. EMSOFT, 2006

6

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

SPECIFICATION LANGUAGE

Concrete syntax: SysML

7

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

TOOL CHAIN

Multi-rate

profile

C++ Code gen.

C++ runtime

SysML

editor

Library

Ver. Code gen.

C++ Code

Java Sys

G++

𝜇Calculus MC

exe

Result

SMT code gen.

Interface

verification

formula

Property

CVC4

Result

8

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

MULTI-MODAL MULTI-RATE SYNCHRONOUS MOC

Syntax

𝑏 ∈ 𝐵𝑢𝑓𝑓

𝑝1 ∈ 𝑃𝐼

𝐵1

𝐵2

𝐵3

𝐵2

𝑝3 ∈ 𝑃𝐼

𝑚𝑜 ∈ 𝑀

𝐵1 ∈ 𝐵

𝐵3

(𝑚0 , 𝑚1 )

𝑝2 ∈ 𝑃𝑂

𝑐𝑜𝑛𝑛 𝑝1 = 𝑝3

𝑏𝑙𝑜𝑐𝑘 𝑝3 = 𝐵2

Tree of Blocks 𝐵

Ports 𝑃 = 𝑃𝐼 ⊎ 𝑃𝑂 taking values from 𝑉 ∪⊥

Buffers 𝐵𝑢𝑓𝑓

Modes 𝑀

Connection function conn ∶ 𝑃 ∪ 𝐵𝑢𝑓𝑓 → 𝐵𝑢𝑓𝑓 ∪ 𝑃 (with some restrictions)

A frequency function 𝑓𝑟𝑒𝑞 ∶ 𝐵 × 𝑀 → ℕ0

Mode transition 𝑇𝑀 ⊆ 𝑀2 , 𝑔𝑟𝑑𝑀 ∶ 𝑇𝑀 → 𝑃 → 𝑉 → {𝑇, 𝐹, 𝑋 )

System states 𝑆

Execution transitions TS ⊆ 𝑆 2 , 𝑒𝑥𝑒𝑐: 𝑇𝑆 → ( 𝑃𝐼 → 𝑉 → [𝑃𝑂 → 𝑉])

Function block association function block: 𝑃 ∪ 𝑇𝑀 ∪ 𝑇𝑆 → 𝐵

9

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

MULTI-MODAL, MULTI-RATE SYNCHRONOUS MOC

Semantics (sketch)

Configuration 𝛼, 𝑣𝑎𝑙

Where 𝛼: 𝐵 → 𝑀 × 𝑎𝑐𝑡, 𝑛𝑎𝑐𝑡 × 𝑆 × ℕ0

And 𝑣𝑎𝑙: 𝑃 ∪ 𝐵𝑢𝑓𝑓 → 𝑉 ∪⊥

5 micro-steps: write, chmod, read, exec, tick

Let 𝐵′ ⊆ 𝐵, a step is defined as follows:

𝐵′

𝛼, 𝑣𝑎𝑙 →

𝛼, 𝑣𝑎𝑙

𝑤𝑟𝑖𝑡𝑒 𝐶

𝛼1 , 𝑣𝑎𝑙1

𝛼3

𝑐ℎ𝑚𝑜𝑑 𝐵 ′

, 𝑣𝑎𝑙 ′

𝛼 ′ , 𝑣𝑎𝑙 ′

𝛼2 , 𝑣𝑎𝑙1

𝑡𝑖𝑐𝑘 𝐵 ′

Executes step of all

children

≡

𝑟𝑒𝑎𝑑 𝐶

𝛼2 , 𝑣𝑎𝑙2

𝑒𝑥𝑒𝑐 𝐶

𝛼′, 𝑣𝑎𝑙 ′

Where 𝐶 is the union of all children of 𝐵′

10

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

VERIFICATION

Some properties of interest

Generating the verification code is a synthesis problem in

itself…

If 𝑐𝑜𝑛𝑛 𝑝1 = 𝑝2 ∈ 𝑃, then 𝑏𝑙𝑜𝑐𝑘(𝑝1 ) and 𝑏𝑙𝑜𝑐𝑘 𝑝2

cannot be active at the same time

Mode switches only occur at the end of mode hyperperiod

More can be done but it requires abstracting from data

11

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013

INTERFACE COMPATIBILITY PROBLEM

Pick up command

World Model

“Move to” command

Path Manager

Vehicle motion commands

Mission Manager

Load command

Load Manager

Arm motion commands

12

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

INTERFACE SPECIFICATION

Variable x, type ¿x

Vector of variables X=(x1,…,xn), type ¿X = (¿x1,…,¿xn)

A command a has:

parameters X(a)

precondition pre(a)

effect eff(a)

A set of action A={a1,…,am} has

parameters X(A) = (X(a1),…,X(am))

13

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

INTERFACE SPECIFICATION

commander ports

Intelligent module I

Interface

Ports

subordinate ports

For a port p, A(p) is the set of

command associated with that port

Alfaro, L. d. and Henzinger, T. A., “Interface Theories for Component-Based Design," Proceedings of the First International Workshop on Embedded Software, EMSOFT '01, Springer-Verlag, London, UK, UK, 2001, pp. 148-165.

14

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

COMPOSITION

Two modules are composable if

Composition operator:

15

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

INTERCONNECTION

An interconnect is a directed graph G(V,E):

V is a set of ports, E is a set of channels

I is connectable by G if:

Connection operator

Smallest transitive relation

16

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

WELL FORMED SYSTEMS

17

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

WELL FORMED SYSTEMS

18

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

CONCLUSIONS AND FUTURE WORK

Analysis of the application domain

Language selection (syntax, semantics, concrete syntax)

Code generation (execution, verification)

Tight integration with other tools and semantic domains

Behavioral verification

Program synthesis

19

A. Pinto, UTRC, WSS, ESWEEK 2013 – This page contains no data subject to the EAR or ITAR

10/28/2013