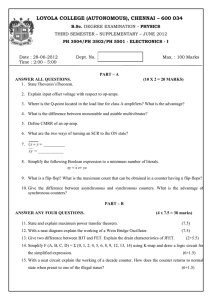

Calicut University Question Papers

G overnment

E ngineering

C ollege

K

ozhikode-5

Calicut University Previous Year

B.Tech Question Papers

AI 09 Syllabus: S

3

(Version 1.00 - 2015-07-08)

Prepared by :Mohammed Sadik (2010 AEI batch) < sadiqpkp(at)gmail(dot)com >

Nikhil Narayan (2010 AEI batch) < nikhil.sopanam(at)gmail(dot)com >

Copyright c 2013, 2014, 2015 Mohammed Sadik P. K.

Some Rights Reserved.

Note: The questions included in this file are in public domain (as far as I know). But this implementation, the L A TEX source and the corresponding compiled document is copyright under the terms and conditions of GNU GPL V3 or later . You may copy, modify, or redistribute the source file under

GNU GPL license conditions.

You can see that I have not included any harassing headers or footers in any page. You may print this and use as you wish. If you feel this work helpful please be helpful to your neighbour.

Check http://www.sadiqpk.org

or mail me to get the latest version and source. Please report me your suggestions and mistakes found.

This document has been completely developed using free software .

Operating systems : Debian GNU/Linux, Fedora GNU/Linux

Typeset Engine

Editor

Circuit Design

: L TEX 2 ε

: GNU Emacs

: X circuit, GNU Dia

Spell check

Other softwares :

: GNU Ispell with GNU Emacs

GNU bash, epspdf, evince etc.

D 30912

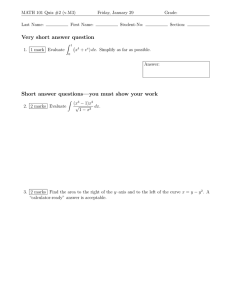

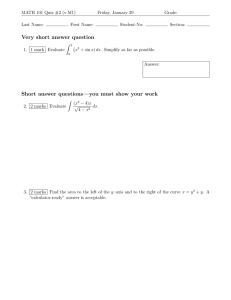

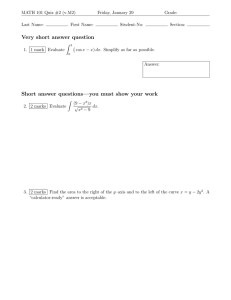

(Pages : 2) Name: ...............................

Reg. No: ...........................

THIRD SEMESTER B.TECH. (ENGINEERING) DEGREE EXAMINATION

OCTOBER 2012

AI09 303—ELECTRONIC CIRCUITS—1

(2009 Admissions)

Time: Three Hours Maximum: 70 Marks

Note: The same Question paper was printed for December 2010 Examination (Code: 10051)

Part A

Answer all questions

1. Explain the effect of temperature on the volt-ampere characteristic of a diode.

2. Why do we need filters in a power supply? Under what condition we shall prefer a capacitor filter?

3. Draw the circuit diagram of a common emitter amplifies with emitter and voltage divider biasing circuit. Why normally an emitter bypass capacitor is used?

4. Draw the circuit diagram of an RC coupled amplifier using PNP transistor.

5.

(a) How does the drain current vary with gate voltage in the saturation region.

(b) How does the trans conductance vary with drain current?

(5 × 2 = 10 marks)

Part B

Answer any four questions .

6. Draw two biasing circuits for a JFET or a depletion type MOSFET.

7. What are the important applications of a diode?

8. A full wave rectifier with a center tapped transformer (10–0–10V) supplies a load current of 100 mA. Neglecting the diode forward resistance and secondary winding resistance, find (a) the dc output voltage (b) PIV of each diode and (c) ripple frequency.

9. Explain the V–I characteristics of UJT. Why it is called a current controlled negative resistance device?

10. Explain how will you determine h -parameters of a transistor experimentally.

11. Give a circuit diagram of a two-stage transistorized RC coupled amplifier. Also draw the frequency response of the amplifier.

(4 × 5 = 20 marks)

Turn over

2 D 30912

Part C

Answer all questions .

12.

(a) i. What are the different types of inductors? Explain them with their constructional features. Give some important applications of inductors.

(5 marks) ii. Explain briefly about the basic construction of an electrolytic capacitor.

(5 marks)

Or

(b) i. Explain with suitable diagram how a diode can be used as a peak clipper and a base clipper as series element and shunt element. Draw a circuit for a slices.

(5 marks) ii. What is the purpose of a clamping circuit? Explain the working of a diode clamper.

How clamping to a dc level is achieved?

(5 marks)

13.

(a) i. Explain the operation of short circuit protection against overload with neat circuit diagram.

(5 marks) ii. A 10 V zener diode is used to regulate the voltage across a variable load resistor. The input voltage varies between 13 and 16 V. The load current (I

L

) varies between 10 and

85 mA. The minimum zener current is 15 mA. Find (i) the maximum value of R s the maximum power dissipated by the zener diode, using the value of R s

.

and

(5 marks)

Or

(b) i. Draw the circuit diagram of half wave rectifier. Explain its working. What is the frequency of ripple in its output?

(6 marks) ii. A full-wave rectifier supplies 0.2 A current at 30 V dc. Find the ripple factor to be expected when two 100 mF capacitors and a 5 H inductor are used in Pi-filter with a

50 Hz supply.

(4 marks)

14.

(a) Develop a low frequency equivalent circuit for a basic common collector amplifier and derive the relations for the current gain, voltage gain and input resistance in terms of h -parameters.

Make suitable assumptions and simplify the final results. Also justify the name ‘emitter follower’ for this type of amplifier.

Or

(b) i. With the help of a suitable circuit diagram, explain the working of a RC coupled amplifier. Derive the expression for voltage gain of the amplifier.

(6 marks) ii. Explain with suitable circuit diagram, the operation of transformer coupled transistorized amplifier.

(4 marks)

15.

(a) How a small signal high frequency model is different from a low frequency model? Explain it briefly.

Or

(b) Draw neatly the circuit diagram of a common source JFET amplifier and explain its working.

D 20629

(Pages : 3) Name: ...............................

Reg. No: ...........................

THIRD SEMESTER B.TECH. (ENGINEERING) DEGREE EXAMINATION

OCTOBER 2011

AI09 303—ELECTRONIC CIRCUITS—1

(2009 Admissions)

Time: Three Hours Maximum: 70 Marks

Part A

Answer all questions

1. What is a PN Junction diode? How its terminals are identified?

2. The Q-factor of a 100 mH inductor is 80. When operated in 400 kHz range. What is the dc resistance (R

0

) of the inductor?

3. What is the function of a bleeder resistor?

4. Name different types of biasing circuits and give three circuit configurations.

5. How do you set a Q-point in a self-biased JFET?

(5 × 2 = 10 marks)

Part B

Answer any four questions .

6. How does the dynamic resistance ‘r’ of a diode vary with (a) Current and (b) Temperature

(c) What is the order of magnitude of ‘r’ for silicon at room temperature and for a dc current of

1mA?

7. A zener diode voltage regulating circuit is shown in Fig. 1. The zener diode used has zener

Voltage (V z

) of 15V and minimum current I z

(min) of 2 µ A, a power dissipation of 120 mW and a zener resistance of 40Ω. If the resistance is 5KΩ and the input voltage varies from 18 to 24V, find the value of R s

.

I

L

= 0.1A

R

β =100

I

B

V s

15 - 18V

I

12 V

I z

Fig. 1.

V z

8. What are the advantages of a bridge rectifier as compared to a full wave center-tapped rectifier?

Turn over

2 D 20629

9. Compare the relative stability of (a) emitter bias and fixed bias circuit, (b) emitter bias and voltage divide bias circuits.

10. Explain the essential difference between the RC coupled and direct coupled amplifier.

11. A certain JFET amplifier has g m of 4ms, r

Assume the source resistance to be zero.

d

= 10KΩ and R

D

= 5KΩ. What is the voltage gain?

(4 × 5 = 20 marks)

Part C

Answer all questions .

12.

(a) i. A. Draw the piecewise linear voltampere characteristic of a p-n diode.

B. What is the circuit model for the ON state?

C. The OFF state.

B. For I

B

= 0, What is I

C

?

(6 marks) ii. A. Derive the expression for I

C region.

versus I

B for a CE transistor configuration in the active

(4 marks)

Or

(b) i. A. Sketch the circuit of a CS amplifier.

B. Derive the expression for the voltage gain at low frequencies.

C. What is the maximum value of A

V

?

ii. A. Sketch the cross section of a p-channel enhancement MOSFET.

B. Show two circuit symbols for this MOSFET.

13.

(a) Draw the circuit diagram of full wave rectifiers: i. With center-tap connection and ii. Bridge connection. Explain their working.

What is the peak inverse voltage of a diode in each case?

(6 marks)

(4 marks)

Or

(b) i. Draw circuit diagram of transistor shunt regulator. Explain it briefly.

(5 marks) ii. A 36V dc voltage is applied through a series resister of 600Ω to a load 300Ω shunted by a zener diode as shown in Fig. 2. if V z

= 8V and γ z

= 10Ω.

Find (a) dc Load voltage; (b) Power dissipated in the zener and (c) maximum current, that a regulator can deliver and still regulate.

V s

=36V

3

R s

=600 Ω

D 20629

R

L

=300 Ω

Fig. 2.

14.

(a) i. Derive an expression for the stability factor of a fixed bias current.

(4 marks) ii. Draw a voltage divider bias circuit and derive an expression for its stability factor.

(6 marks)

Or

(b) Derive the expressions for input resistance, output resistance, current gain and voltage gain of a common emitter amplifier.

15.

(a) i. What are the biasing schemes available to achieve to achieve the required bias in a

JFET? Explain any one of the biasing schemes.

(6 marks) ii. A certain JFET has a transconductance (g m

) of 2500 µ S. With an external drain resistance of 2kΩ. Find the value of ideal voltage gain.

(4 marks)

Or

(b) i. Sketch the small signal high frequency circuit of a CS amplifier.

ii. Derive the expression for the voltage gain.

(4 × 10 = 40 marks)

D 51037

(Pages : 2) Name: ...............................

Reg. No: ...........................

THIRD SEMESTER B.TECH. (ENGINEERING) DEGREE EXAMINATION

NOVEMBER 2013

AI09 304—ELECTRICAL ENGINEERING

(2009 Admissions)

Time: Three Hours Maximum: 70 Marks

Part A

Answer all questions

1. What are the desirable conditions for DC generators to be connected in parallel?

2. Why is the HV side of a single-phase transformer left open and the open circuit test is performed by energising the LV side?

3. Why is a single-phase transformer rated in kVA?

4. Give the relationship between the gross mechanical power output and the air gap power in a three-phase Induction motor.

5. What is meant by creep in an Induction type energy meter?

(5 × 2 = 10 marks)

Part B

Answer any four questions .

6. Classify the DC generators and draw the external characteristics of each type of DC generator.

7. Explain the principle of operation of a single-phase transformer and hence derive and expression for induced emf from its first principles.

8. Discuss the phenomenon of armature reaction in a three-phase alternator for pure inductive load at the armature terminals.

9. Derive the condition for maximum torque at running condition for a three-phase induction motor.

10. Explain the possible errors that can occur in a moving iron instrument when both AC and DC quantities are measured.

11. Demonstrate how power can be measured in a three-phase circuit by using two wattmeters.

(4 × 5 = 20 marks)

Turn over

2 D 51037

Part C

Answer section ( a ) or section ( b ) of each question .

12.

(a) i. Differentiate Lap and wave windings in a DC machine.

(2 marks) ii. Two DC shunt generators are rated 230 kW and 150 kW, 400 V. Their full load voltage drops are 3% and 6% respectively. They are excited to no-load voltages of 410 V and

420 V respectively. How will they share a load of 1000 Amps and the corresponding bus voltage?

(8 marks)

Or

(b) i. Compare the advantages of four point starter over three-point starter.

(2 marks) ii. A 10 kW, 250 V shunt motor has an armature resistance of 0.5Ω and a field resistance of

200 W. AT no-load and rated voltage, the speed is 1200 rpm , and the armature current is 3 Amps. At full load 8 rated voltage, the line current is 47 Amps and because of armature reaction, the flux is 4% less than its no-load value. What is the full-load speed? What is the developed torque at full load?

(8 marks)

13.

(a) Explain the different methods of cooling adopted in a single-phase transformer. (10 marks)

Or

(b) i. What is all day efficiency?

(2 marks) ii. Draw and explain the phasor diagram respecting the relationship between different voltages and current of a single-phase transformer if the secondary is loaded with pure resistive and pure capacitive load.

(8 marks)

14.

(a) Explain in detail the construction of a three-phase Induction motor. Also explain the different types of rotor construction.

(10 marks)

Or

(b) Explain how does a synchronous motor perform when the excitation current is increased from zero to rated value with the help of phasor diagram relating the induced voltage and the field currents.

(10 marks)

15.

(a) Explain the kelvins double bridge method of measurement of Low resistance.

(10 marks)

Or

(b) Explain how dissipation factor can be determined accurately with the help of schering

Bridge.

(10 marks)

(4 × 10 = 40 marks)

D 20630

(Pages : 3) Name: ...............................

Reg. No: ...........................

THIRD SEMESTER B.TECH. (ENGINEERING) DEGREE EXAMINATION

OCTOBER 2011

AI09 304—ELECTRICAL ENGINEERING

(2009 Admissions)

Time: Three Hours Maximum: 70 Marks

Part A

Answer all questions

1. What is the need for starters for starters used in D.C. motors? Justify your answer.

2. What is the significance of ‘Back emf’ in a shunt motor?

3. Mention the losses that occur in a single phase transformer.

4. Comment on the starting torque of a wound rotor induction motor.

5. Which bridge is suitable for measuring small capacitance? Mention any two special features of it.

(5 × 2 = 10 marks)

Part B

Answer any four questions .

6. A 75kW, 250 V compound dc generator has the following data:

R a

R sh

= 0 .

04Ω R se

= 0 .

004Ω

= 100Ω Brush contact deep = 1V per brush.

Determine and compare the induced emf in the generator when it is

(a) Long shunt compound and

(b) Short shunt compound.

7. Draw the phasor diagram representing the various currents and voltage in a single-phase transformer when loaded with inductive and capacitive loads.

8. Discuss how constant flux is maintained in a single-phase transformer when the secondary winding is loaded.

9. Explain how the rotor rotates in a three-phase induction motor when a 3φ supply is given to the stator terminals.

10. Explain any one starting method for a three-phase synchronous motor.

Turn over

2 D 20630

11. Explain the constructional details of a permanent magnet moving coil type ammeter.

(4 × 5 = 20 marks)

Part C

Answer section ( a ) or section ( b ) of each question .

12.

(a) Explain with appropriate graphs the magnetisation and load characteristics of a dc shunt generator (self excited) type.

Or

(b) A dc shunt motor rated 10kW connected to 250 V supply is loaded to draw 35 A armature current running at 1250 rpm. Given R a

= 0 .

5Ω. Determine the following: i. Load torque if rotational loss is 500Ω.

ii. Motor efficiency if R sh

= 250Ω.

iii. Armature current for maximum motor efficiency and the maximum efficiency.

What is the corresponding load torque speed?

(10 marks)

13.

(a) Explain constructional details of shell and core type transformers.

(b)

Or i. Derive the emf equation of a single-phase transformer.

ii. Draw the equivalent circuit of a single-phase transformer and explain.

(5 marks)

(5 marks)

14.

(a) Explain with neat diagram the construction and principle of working of a three synchronous motor.

Or

(b) i. Draw the equivalent circuit of a three-phase induction motor and explain the circuit parameters.

ii. A 6 pole 50 Hz 3-phase induction motor running on a full load develops a useful torque of 160 Nm when the rotor emf makes 120 complete cycles per minute. Calculate the shaft power output. If the mechanical torque lost in friction and that for core-loss is

10 Nm, calculate the

A. Copper loss in the rotor windings.

B. The input to the motor and

C. Efficiency.

The total stator loss is given to be 800 W.

15.

(a) Justify that two wattmeters are required to measure three-phase power, with appropriate equations.

3 D 20630

(b) Explain with suitable diagrams how inductance can be measured in a Maxwell’s bridge in comparison with a standard variable capacitance. Also discuss the advantage and disadvantages of the Maxwell’s bridge.

(4 × 10 = 40 marks)

D 51038

(Pages : 2) Name: ...............................

Reg. No: ...........................

THIRD SEMESTER B.TECH. (ENGINEERING) DEGREE EXAMINATION

NOVEMBER 2013

AI 09 305—DIGITAL SYSTEMS

(2009 Admissions)

Time: Three Hours

Part A

Answer all questions

1. What is a parity bit? List its types.

2. Distinguish between PLAs and PALs.

3. State any two advantages of CMOS Logic over other families.

4. State the difference between Mealy and Moore Machine.

5. What are the two types of Asynchronous sequential circuits?

Maximum: 70 Marks

(5 × 2 = 10 marks)

Part C

Answer all questions .

6. State and prove De Morgan’s theorem.

7. Find the Canonical form of f (A, B, C, D) = ABC

0

+ AB

0

D + C

0

D + CD

0

.

8. Write a brief note on ROM.

9. Explain the operation of a JK flip-flop.

10. Explain the characteristics of ECL Logic.

11. What are cycles and races? How are they avoided?

(4 × 5 = 20 marks)

Part C

Answer all questions .

12.

(a) Reduce the following expression using K-Map: f (A, B, C, D, E) = P m (0 , 2 , 4 , 15 , 21 , 27 , 29) + P d (3 , 5 , 26).

Or

Turn over

2 D 51038

(b) Minimize:

F(A, B, C, D) = P m (0 , 1 , 5 , 7 , 8 , 9 , 10 , 11 , 14 , 15) using Quine McCluskey method.

13.

(a) Implement the following function using suitable multiplexers:

F(A, B, C, D) = P m (0 , 2 , 4 , 6 , 8 , 10 , 12 , 14).

Or

(b) Implement a full adder using suitable decoder and additional logic gates.

14.

(a) Design a MOD-5 counter and explain its operation.

Or

(b) Explain the operation of a Monostable Multivibrator and astable Multivibrator.

15.

(a) Design a serial adder using Mealy state machine and explain its operation.

Or

(b) Minimize the state table give below:

Present Next state, Z (Output)

State

A

B

C

D

E

0

B, 0

B, 0

B, 0

E, 1

B, 0

X input

1

C, 0

D, 0

C, 0

C, 0

D, 0

(4 × 10 = 40 marks)

D 30914

(Pages : 2) Name: ...............................

Reg. No: ...........................

THIRD SEMESTER B.TECH. (ENGINEERING) DEGREE EXAMINATION

OCTOBER 2012

AI 09 305—DIGITAL SYSTEMS

(2009 Admissions)

Time: Three Hours Maximum: 70 Marks

Part A

Answer all questions

1. Convert 22.20

10 to its binary equivalent.

2. Compare 1’s complement and 2’s complement form.

3. Design a Half Adder.

4. Convert JK flip flop into a D flip flop.

5. What is a totem pole output?

(5 × 2 = 10 marks)

Part B

Answer any four questions .

6. Write a note on Error detecting Codes.

7. State and prove De Morgan’s theorem.

9. Design a Binary-Gray decoder.

10. How frequency division is achieved using flip flops? Give the general expression for it.

11. State the condition for state equivalence Give an example.

(4 × 5 = 20 marks)

Part C

Answer all questions .

12.

(a) Explain any one Error detecting and Correcting code.

Or

(b) Determine the prime implicants of the function.

F(A, B, C, D) = P (0 , 1 , 2 , 3 , 5 , 6 , 7 , 8 , 11 , 13).

Turn over

2 D 30914

13.

(a) Design an octal to binary encoder.

(b) Discuss in detail about: i. Static RAM.

ii. Dynamic RAM.

14.

(a) Design a 3-bit bidirectional shift register.

Or

Or

(b) Explain the features of: i. TTL ii. ECL iii. CMOS logics.

15.

(a) Obtain the transition table and flow table for the given asynchronous sequential circuit.

Or

(b) Design a serial parity generator using the asynchronous FSM technique.

(4 × 10 = 40 marks)

D 20631

(Pages : 2) Name: ...............................

Reg. No: ...........................

FOURTH SEMESTER B.TECH. (ENGINEERING) DEGREE EXAMINATION

OCTOBER 2011

AI 09 305—DIGITAL SYSTEMS

(2009 Admissions)

Time: Three Hours Maximum: 70 Marks

Part A

Answer all questions

1. State consensus theorem.

2. Simplify f = AB + BC + B

0

C

0

.

3. State the advantage of carry look-ahead adders.

4. Implement the following function using AND-OR realization: f = ABC + A

0

BC

0

D.

5. Define fan-in and fan-out.

(5 × 2 = 10 marks)

Part B

Answer any four questions .

6. Implement the following function using SOP and POS forms f (A, B, C) = AB + AC + A

0

C

0

+A

0

B

0

+ A

0

B + AC

0

7. Simplify the following function f (A, B, C, D) = P m (0 , 1 , 2 , 3 , 5 , 7 , 8 , 9 , 11 , 12)

8. Design a full Adder.

9. Design a 2-bit magnitude comparator.

10. Design a 2-bit Asynchronous counter using JK flip flops.

11. Explain the basic principle of partitioning procedure.

(4 × 5 = 20 marks)

Part C

Answer section ( a ) or section ( b ) of each question .

12.

(a) The Hamming Code 101101101 is received. Correct it if any errors. There are four parity bits and odd parity is used.

Turn over

2 D 20631

Or

(b) Simplify the following function using Quine Mc Cluskey method f (A, B, C, D, E) = P m (0 , 1 , 2 , 3 , 5 , 7 , 9 , 12 , 15 , 17 , 21 , 25 , 27 , 29 , 30 , 31)

13.

(a) Design a BCD adder.

Or

(b) What is a race around condition? How it is avoided in Master Slave JK flip flop? Explain.

14.

(a) Design a 4-bit universal shifter and explain its operation.

Or

(b) Draw the circuit schematic of a 2-input TTL NAND gate and explain its operation.

15.

(a) Draw a sequential circuit for the state diagram shown in figure. Use state assignment rules for assigning states.

(b) Design a sequence recogniser to detect the sequence 1011.

10053

(Pages : 2) Name: ...............................

Reg. No: ...........................

THIRD SEMESTER B.TECH. (ENGINEERING) DEGREE EXAMINATION

DECEMBER 2010

AI 09 305—DIGITAL SYSTEMS

(2009 Admissions)

Time: Three Hours Maximum: 70 Marks

Part A

Answer all questions

1. Convert binary number 11011.1101 to its decimal equivalent.

2. Express -54 in 2’s complement form.

3. Determine the minimum number of gates required to implement the boolean function (AB + C) using only 2-input NOR gates.

4. What do you mean by propagation delay?

5. Draw te circuit diagram of a CMOS NAND gate.

(5 × 2 = 10 marks)

Part B

Answer any four questions .

8. Convert SR flipflop to JK flipflop.

9. Design a combinational logic circuit which will compare two 4 bit numbers A and B and produce a high output, if A > B and zero if A < B.

10. Design a circuit that will produce a PWM output with 25% duty cycle and frequency of 1 KHz.

11. Design a counter that goes through the states 0, 1, 2, 4, 0 using D flipflop.

(4 × 5 = 20 marks)

Part C

Answer section ( a ) or section ( b ) of each question .

12.

(a) Simplify the following boolean function using Quine-Mc Cluskey method.

f (A, B, C, D) = P m (0 , 2 , 3 , 6 , 7 , 8 , 10 , 12 , 13)

Turn over

2 10053

Or

(b) Reduce the following function using Karnaugh map technique and implement using basic gates f (A, B, C, D) = ¯ BD + AB ¯

13.

(a) Implement the following Boolean function using 4:1 multiplexer.

f (A, B, C, D) = P m (0 , 1 , 2 , 4 , 6 , 9 , 12 , 14)

Or

(b) Implement binary to BCD converter using gates.

14.

(a) Design a synchronous decade counter using T-flop flop.

Or

(b) Explain with neat diagram the operation of a 4 bit serial in parallel out shift register.

15.

(a) Design a synchronous counter using JK-flop flop for 4 → 6 → 7 → 3 → 1 → 4.

Or

(b) Explain the procedure of state minimization using merger graph and merger table.

(4 × 10 = 40 marks)