LT1947 - Linear Technology

advertisement

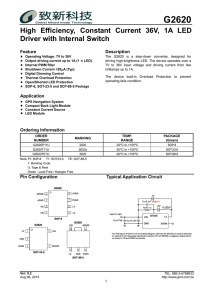

LT1947 Adjustable Output TFT-LCD Triple Switching Regulator U FEATURES DESCRIPTIO ■ The LT®1947 is a highly integrated multiple output DC/DC converter designed for use in TFT-LCD panels. The device contains two independent switching regulators. The main regulator has an adjustable output voltage with an internal 1.1A switch that can generate a boosted voltage as high as 30V. The second regulator’s output is also adjustable up to 30V and can deliver 10mA for positive bias. A simple level-shift charge pump off the main switch node generates the negative bias voltage. An external capacitor sets the delay time from AVDD’s final value to the rising edge at the VON pin. The 3MHz switching frequency allows the use of tiny low profile chip inductors and capacitors throughout, providing a low noise, low cost total solution with all components under 1.2mm in height. The device operates from an input range of 2.7V to 8V and is available in 10-lead MSOP and thermally enhanced 10-lead MSOP packages. ■ ■ ■ ■ ■ ■ ■ ■ ■ ■ Complete Solution Under 1.2mm Develops Three Outputs from a 3.3V or 5V Supply Externally Programmable VON Delay Fixed Frequency Low Noise Outputs All Ceramic Capacitors 3MHz Switching Frequency Fast Transient Response Few External Components Required 2.7V to 8V Input Range Adjustable AVDD and VON Voltages Tiny 10-Lead MSOP and Thermally Enhanced 10-Lead MSOP Packages U APPLICATIO S ■ ■ ■ ■ TFT-LCD Notebook Display Panels TFT-LCD Desktop Monitor Display Panels Digital Cameras Handheld Computers , LTC and LT are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. U TYPICAL APPLICATIO D3 D4 VOFF –8V 10mA C4 0.68µF CERAMIC AVDD 8V 200mA C6 0.68µF L1 3.3µH VIN D1 L2 4.7µH VIN SW1 SW2 C1 2.2µF CERAMIC FB1 D2 VO2 C3 220nF SHUTDOWN R1 53.6k R2 10k LT1947 R3 182k FB2 R4 10k SHDN CT C2 3.3µF CERAMIC ×2 VON GND VON 24V 10mA C5 10nF C1: TAIYO YUDEN LMK316BJ225MD C2: TAIYO YUDEN LMK325BJ335MD ×2 C3: AVX 0.22µF 25V X7R C4, C6: TAIYO YUDEN LMK107BJ684MA D1: MBRM120LT3 D2: CMDSH-3 D3, D4: BAT54S DUAL DIODE L1: SUMIDA CLQ4D103R3 L2: TAIYO YUDEN LB2012B4R7M Start-Up Waveforms VSHDN 5V/DIV VON 20V/DIV AVDD 10V/DIV VOFF 10V/DIV 1947 F01 2ms/DIV 1947 TA01.tif Figure 1. 3.3V Powered TFT-LCD Bias Generator 1947fa 1 LT1947 W W W AXI U U ABSOLUTE RATI GS (Note 1) VIN Voltage ................................................................ 8V CT Voltage.................................................................. 6V SW1, SW2 Voltage .................................................. 36V VON, VO2 Voltage ..................................................... 30V FB1, FB2 .................................................................... 3V SHDN......................................................................... 8V Operating Temperature Range (Note 2) .. – 40°C to 85°C Lead Temperature (Soldering, 10 sec).................. 300°C U U W PACKAGE/ORDER I FOR ATIO ORDER PART NUMBER TOP VIEW FB1 FB2 CT SW1 GND 1 2 3 4 5 11 10 9 8 7 6 VON V02 SHDN SW2 VIN MSE PACKAGE 10-LEAD PLASTIC MSOP EXPOSED PAD (PIN 11) IS GND MUST BE SOLDERED TO PCB TJMAX = 125°C, θJA = 40°C/W LT1947EMSE MSE PART MARKING ORDER PART NUMBER TOP VIEW FB1 FB2 CT SW1 GND 1 2 3 4 5 10 9 8 7 6 VON VO2 SHDN SW2 VIN LT1947EMS MS PACKAGE 10-LEAD PLASTIC MSOP MS PART MARKING TJMAX = 125°C, θJA = 120°C/W LTBQW LTUE Order Options Tape and Reel: Add #TR, Lead Free: Add #PBF, Lead Free Tape and Reel: Add #TRPBF Lead Free Part Marking: http://www.linear.com/leadfree/ Consult LTC Marketing for parts specified with wider operating temperature ranges. ELECTRICAL CHARACTERISTICS The ● denotes the specifications which apply over the full operating temperature range, otherwise specifications are at TA = 25°C. VIN = 3.3V, VSHDN = 3.3V unless otherwise specified. SYMBOL CONDITIONS MIN Input Voltage Range Supply Current SHDN = 2.4V SHDN = 0V FB1 Voltage VIN = 2.7V to 8V MAX 8 UNITS V 9.5 12.5 1 mA µA 1.240 1.225 1.26 ● 1.280 1.295 V V 1.225 1.210 1.26 ● 1.295 1.310 V V 0.01 0.05 %/V FB2 Voltage Reference Line Regulation TYP 2.7 1947fa 2 LT1947 ELECTRICAL CHARACTERISTICS The ● denotes the specifications which apply over the full operating temperature range, otherwise specifications are at TA = 25°C. VIN = 3.3V, VSHDN = 3.3V unless otherwise specified. SYMBOL CONDITIONS Error Amplifier Voltage Gain EA1 and EA2 CT Current Source VFB1 = 1.3V MIN TYP MAX UNITS 100 V/V µA 4 5.5 6.5 CT Threshold to Turn On Q3 1.25 1.28 1.30 V FB1 Voltage to Begin CT Charge 1.17 1.2 1.23 V 1.4 2 A SW1 Current Limit (Note 3) 1.1 SW2 Current Limit (Note 3) 0.35 0.6 1 A SW1 Saturation Voltage ISW1 = 800mA 0.230 0.280 V SW2 Saturation Voltage ISW2 = 300mA 0.3 0.36 V SW1 Maximum Duty Cycle 82 SW2 Maximum Duty Cycle % 85 ● Oscillator Frequency 2.3 % 3 3.5 MHz VON Switch Drop IQ3 = 7mA 160 200 mV SW1 Leakage Current Switch Off, SW1 = 3.3V 0.01 5 µA SW2 Leakage Current Switch Off, SW2 = 3.3V 0.01 5 µA 10 25 µA SHDN Pin Bias Current VSHDN = 2.4V SHDN Pin High Active Mode SHDN Pin Low Shutdown Mode 2.4 V 0.4 Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired. Note 2: The LT1947 is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the – 40°C to 85°C operating V temperature range are assured by design, characterization and correlation with statistical process controls. Note 3: Switch current limit guaranteed by design and/or correlation to static tests. U W TYPICAL PERFOR A CE CHARACTERISTICS 3.3V TFT-LCD Converter Efficiency Supply Current VIN = 2.7V 65 60 55 50 10 –4 CT CURRENT (µA) VIN = 3V SUPPLY CURRENT (mA) 75 70 –2 SHDN = 2.4V VIN = 3.3V 80 EFFICIENCY (%) CT Current Source 12 85 8 6 –6 –8 45 40 35 0 25 50 75 100 125 150 175 200 AVDD LOAD CURRENT (mA) 1947 G01 4 –50 –25 0 25 50 TEMPERATURE (°C) 75 100 1947 G02 –10 –50 –25 0 25 50 TEMPERATURE (°C) 75 100 1947 G03 1947fa 3 LT1947 U W TYPICAL PERFOR A CE CHARACTERISTICS SW2 Current Limit 1.0 1.6 0.8 SW2 CURRENT (A) SW1 CURRENT (A) SW1 Current Limit 1.8 1.4 1.2 1.0 0.6 0.4 0.2 0.8 –50 –25 0 25 50 TEMPERATURE (°C) 75 0 –50 100 –25 0 25 50 TEMPERATURE (°C) 75 1947 G04 1947 G05 Switch 2 Saturation Voltage Switch 1 Saturation Voltage 800 SWITCH 2 SATURATION VOLTAGE (mV) SWITCH 1 SATURATION VOLTAGE (mV) 500 400 25°C 300 90°C 200 –45°C 100 0 25°C 600 90°C 400 –45°C 200 0 0 0.2 0.4 0.6 0.8 1 SWITCH CURRENT (A) 1.2 1.4 0 0.1 0.2 0.3 0.4 SWITCH CURRENT (A) 0.5 1947 G06 Oscillator Frequency 100 OSCILLATOR FREQUENCY (MHz) 3.2 90 80 70 60 50 –50 0.6 1947 G07 SW1 Maximum Duty Cycle SW1 DUTY CYCLE (%) 100 –25 0 25 50 TEMPERATURE (°C) 75 100 1947 G08 3.0 2.8 2.6 2.4 2.2 –50 –25 0 25 50 TEMPERATURE (°C) 75 100 1947 G09 1947fa 4 LT1947 U U U PI FU CTIO S FB1 (Pin 1): Feedback Pin for First Switcher. Connect resistor divider tap here. Set AV DD according to: AVDD = 1.26V(1 + R1/R2). FB2 (Pin 2): Feedback Pin for Second Switcher. Connect resistor divider 2 here and set V ON using: VON = 1.26V (1 + R3/R4) – 160mV. VIN (Pin 6): Input Supply Pin. Must be bypassed with a ceramic capacitor close to the pin. SW2 (Pin 7): VO2 Switch Node. Connect L2 and D2 here. Minimize trace area at this pin to keep EMI down. SHDN (Pin 8): Pull this pin low for shutdown mode. For normal operation, tie to a voltage between 2.4V and 8V. CT (Pin 3): Timing Capacitor Pin. Connect a 10nF capacitor from CT to ground to program a 2.3ms delay from FB1 reaching 1.26V to VON turning on. VO2 (Pin 9): SW2 Output. This node is also internally connected to the emitter of Q3 (see Block Diagram), the high side switch between VO2 and VON. SW1 (Pin 4): AVDD Switch Node. Connect L1 and D1 here (see Figure 1). Minimize trace area at this pin to keep EMI down. VON (Pin 10): This is the delayed output for second Switcher. VON reaches its programmed voltage after the internal timer times out. GND (Pin 5): Ground. Connect directly to local ground plane. Exposed Pad (Pin 11): Ground (MSE package only). The exposed pad must be soldered to the PCB and electrically connected to ground. 1947fa 5 LT1947 W BLOCK DIAGRA VIN GND SHDN VIN 5.5µA – 28mV +– R Q1 REF + – REF Q3 ∑ REF VO2 + 0.01Ω + SLOPE 1 OSC – FB2 – OSC SLOPE 1 SLOPE 2 1.26V REFERENCE AND UNDERVOLTAGE LOCKOUT SW2 S + 3MHz OSCILLATOR Q + Q4 + SW1 S + – VON OSC – FB1 CT SHUTDOWN R Q Q2 + REF REF ∑ + 0.03Ω + SLOPE 2 1947BD 1947fa 6 LT1947 U OPERATIO To best understand operation of the LT1947, please refer to the LT1947 Block Diagram. The device contains two switching regulators, a timer and a high side switch. Three outputs can be generated: an adjustable AVDD output, a charge-pumped inversion of the AVDD output called VOFF, and a time delayed adjustable output called VON. Q3 keeps VON off for an externally set time interval, set by a capacitor connected to the CT pin. C = (5.5µA • tDELAY)/1.28V A 10nF capacitor results in approximately 2.3ms of delay. Layout Hints The high speed operation of the LT1947 mandates careful attention to layout for proper performance. Be sure to keep input capacitor C1 as close as possible to the IC and minimize trace area and length at the SW and FB pins. Always use a ground plane under the switching regulator to minimize interplane coupling. Figure 2 shows the recommended component placement. The switching frequency of both switchers is 3MHz, set internally. The switchers are current mode and are internally compensated. The main AVDD switcher is current limited at 1.1A, while the second VON switcher is limited to 350mA. They share the same 1.26V reference voltage. When the input voltage is below approximately 2.7V, an undervoltage lockout circuit disables switching. The exposed pad of the MSE package must be soldered to the PCB and electrically connected to ground. Thermal vias to a large ground plane will lower the thermal resistance. When AVDD is less than its final voltage, Q4 is turned on, holding the CT pin at ground. When AVDD reaches final value, Q4 lets go of the CT pin, allowing the 5.5µA current source to charge the external capacitor, CT. When the voltage on the CT pin reaches 1.28V, Q3 turns on, connecting VO2 to VON. Capacitor value can be calculated using the following formula: Soft-Start For applications requiring soft-start, a circuit consisting of RSS and CSS tied to the SHDN pin can be used, as shown in Figure 3. For a combination of 33.2k/33nF, AVDD rises to its final value in approximately 3ms. R3 GND R4 R1 VON R2 1 10 LT1947 C5 L1 2 9 3 8 4 7 5 6 SHDN C1 L2 VIN D2 C6 C3 D1 D3 D4 GND C4 AVDD VIN C2 VOFF 1947 F02 Figure 2. Recommended Component Placement 1947fa 7 LT1947 U OPERATIO D3 D4 VOFF –8V 10mA C4 0.68µF CERAMIC AVDD 8V 200mA C6 0.68µF L1 3.3µH VIN D1 L2 4.7µH VIN SW1 SW2 C1 2.2µF CERAMIC VSS FB1 D2 VO2 C3 220nF RSS 33.2k R1 53.6k R2 10k LT1947 R3 182k FB2 R4 10k SHDN CT C2 3.3µF CERAMIC ×2 VON 24V 10mA VON GND C5 10nF CSS 33nF VOFF 1947 F03 C1: TAIYO YUDEN LMK316BJ225MD C2: TAIYO YUDEN LMK325BJ335MD ×2 C3: AVX 0.22µF 25V X7R C4, C6: TAIYO YUDEN LMK107BJ684MA D1: MBRM120LT3 D2: CMDSH-3 D3, D4: BAT54S DUAL DIODE L1: SUMIDA CLQ4D103R3 L2: TAIYO YUDEN LB2012B4R7M Figure 3. RSS and CSS at SHDN Pin Provide Soft-Start VSS 5V/DIV VON 20V/DIV AVDD 10V/DIV VOFF 10V/DIV 5ms/DIV 1947 F04.tif Figure 4. Start-Up Waveforms with Soft-Start Circuit Added 1947fa 8 LT1947 U TYPICAL APPLICATIO S TFT-LCD Bias Generator: 12V, 20V, – 6V Output 34k Q1 BAT54S D3 C6 R1 86.6k SW1 VIN SW2 C1 4.7µF AVDD 12V 120mA D1 L2 4.7µH 34k C4 L1 4.7µH VIN 3.3V Q2 D4 C2 3.3µF CERAMIC ×2 FB1 D2 VO2 C3 0.22µF R2 10k LT1947 R3 147k FB2 R4 10k SHUTDOWN VON 20V 10mA VON GND SHDN CT VOFF –6V 20mA C5 10nF C1: TAIYO YUDEN JMK316BJ475MD 4.7µF 6.3V X7R C2: TAIYO YUDEN LMK325BJ335MD 3.3µF 10V X7R ×2 C3: AVX 0.22µF 25V X7R C4, C6: TAIYO YUDEN LMK107BJ684MA 0.68µF 10V X7R D1: MBRM120 D2: CMDSH-3 L1: SUMIDA CLQ4DI04R7 L2: TAIYO YUDEN LB2012B4R7M Q1: MMBT3904 NPN Q2: MMBT3906 PNP 1947 TA02 TFT-LCD Bias Generator: 10V, 24V, – 6V Output BAT54S D3 D1 L2 4.7µH SW1 VIN SW2 C4 0.68µF AVDD 10V 150mA R1 69.8k FB1 D2 VO2 C3 220nF SHUTDOWN VOFF –6V 10mA C6 220nF L1 3.3µH VIN 3.3V C1 2.2µF CERAMIC D4 R2 10k LT1947 R3 182k FB2 R4 10k SHDN CT C2 3.3µF CERAMIC ×2 VON GND VON 24V 10mA C5 10nF C1: TAIYO YUDEN LMK316BJ225MD 2.2µF X7R C2: TAIYO YUDEN LMK325BJ335MD 3.3µF X5R C3, C6: AVX 0.22µF CERAMIC X7R C4: TAIYO YUDEN EMK212BJ684MD 1947 TA04 D1: MBRM120 D2: CMDSH-3 L1: SUMIDA CLQ4DI03R3 L2: TAIYO YUDEN LB2012B-4R7M 1947fa 9 LT1947 U PACKAGE DESCRIPTIO MS Package 10-Lead Plastic MSOP (Reference LTC DWG # 05-08-1661) 0.889 ± 0.127 (.035 ± .005) 5.23 (.206) MIN 3.20 – 3.45 (.126 – .136) 3.00 ± 0.102 (.118 ± .004) (NOTE 3) 0.50 0.305 ± 0.038 (.0197) (.0120 ± .0015) BSC TYP RECOMMENDED SOLDER PAD LAYOUT 0.254 (.010) 10 9 8 7 6 3.00 ± 0.102 (.118 ± .004) (NOTE 4) 4.90 ± 0.152 (.193 ± .006) DETAIL “A” 0.497 ± 0.076 (.0196 ± .003) REF 0° – 6° TYP GAUGE PLANE 1 2 3 4 5 0.53 ± 0.152 (.021 ± .006) DETAIL “A” 1.10 (.043) MAX 0.86 (.034) REF 0.18 (.007) SEATING PLANE 0.17 – 0.27 (.007 – .011) TYP 0.50 (.0197) NOTE: BSC 1. DIMENSIONS IN MILLIMETER/(INCH) 2. DRAWING NOT TO SCALE 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX 0.127 ± 0.076 (.005 ± .003) MSOP (MS) 0603 1947fa 10 LT1947 U PACKAGE DESCRIPTIO MSE Package 10-Lead Plastic MSOP (Reference LTC DWG # 05-08-1663) BOTTOM VIEW OF EXPOSED PAD OPTION 2.794 ± 0.102 (.110 ± .004) 5.23 (.206) MIN 0.889 ± 0.127 (.035 ± .005) 1 2.06 ± 0.102 (.081 ± .004) 1.83 ± 0.102 (.072 ± .004) 2.083 ± 0.102 3.20 – 3.45 (.082 ± .004) (.126 – .136) 10 0.50 0.305 ± 0.038 (.0197) (.0120 ± .0015) BSC TYP RECOMMENDED SOLDER PAD LAYOUT 3.00 ± 0.102 (.118 ± .004) (NOTE 3) 3.00 ± 0.102 (.118 ± .004) (NOTE 4) 4.90 ± 0.152 (.193 ± .006) 0.254 (.010) DETAIL “A” 0° – 6° TYP 1 2 3 4 5 GAUGE PLANE 0.53 ± 0.152 (.021 ± .006) DETAIL “A” 0.18 (.007) 0.497 ± 0.076 (.0196 ± .003) REF 10 9 8 7 6 SEATING PLANE 0.86 (.034) REF 1.10 (.043) MAX 0.17 – 0.27 (.007 – .011) TYP 0.50 (.0197) BSC 0.127 ± 0.076 (.005 ± .003) MSOP (MSE) 0603 NOTE: 1. DIMENSIONS IN MILLIMETER/(INCH) 2. DRAWING NOT TO SCALE 3. DIMENSION DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS. MOLD FLASH, PROTRUSIONS OR GATE BURRS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 4. DIMENSION DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS. INTERLEAD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.152mm (.006") PER SIDE 5. LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.102mm (.004") MAX 1947fa Information furnished by Linear Technology Corporation is believed to be accurate and reliable. However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights. 11 LT1947 U TYPICAL APPLICATIO TFT-LCD Bias Generator: 7.5V, 15V, – 10V Output C7 0.68µF C6 0.68µF D7 C8 D3 D5 D4 BAT54S C4 0.68µF D6 34k Q1 34k VOFF –10V 20mA L1 3.3µH VIN 3.3V D1 L2 4.7µH C1 1µF CERAMIC ×2 SW2 R1 49.9k FB1 D2 VO2 BAT54S C3 0.68µF SHUTDOWN SW1 VIN AVDD 7.5V 200mA R2 10k LT1947 R3 105k FB2 R4 10k SHDN CT C2 3.3µF CERAMIC ×2 VON GND VON 15V 10mA C5 10nF C1: TAIYO YUDEN JMK107BJ105MA 1µF 6.3V X7R ×2 C2: TAIYO YUDEN LMK325BJ335MD 3.3µF 10V X7R ×2 C3, C7, C8: TAIYO YUDEN EMK212BJ684MD 0.68µF 16V X7R C4, C6: TAIYO YUDEN LMK107BJ684MA 0.68µF 10V X5R D1: MBRM120 1947 TA03 D2: CMDSH-3 D7: MMBZ5240 10V ZENER L1: SUMIDA CLQ4D103R3 L2: TAIYO YUDEN LB2012B-4R7M Q1: MMBT3906 PNP RELATED PARTS PART NUMBER DESCRIPTION COMMENTS LT1310 1.5A ISW, 4.5MHz, High Efficiency Step-Up DC/DC Converter VIN = 2.75V to 18V, VOUT Max = 35V, IQ = 12mA, ISHDN = <1µA, MS10E LT1613 550mA ISW, 1.4MHz, High Efficiency Step-Up DC/DC Converter VIN = 0.9V to 10V, VOUT Max = 34V, IQ = 3mA, ISHDN = <1µA, ThinSOT LT1615/LT1615-1 300mA/80mA ISW, Constant Off-Time, High Efficiency Step-Up DC/DC Converter VIN = 1.2V to 15V, VOUT Max = 34V, IQ = 20µA, ISHDN = <1µA, ThinSOT LT1940 Dual Output 1.4A IOUT, Constant 1.1MHz, High Efficiency Step-Down DC/DC Converter VIN = 3V to 25V, VOUT Min = 1.2V, IQ = 2.5mA, ISHDN = <1µA, TSSOP-16E LT1944 Dual Output 350mA ISW, Constant Off-Time, High Efficiency Step-Up DC/DC Converter VIN = 1.2V to 15V, VOUT Max = 34V, IQ = 20µA, ISHDN = <1µA, MS10 LT1944-1 Dual Output 150mA ISW, Constant Off-Time, High Efficiency Step-Up DC/DC Converter VIN = 1.2V to 15V, VOUT Max = 34V, IQ = 20µA, ISHDN = <1µA, MS10 LT1945 Dual Output, Pos/Neg 350mA ISW, Constant Off-Time, High Efficiency Step-Up DC/DC Converter VIN = 1.2V to 15V, VOUT Max = ±34V, IQ = 20µA, ISHDN = <1µA, MS10 LT1946/LT1946A 1.5A ISW, 1.2MHz/2.7MHz, High Efficiency Step-Up DC/DC Converter VIN = 2.45V to 16V, VOUT Max = 34V, IQ = 3.2mA, ISHDN = <1µA, MS8 LT1949/LT1949-1 550mA ISW, 600kHz/1.1MHz, High Efficiency Step-Up DC/DC Converter VIN = 1.5V to 12V, VOUT Max = 28V, IQ = 4.5mA, ISHDN = <25µA, MS8, S8 LTC3400/LTC3400B 600mA ISW, 1.2MHz, Synchronous Step-Up DC/DC Converter VIN = 0.85V to 5V, VOUT Max = 5V, IQ = 19µA/300µA, ISHDN = <1µA, ThinSOT LTC3401 1A ISW, 3MHz, Synchronous Step-Up DC/DC Converter VIN = 0.5V to 5V, VOUT Max = 6V, IQ = 38µA, ISHDN = <1µA, MS10 LTC3402 2A ISW, 3MHz, Synchronous Step-Up DC/DC Converter VIN = 0.5V to 5V, VOUT Max = 6V, IQ = 38µA, ISHDN = <1µA, MS10 1A ISW, 3MHz, Low VOUT, Synchronous Step-Up VIN = 0.5V to 5V, VOUT Max = 6V, IQ = 38µA, ISHDN = <1µA, MS10 DC/DC Converter LTC3423 LTC3424 2A ISW, 3MHz, Low VOUT, Synchronous Step-Up DC/DC Converter VIN = 0.5V to 5V, VOUT Max = 6V, IQ = 38µA, ISHDN = <1µA, MS10 1947fa 12 Linear Technology Corporation LT/LT 0605 REV A • PRINTED IN USA 1630 McCarthy Blvd., Milpitas, CA 95035-7417 (408) 432-1900 ● FAX: (408) 434-0507 ● www.linear.com © LINEAR TECHNOLOGY CORPORATION 2001