Lab 1: Using LTSpice or Multisim for Simulation

advertisement

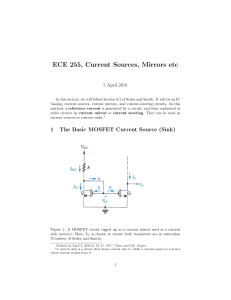

1 Lab 01: Current Mirrors (20 points) Objectives The purpose of this lab is to build MOSFET based Current Mirror Circuits that provide stable and constant DC current for biasing. 1.0 Basic Current Mirror Fig. 1 Simple MOSFET (NMOS) current mirror and its test circuit In the basic current mirror circuit, for a matched pair for transistors, IO=IREF. Fig. 1 shows a simple NMOS based current mirror with its test circuit (Fig. 7.22). Here Vdd=10 V, R=1 kΩ, Rp=potentiometer. Q1 and Q2 should be a matched pair of NMOS transistors (you will have to find the two that are closely matched by trial and error). Test voltage Vo is used to determine range of output resistance Ro. You can use any NMOS transistors that meet the objective (recommendation: 2N7000TA or ALD1116 (NMOS Array)). You will need to look up the datasheet to determine Vtn and VA 1.1 Design 1. Calculate the value of VGS required to obtain IREF = 1 mA (see Fig. 7.22 and example 7.5) 2. Calculate the total resistance RT needed at the drain of Q1 in order to provide IREF=1mA (see example 7.5). Next, determine the range of RP in order to meet this goal. Note that RT = RP + R. 3. Calculate the value of gm for transistor Q1 when it is biased under these conditions. 4. Calculate the lowest allowable value of VO for the current mirror when it is biased under these conditions. 5. What is the output resistance, Ro? L1: Calculate the total resistance RT, RP, VGS, gm, and RO. Weber State University EE3120 Microelectronics II Suketu Naik 2 1.2 Simulation: Now, simulate the circuit by setting Rp to four values: Rp for IREF=1mA (found in previous section), IREF=2mA, IREF=4mA, IREF=6mA. Note that while Q2 is in saturation changing Vo should have minimal/no effect on IO. (a) Measure VGS. (b) Measure Io by varying Vo from 0 to 10 V in 500 mV increments. You can use DC sweep. Plot Io vs Vo (Place cursors around expected Vo, Io = 1 mA in the saturation region and calculate slope (1/Ro) for a small range of Vo. Alternatively, you can save the simulated waveforms in a file; then import the file into Matlab or Excel. Using this data, find the small-signal output resistance, Ro in the saturation region. L2: Simulate VGS and the output resistance RO and IREF = 1mA, 2mA, 4mA, 6mA. 1.3 Experiment: (a) Build the circuit and adjust values as necessary. MOSFETs must be handled with care. To avoid the damage, try to avoid touching the gate terminal as the static charge on your fingers can be enough to blow the gate capacitor. When you place the MOSFETs in your bread board, take care to get the drain and source oriented properly as these discrete MOSFETs do not have interchangeable sources and drains. Repeat 1.2 and find the measured values for VGS and Ro. Obtain as many points as possible for your sweep. Plot Io vs Vo. You may want to plot the measured data and simulated data together to see the difference. Don’t forget to check the multi-meter mode before you measure a current or voltage, if it is set incorrectly you will blow a fuse! Is there a mismatch between the transistors you picked? How does it affect the current mirror gain (Io/IREF)? Would you expect this mistmatch to be better or worse for an integrated implementation of the basic current mirror? L3: Measure VGS and the output resistance RO for IREF = 1mA, 2mA, 4mA, 6mA. In your report, create a table with calculated, simulated and measured values. Weber State University EE3120 Microelectronics II Suketu Naik 3 2.0 Advanced Current Mirror We will now modify the circuit of Fig. 1 and create Wilson Current Mirror (see section 7.5.4) as shown in Fig. 2. The advantage of Wilson current mirror over the basic current mirror is that it has a higher output resistance (an ideal current source should have an infinite impedance). Fig. 2 Advanced MOSFET (NMOS) current mirror: Wilson current mirror In the Wilson current mirror circuit, for a matched pair for transistors, IO =IREF. Repeat the steps in section 1 (design, simulation, and experiment). 2.1 Design Follow the problem 7.74. Calculate the total resistance RT needed at the collector of Q1 in order to provide IREF=1mA. Next, determine the range of RP in order to meet this goal. Note that RT=RP+R. What is the output resistance, Ro (see eq.7.82)? How does it compare with basic current mirror? L5: Calculate the total resistance RT, RP, and RO. 2.2 Simulation Now, simulate the circuit by setting Rp for IREF=1mA (found in previous section. Note that while Q3 is in saturation changing Vo should have minimal/no effect on IO. (c) Measure VGS for both Q3-Q4 and Q1-Q2 pairs. Weber State University EE3120 Microelectronics II Suketu Naik 4 (d) Measure Io by varying Vo from 0 to 10 V in 500 mV increments. You can use DC sweep. Plot Io vs Vo (Place cursors around expected Vo, Io = 1 mA in the saturation region and calculate slope (1/Ro) for a small range of Vo. Alternatively, you can save the simulated waveforms in a file; then import the file into Matlab or Excel. Using this data, find the small-signal output resistance, Ro in the saturation region. L6: Simulate VGS and the output resistance RO for IREF = 1mA. 2.3 Experiment: Build the circuit and adjust values as necessary. Repeat 2.2 and find the measured values. (a) Measure Io by varying Vo from 0 to 10 V in 500 mV increments. Plot Io vs Vo and calculate Ro around Io = 1 mA. L7: Measure the output resistance RO. Is the output resistance of Wilson current source higher or lower than the basic current mirror? Is this expected? In your report, create a table with calculated, simulated and measured values. Weber State University EE3120 Microelectronics II Suketu Naik