Mixed Swing Techniques for Low Energy/Operation Datapath Circuits

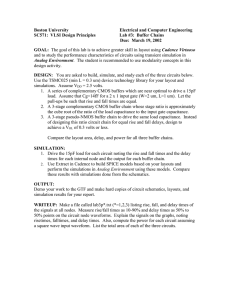

advertisement