as a PDF

advertisement

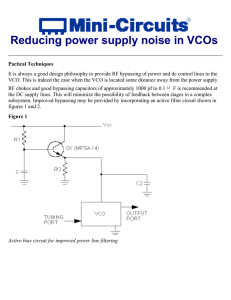

World Applied Sciences Journal 7 (7): 829-832, 2009 ISSN 1818-4952 © IDOSI Publications, 2009 A High Performance 5.4 GHz 3V Voltage Controlled Oscillator in 0.35-≥m BiCMOS Technology 1 1 2 M.H. Seyedi , H. Mokari and A.Bazdar 1 Department of Electrical Engineering, Islamic Azad University (IAU), Science and Research Campus, Tehran, Iran 2 Department of Electrical Engineering, Islamic Azad University (IAU), Urmia Campus, Urmia, Iran Abstract: This paper presents a fully integrated 5.4-GHz CMOS Voltage-controlled Oscillator (VCO) with a low phase noise and ultra linear VCO gain (Kvco) in 0.35-µm SiGe (Silicon Germanium) BiCMOS technology. In order to increase the linearity of the VCO, a resonant circuit is proposed that consists of four parallel p-n junction varactor pairs. The VCO operate at a bias current of 3.13 mA and a supply voltage of 3.0 V with a corresponding DC power consumption of about 9.3 mW. The VCO gain changes from 214 MHz/V to 271 MHz/V. The CMOS VCO shows a fine frequency tuning range of 786 MHz. In addition, a low phase noise of-120.976 dBc/Hz at 1 MHz offset was obtained. Key word: CMOS VCO p-n junction varactor Kvco SiGe BiCMOS technology VCO gain voltagecontrolled oscillator • • • INTRODUCTION • • noise with low DC power consumption. Many researches pay attention at phase noise analysis and studying the different noise sources in LC oscillators and give good prediction for phase noise [5, 6]. So the VCO gain (the so-called Kvco) is an important control parameter in the design of phase locked loops [7] that few research topics focus on it [8, 9]. Trade-off between phase noise and VCO gain is frequently the object of engineering [10]. In this paper, a fully differential Voltage-controlled Oscillator (VCO) with a low phase noise and ultra linear Kvco is presented for 5-GHz wireless applications. The VCO has been implemented in 0.35-µm SiGe BiCMOS process technology. CMOS topology has been adopted in this research. The MOS VCO compensates the nonlinearity of VCO gain while maintaining low phase noise, low power and wide tuning range. In recent years, among the communication applications that have emerged in the consumer market, Wireless Local Area Network (WLAN) is the most popular one. WLAN could serve as high-speed links with 1 Mbps to 55 Mbps data rates in office buildings, hospitals, factories, etc. Increased demand for wireless communication motivates a growing interest in monolithic personal communication transceivers [1]. A fully integrated transceiver is effective element for providing high-speed wireless network communication. The growing development and popular application of WLANs and short -range wireless communications is driving a need for higher integration degree in transceivers in order to achieve lower cost, low power consumption and small size. Fully integrated Voltage-controlled Oscillator (VCO) is one of the most important and challenging building blocks in a transceiver system. Its performance often determines whether the entire system will meet the specifications or not. The VCO generates the Local Oscillator (LO) carrier signal used to convey RF signals in transceivers. The LO is typically implemented as a Phase-locked Loop (PLL) [2-4]. The important requirements in VCOs for many of the basic performance characteristics of a transceiver are a sufficient frequency tuning range and a low phase GENERAL CONCEPTIONS In this paper, VCO gain and phase noise of differential MOS VCO are considered. The VCO gain is the derivative of the oscillation frequency with respect to the control voltage as shown in equation (1) Kvco(Vctrl ) = ∂fosc (Vctrl ) ∂Vctrl Corresponding Author: Dr. M.H. Seyedi, Department of Electrical Engineering, Islamic Azad University (IAU), Science and Research Campus, Tehran, Iran 829 (1) World Appl. Sci. J., 7 (7): 829-832, 2009 where, fosc is the oscillation frequency and Vctrl is the control voltage of the varactor. If the oscillation frequencies are linearly controlled by the control voltage, then Kvco would be completely linear. Thus, oscillation frequency is expressed as equation (2) f osc = 1 2π LC (2) Fig. 2: The cross-section and symbolic representation of the p-n junction varactor unit where, L and C are the inductance of spiral inductor and capacitance of the resonator (mainly varactor capacitance), respectively. The most important sources for phase noise performance in MOS VCO are the parasitic resistance of resonator and the oscillation amplitude of VCO. The parasitic resistance of resonator is not effective for the types of VCO topology. It only depends on the process and the output amplitude strongly depends on circuit topology. Because the linearity of any device is different by itself. Finally, all noise sources are combined to obtain the well-known Leeson's formula as equation (3) 2kT.R eff .F ωosc 2 L(ωm ) = ( ) Vamp 2 ωm resonant circuit. Available integrated varactors are as follow: a diode capacitor and a MOS capacitor. A p-n junction varactor is typically formed by a p+/n-well junction with its junction capacitance being modulated by varying its reverse biasing voltage. The diode capacitance is dictated by the doping profile of the p-n junction. Figure 2 shows the cross-section and symbolic representation of the junction varactor unit. The structure of the p-n junction varactor is actually a diode with reversed bias. The voltage-level-shift circuit, which consists of diode-connected pMOS transistors, sequentially turns on each varactor pair. Since the flicker noise of pMOS transistors is lower than that of nMOS transistors, pMOS transistors are adopted for this circuit. (3) VCO DESIGN where Reff, Va mp and F are parasitic resistance of resonator, oscillation amplitude of VCO and factor which characterizes the phase noise performance of the oscillator, respectively. Figure 3 depicts the equivalent circuit of the MOS VCO core. The VCO are designed using cross-coupled configurations. It consists of nMOS (M1 and M2) and pMOS (M3 and M4) cross-coupled pairs, the resonant circuit and a pMOS transistor for biasing current source. A pair of coupled nMOS transistors and a pair of coupled pMOS transistors are used in the positive feedback to provide a negative resistance. The cross-coupled configuration has two advantages: first, with the addition of the pMOS pair, it is possible to compensate the loss of the resonant circuit with less current consumption. Second, although 1/f noise is much larger in CMOS devices than that of silicon or SiGe bipolar devices, its effect on VCO phase noise can be minimized by using both ratio between nMOS and pMOS transistors, the degradation in phase noise due to l/f noise can be significantly reduced [11]. Another way to reduce l/f noise is to increase the size of CMOS devices. Larger CMOS devices produce smaller 1/f noise. However, too large CMOS devices can lead to more fix parasitic capacitance. Thus, it would reduce the frequency tuning range of VCO. Sizes of both nMOS and pMOS directly affect the current, which must be biased. RESONANT CIRCUIT Figure 1 shows the resonant circuit proposed in this paper, which includes four parallel p-n junction varactor pairs, a spiral inductor and a voltage-level-shift circuit. The frequency variation is achieved by a varactor. Varactor is a commonly used tuning component in VCO circuits, because it is more convenient to tune the value of a capacitor compared to an inductor in a Fig. 1: Equivalent circuit of the resonator 830 World Appl. Sci. J., 7 (7): 829-832, 2009 Table 1: Summary of the simulation results Process 0.35-µm SiGe BiCMOS Phase noise at 600 kHz offset -115.742 dBc/Hz Phase noise at 1.0 MHz offset -120.976 dBc/Hz Phase noise at 3.0 MHz offset -131.490 dBc/Hz Kvco ratio a 1.26 Oscillation Frequency 4.6 ~ 5.4 GHz Current Consumption 3.13 mA a. Kvco ratio is the ratio of the maximum value of Kvco to the minimum value of Kvco Fig. 3: Equivalent circuit of the MOS VCO core Fig. 5: Simulated Kvco of the VCO Fig. 4: Phase noise characteristic of the VCO SIMULATION RESULTS In this paper, the VCO circuit was simulated using Agilent ADS simulator. The number of p-n junction diode units and stages were optimized so that linear Kvco with a center frequency of 5.1 GHz is generated. The VCO core circuit draws 3.13 mA of DC current from a supply voltage of 3.0 V. The achieved phase noise level is -115.742 dBc/Hz at 600 kHz offset from center frequency. In addition, the simulated VCO has a phase noise of-120.976 dBc/Hz at a 1.0 MHz offset and a phase noise of-131.490 dBc/Hz at a 3.0 MHz offset. The simulated Fig. 6: Phase noise at 1 MHz offset Phase noise of VCO is shown in Fig. 4. The dependence of the calculated Kvco on the control voltage is depicted in Fig. 5. The VCO gain changes from 214 MHz/V to 271 MHz/V. The ratio of the maximum Kvco to its minimum value in the extra linear VCO is 1.26. The phase noise performance of the VCO is stable with respect to the variation of the control voltage, as 831 World Appl. Sci. J., 7 (7): 829-832, 2009 2. Shin, Y., T. Kim, S. Kim, S. Jang and B. Kim, 2007. A Low Phase Noise Fully Integrated CMOS LC VCO Using a Large Gate Length pMOS Current Source and Bias Filtering Technique for 5-GHz WLAN. International Symposium on Signals, Systems and Electronics, ISSSE apos; 07, 2007, pp: 521-524. 3. Darade, B. and T. Parmar, 2005. Low Phase Noise Fully Integrated VCO. Presented in Research Scholars Forum, 18th IEEE International Conference on VLSI Design 2005, Calcutta. 4. Mostafa, M.A.L., S. Tuncer and G. Luff, 2004. Low Power Low Phase Noise 3.9 GHz SiGe VCO whth Data Modulation Correction Loop. IEEE RFIC Symposium 2004, Digest of Papers, pp: 273-276. 5. Rael, J.J. and A.A. Abidi, 2000. Physical Processes Of Phase Noise in Differentia l LC Oscillators. IEEE Custom Integrated Circuits Conf., 25: 1-4. 6. Bemy, A.D., A.M. Niknejad and R.G. Meyer, 2003. A Wideband Low-Phase-Noise CMOS VCO. Custom Integrated Circuits Conference, 2003. Proceedings of the IEEE 2003, pp: 553-555. 7. Razavi, B., 1997. RF Microelectronics. Prentice Hall. 8. Kurachi, S., T. Yoshimasu, H. Liu, N. Itoh and K. Yonemura, 2007. A SiGe BiCMOS VCO IC with Highly Linear Kvco for 5-GHz-Band Wireless LANs. IEICE Transactions on Electronics, pp: 1228-1233. 9. Zhang, H., G. Chen and N. Li, 2005. A 2.4-GHz linear-tuning CMOS LC voltage-controlled oscillator. Proc. ASP-DAC 2005. Asia and South Pacific, 2: 799-802. 10. Ogawa, T., I. Kyu, H. Kondoh and S. Takatani, 2001. A fully MMIC transceiver module for 5 GHz wireless communications. In IEEE GaAs IC Symp. Dig., pp: 33-36. 11. Lee, T. and A. Hajimiri, 2000. Oscillator Phase Noise: A Tutorial. IEEE Journal of Solid-State Circuits, 35 (3): 326-336. 12. Miram, J., T. Divel, S. Ramet, J. Begueret and Y. Deval, 2004. Distribute MOS varactor biasing for VCO gain equalization in 0.13µm CMOS technology. IEEE RFIC Symposium 2004, Digest of Papers, pp: 131-134. Fig. 7: Tuning characteristic of the VCO shown in Fig. 6. The linear tuning of the structure corves 786 MHz range. The oscillation frequency was changed from 4.642 GHz to 5.428 GHz with a control voltage of from 0.9 V to 2.5 V. It is observed that the oscillation frequencies are linearly controlled by the control voltage. Figure 7 illustrates tuning characteristic of the core VCO. Table 1. summarizes the simulation results of the reportd VCO. CONCLUSION A fully differential low phase noise and extra linear CMOS VCO with oscillation frequencies around 5.1 GHz has been demonstrated using 0.35 -µm SiGe BiCMOS technology. To realize a low phase noise and extra linear Kvco cross-coupled CMOS configuration and a resonant circuit with parallel junction varactor pairs were proposed in this paper. The designed VCO exhibits low phase noise of-120.976 dBc/Hz at 1 MHz offset. The simulated Kvco of VCO is from 214 MHz/V to 271 MHz/V. The proposed MOS VCO shows better performance according to the current consumption, the phase noise and linear VCO gain compared with linear VCOs published using p-n junction [8] or MOS varactors [12] and or both p-n junction and MOS varactors [9] in the previous papers. REFERENCES 1. Gray, P.R. and R.G. Meyer, 1995. Future Direction in Silicon ICs for RF Personal Communications. ClCC Dig. Tech. Papers, pp: 83-90. 832