Capabilities

advertisement

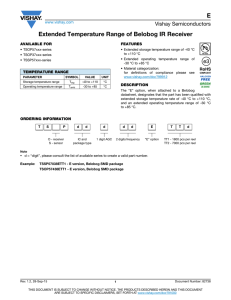

V i s h ay I n t e rt e c h n olog y, I n c . I INNOVAT AND TEC O L OGY AuSn Series N HN LASER DIODE SUBSTRATE MOUNTS O 19 62-2012 Resistors - Deposited Gold Tin Thin Film Patterned Substrates with Deposited Gold/Tin Pads Key Benefits • • • • • • Gold-tin compositions available from 70/30 to 80/20 Gold-tin composition controlled to ± 2 wt% Replace gold-tin preforms Lot-to-lot deposited gold-tin: thickness of 6 µm typical Pad tolerance to ± 0.0002 in. Freeze time: 120 s at 320 ºC APPLICATIONS • • • • • • Laser diode sub-mounts Fiber optic pump lasers Optical transmitters Optical receivers Optical transceivers Optical TOSA/ROSA packages Resources • Datasheet: AuSn Series - http://www.vishay.com/doc?61081 • For technical questions contact efi@vishay.com One of the World’s Largest Manufacturers of Discrete Semiconductors and Passive Components Capabilities 1/2 VMN-PL0464-1202 This document is subject to change without notice. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000 V i s h ay I n t e rt e c h n olog y, I n c . AND TEC I INNOVAT O L OGY AuSn Series N HN LASER DIODE SUBSTRATE MOUNTS O 19 62-2012 Deposited Gold-Tin Vishay Electro-Films (VEFI) has developed a proprietary technique to enable the sputter deposition of gold-tin solder with wt% ranging from 70/30 to 80/20 while maintaining tolerances tighter than ± 2 % wt and control of film thickness to ± 0.1 µm. Gold-Tin Composition and Thickness For best performance, Vishay recommends using the 80/20 alloy when possible; gold-tin with an 80/20 composition is deposited exactly at the eutectic point, allowing reflow at minimum temperature. However, in cases where the backside metal on die being soldered includes a relatively thick layer of gold, alloy modification is required to ensure proper assembly. During reflow, gold on the backside of the die dissolves into the solder resulting in gold enrichment of the alloy; this enrichment of the solder has the unwanted effect of dramatically increasing the reflow temperature. To eliminate the unwanted increase in reflow temperature, the wt% of gold in the solder can be reduced to create a tin-rich solder. During reflow, the resultant is the desired 80/20 alloy. The gold-tin deposition process allows films with thickness ranging between 3 µm and 8 µm with a tolerance of ± 0.1 µm. Conductor Pattern to Edge Clearance AuSn Pad to Die Clearance Conductor Pattern Line/Gap Critical Dimension 2 mil min 1 mil min 2 mil min 1 mil min DIE AuSn Pad to Copper Pattern Edge Clearance Assembled Die AuSn Die Pad Conductor Pattern Capabilities Ceramic Substrate 3 mils min Via Edge to Pad Edge Solid filled vias Via Center to Center 2/2 Via Edge to Substrate Edge Resistors - Deposited Gold Tin This capability allows deposition of customer AuSn compositions that can be used to fine-tune assembly processes to meet the most demanding requirements; the tight composition tolerance eliminates the need to adjust reflow process parameters to compensate for variations in solder composition. VMN-PL0464-1202 This document is subject to change without notice. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000