SDT122 53mm / 4.0kV THYRISTOR

advertisement

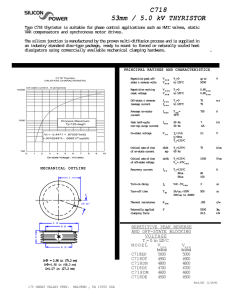

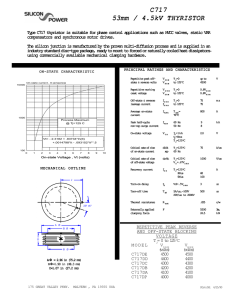

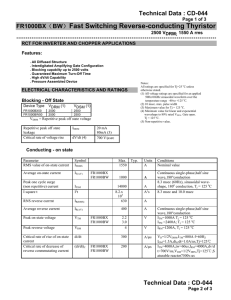

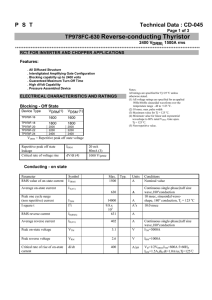

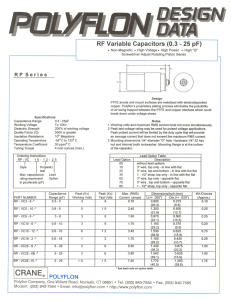

SDT122 53mm / 4.0kV THYRISTOR Type SDT122 thyristor is suitable for phase control applications such as HVDC valves, static VAR compensators and synchronous motor drives. The silicon junction is manufactured by the proven multi-diffusion process and is supplied in an industry standard disc-type package, ready to mount to forced or naturally cooled heat dissipators using commercially available mechanical clamping hardware. ON-STATE CHARACTERISTIC Process Maximum 8 ms Sine Pulses On-State Voltage, Vt (V) 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 100 Initial Tj PRINCIPAL RATINGS AND CHARACTERISTICS Repetitive peak offstate & reverse volts VD R M VR R M T J=0 to 125oC up to 4000 Repetitive working crest voltage VD W M VD R M T J=0 to 125oC 0.8VD R M 0.8VR R M Off-state & reverse leakage current ID W M IR W M T J=0 to 125oC 75 75 ma Average on-state current IT(AV) T case= 70oC 950 A Peak half-cycle non-rep surge current IT S M 60 Hz 50 Hz On-state voltage VT M IT =1kA tP=8ms T J=125oC 1.60 V Critical rate of rise of on-state current di/dt rep T J=125oC 60 Hz 75 A/us Critical rate of rise of off-state voltage dv/dt T J=125oC V D = .8VD R M 1000 V/us Recovery current IR M T J=125oC 2A/us 5A/us 60 110 16.0 14.7 V kA 125 C 25 C 1000 On-State Current, It (A) 10000 95f: MECHANICAL OUTLINE J CL CL 2 0° ±5 ° A Turn-on delay td Vd=.5VD R M 3 us Turn-off time T off 5A/us,-100V 20V/us to 2000V 500 us Thermal resistance R thJC .025 c/w Externally applied clamping force F 5500 24.5 lbs. kN A Ø B Ø D B Ø A Φ = 2.96 in (75.2 mm) B Φ=1.90 in (48.3 mm) D=1.07 in (27.2 mm) REPETITIVE PEAK REVERSE AND OFF-STATE BLOCKING VOLTAGE TJ= 0 to 125oC MODEL VD R M VR R M (volts) (volts) SDT122FT 4000 4000 SDT122FS 3900 3900 SDT122FR 3800 3800 SDT122FP 3700 3700 SDT122FM 3600 3600 SDT122FK 3500 3500 95f: 5/27/96 SDT122 FULL CYCLE AVERAGE POWER LOSS versus PEAK CURRENT at 50/60 Hz MAXIMUM PEAK RECOVERY CURRENT (plasma spreading and conduction loss) Pavg (watts) 110 100 2600 Irm, (A) 2400 2200 approximation 120 deg.sq. wave overlap angle = 20 degree 2000 1800 Irm Qrr = ---di/dt I T(av) = IT / 3 50 (uC) 1600 2 (A/us) 1400 180 degree 1200 sinewave Tj ( C) 1000 800 I T(av) = I T / 3.1416 125 20 600 25 400 200 0 0 500 1000 1500 2000 2500 10 3000 Peak Current,It (A) .1 1. 5. Circuit diR/dt, (A/us) 95f: 95F: Full Cycle Pow er Loss (w atts) 50/60 Hz, TJ =125oC IT (peak) Half-sine 3 Phase (A) 180o 120o 200 63 69 400 147 162 600 244 270 800 351 390 1000 468 523 1200 596 669 1400 734 828 1600 883 1001 1800 1043 1187 2000 1213 1387 2200 1394 1601 2400 1556 1829 2600 1789 2071 2800 2004 2327 3000 2229 2598 GATE SUPPLY REQUIREMENTS Open circuit voltage 30 V Short circuit current - rise time 3 A 0.5us Pulse duration (min) 20 us sh2 7/11/95