Multi-level logic

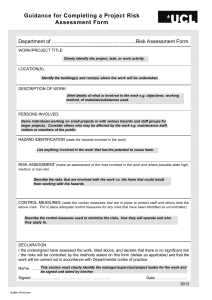

advertisement

Overview Timing diagrams Last lecture Verilog “Sideways” truth tables Show time-response of circuits Real gates have real delays Today Timing diagrams Multilevel logic Example: A' • A = 0 Delays cause transient F=1 Multilevel NAND/NOR conversion AOI and OAI gates A B C D F time Hazards Some texts call timing diagrams “waveforms” CSE370, Lecture 9 1 Example: F=A+BC in 2-level logic F1 2 Timing diagram for F = A + BC C B CSE370, Lecture 9 canonical sum-of-products Time waveforms for F1 – F4 are identical Except for timing hazards (glitches) More on this shortly... A F2 F3 F4 CSE370, Lecture 9 minimized sum-of-products canonical product-of-sums minimized product-of-sums 3 CSE370, Lecture 9 4 Multilevel logic Multilevel logic example Basic idea: Simplify logic using >2 gate levels Time–space (speed versus gate count) tradeoff Function X SOP: X = ADF + AEF + BDF + BEF + CDF + CEF + G X is minimized! Six 3-input ANDs; one 7-input OR; 25 wires Two-level logic usually Has smaller delays (faster circuits) But more gates and more wires (more circuit area) Sometimes has large fan-ins (slow) Factored form One 3-input OR, two 2-input OR's, one 3-input AND; 10 wires Easier to eliminate hazards Multilevel logic usually Has less gates (smaller circuits) 3-level circuit X = (A+B+C)(D+E)F + G A B C But can be slower (more gate delays) Multilevel: X = (A+B+C)(D+E)F + G Harder to eliminate hazards X D E F G CSE370, Lecture 9 5 Multilevel NAND/NAND conversion F = A(B+CD) + BC' Level 1 introduce bubbles (conserve inversions) CSE370, Lecture 9 6 Multilevel NOR/NOR conversion F = A(B+CD) + BC' original AND-OR network CSE370, Lecture 9 C D B A B C' C D Level 2 Level 3 Level 1 Level 4 original AND-OR network F C D B A B C' Level 2 Level 3 Level 4 F C F introduce bubbles (conserve inversions) B A B C' D B A F B C' 7 CSE370, Lecture 9 8 Generic multilevel conversion AND-OR-Invert and OR-AND-Invert blocks F = ABC + BC + D = AX + X + D AOI and OAI are dense 3-level building blocks 2x2 AOI uses only 8 transistors Minimal delay (a) (b) A B C X D A B C F F X D add double bubbles at inputs original circuit (c) (d) A A X B C F X' B C D' distribute bubbles some mismatches F X' D' logical concept 9 Using AOI and OAI blocks F AND OR 10 Example: AOI and OAI A C Form AOI as (F’)’ AOI form – Use SOP F' = A'B' + A'C + B'C F = (A'B' + A'C + B'C)' A CSE370, Lecture 9 1 0 0 1 1 1 0 0 1 0 B Example: F = A'B + AB' SOP form: F' = A'B' + AB AOI form: F = (A'B' + AB)' B + & CSE370, Lecture 9 If using AOI, find F’ in minimized SOP form If using OAI, find F’ in minimized POS form 1 & 3x2 AOI symbol Invert Approach Start by finding F’ 0 + & insert inverters to fix mismatches CSE370, Lecture 9 & 2x2 AOI symbol A B C D A' & B' A & B + A' B' A' C B' C F 11 & & + & CSE370, Lecture 9 F OAI form – Use POS F' = (B'+C)(A'+C)(A'+B') F = [(B'+C)(A'+C)(A'+B')]' B' C A' C A' B' + + & F + 12 Issues with multilevel design Multilevel logic summary No global definition of “optimal” multilevel circuit Optimality depends on user-defined goals Synthesize an implementation that meets design goals Advantages over 2-level logic Smaller circuits Reduced fan-in Less wires Synthesis requires CAD-tool help No simple hand methods like K-maps CAD tools manipulate Boolean expressions Disadvantages w.r.t 2-level logic More difficult design Less powerful optimizing tools Dynamic hazards Factoring, decomposition, etc. Covered in more detail in CSE467 What you should know for CSE370 The basic multilevel idea Multilevel NAND/NAND and NOR/NOR conversion AOI gates CSE370, Lecture 9 13 CSE370, Lecture 9 Hazards/glitches Types of hazards Hazards/glitches: Undesired output switching Occurs when different pathways have different delays Wastes power; causes circuit noise Dangerous if logic makes a decision while output is unstable Dangerous if using asynchronous circuits Static 1-hazard Output should stay logic 1 Gate delays cause brief glitch to logic 0 14 1 Static 0-hazard Output should stay logic 0 Gate delays cause brief glitch to logic 1 Solutions Design hazard-free circuits 0 1 0 1 0 Difficult when logic is multilevel Wait until signals are stable Use synchronous circuits CSE370, Lecture 9 Dynamic hazards Output should toggle cleanly Gate delays cause multiple transitions 15 CSE370, Lecture 9 0 1 0 1 1 0 1 16 0 Static hazards Dynamic hazards Occur when a literal and its complement momentarily Occur when a literal assumes multiple values Through different paths with different delays Causes an output to toggle multiple times assume the same value Through different paths with different delays Causes an (ideally) static output to glitch A A multiplexer A A S F 3 B B S A F C 2 B1 1 B2 C B3 S' B F F S' CSE370, Lecture 9 Dynamic hazard Dynamic hazards static-0 hazard 17 CSE370, Lecture 9 18 Eliminating static hazards Eliminating static hazards (con’t) In 2-level logic circuits Assuming single-bit changes Solution: Add redundant k-map encirclements Ensure that all single-bit changes are covered First eliminate static-1 hazards: Use SOP form Key idea: Glitches happen when a changing input spans separate k-map encirclements A C' A' D CSE370, Lecture 9 A C' A AB CD 00 01 11 10 00 0 0 1 1 F = AC' + A'D 01 1 F C 1 1 1 11 1 1 0 0 10 0 0 0 0 B A AB CD 00 01 11 10 00 0 0 1 1 F = AC' + A'D + C'D Example: 1101 to 0101 change can cause a static-1 glitch A' D C' D D 19 F C 01 1 1 1 1 11 1 1 0 0 10 0 0 0 0 D B Still need to eliminate static-0 hazards: Use POS form CSE370, Lecture 9 20 Summary of hazards We can eliminate static hazards in 2-level logic For single-bit changes Eliminating static hazards also eliminates dynamic hazards Hazard are a difficult problem Multiple-bit changes in 2-level logic are hard Static hazards in multilevel logic are harder Dynamic hazards in multilevel logic are harder yet CAD tools and simulation/testing are indispensable Test vectors probe a design for hazards CSE370, Lecture 9 21