Pad tutorial

advertisement

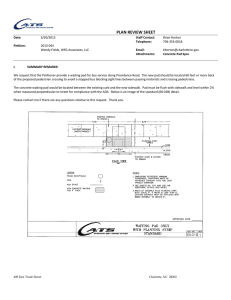

ECE/CS 5720/6720: Design Project Pads Information The final step of your design project (if you have chosen to fabricate your circuit) will be to add pads to your layout. Your layout should fit within a square of approximately 990µm x 990µm. The tiny chip units (TCU) each project will be allotted are 1500µm x 1500µm, but the pad circuitry takes up space at the edges of the chip. The layout of your circuit should actually be smaller than 990µm x 990µm, since you will require some space around the periphery for routing signals to the pads. One other rule to follow when making the schematic and layout for your circuit is to name your supply nets as vdd! and gnd!. The exclamation mark denotes a global net, meaning that it can be seen anywhere in the hierarchy of your schematics, without explicitly connecting it. This is the convention that has been used in the layouts and schematics for the pads, so following this convention will allow you to perform DRC and LVS checks on your entire chip after you have added the pads. Once you have completed the DRC and LVS checks for your layout, perform the following steps to add the pads: 1. Add the following line to your cds.lib file: DEFINE UofU_Pads /uusoc/facility/cad_common/local/Cadence/lib/UofU_Pads 2. Now start cadence, you should be able to see this new library in your library manager. 3. Next use the library manager to copy the cell Frame1_38 from the UofU_Pads library to your own working library, renaming the cell to top. 4. Now open up this cell. The layout is a pad ring containing one of each type of pad. There are 40 pads in the ring, 10 on each side. The corners of the pad ring just connect the power and ground rings that run through the pads. The different pad cells will appear as red boxes, if you want to see the actual layout you can select: Options -> Display and set Display Levels from 0 to 30, instead of from 0 to 0 which is the default. A description of each of the pads is as follows: a. pad_bidirhe: this pad is used for digital inputs and outputs. The input or output functionality is determined by how the output enable (EN) is set. A description of each of the pad connections is as follows: i. EN: located on the bottom left of the pad (Metal 2). Connect this to vdd! to have the pad behave as an output (driving information out of the chip), or to gnd! to have the pad behave as an input (driving information in to the chip) ii. DataOut: located on the lower left of the pad (Metal 2). Connect this to data that is being driven out of the chip. iii. DataIn: located on the lower right of the pad (Metal 2). Connect this to data lines receiving data from outside of the chip. iv. DataInB: located on the lower right of the pad (Metal 2). This is the same as above, but inverted. b. pad_corner: these are the corners of the pad ring, they are not actually pads since they don’t have connections outside the chip, they just connect the power and ground rings that encircle the chip. c. pad_gnd: these are used for providing the negative power rail (e.g., Vss) to the chip, a pad ring must include at least one of these. The Metal 1 on the bottom middle of the pad and the Metal 2 along the entire bottom of the pad is the gnd! connection. d. pad_in: this is the same as pad_bidirhe, except the EN connection has been tied to gnd! so the pad can only function as a digital input. Use this pad if the pad is going to be used exclusively to drive digital data onto the chip. The connections of interest are: i. DataIn: located on the lower right of the pad (Metal 2). Connect this to data lines receiving data from outside of the chip. ii. DataInB: located on the lower right of the pad (Metal 2). This is the same as above, but inverted. e. pad_io: this pad is a straight connection to the outside pin, with a small series resistance (about 300 ohms). Use it for analog inputs that will not draw DC current, such as a connection to the gate of a transistor. The connection of interest is: i. io: located on the lower middle of the pad (Metal 2), connect this to the input or output. f. pad_io_nores: this pad is the same as pad_io, but with no resistor. Use it for analog inputs or outputs that will draw DC current. May also be used for auxiliary power supplies. The connection of interest is: i. pad: located on the lower middle of the pad (Metal 2), connect this to the input or output. g. pad_nc: this is “no-connect” pad, use it as a spacer if you have fewer than 40 pins. The other option would be to add extra power and ground pins. h. pad_out: this is the same as pad_bidirhe, except the EN connection has been tied to vdd! so the pad can only function as a digital output. Use this pad if the pad is going to be used exclusively to drive digital data out of the chip. The connections of interest are: i. DataOut: located on the lower left of the pad (Metal 2). Connect this to data that is being driven out of the chip. i. pad_vdd: these are used for providing the positive power rail to the chip, a pad ring must include at least one of these. The Metal 1 on the lower middle of the pad is the vdd! connection. 5. Next you will need to remove and add pads from the ring to get the types of pads that you need for your design. I would recommend doing this one pad at a time with the Display Levels set from 0 to 30 so that you get the pads aligned properly. 6. Next you should instantiate the layout cell for your circuit in the center of the pad ring layout, and route all of the required signals from your circuit to the pads. 7. The next step is to create a schematic view of the entire chip. To do this, open the schematic view of the top cell. You will have to remove and add pad cells to get the ones you need, just as you did for the layout. Now create a symbol view for your circuit (if you haven’t already) and instantiate this in the top schematic. Next connect the appropriate signals to the pads. Notice that the individual pad symbols have no pins for the power rails, this is because they have been named as global nets and will be connected automatically (you must still connect them in the layout!). 8. The final step is to run DRC on the final chip layout, and then extract and run LVS against the schematic which you have created.