Input/Output Termination Techniques

advertisement

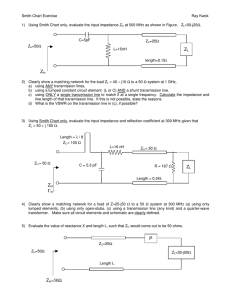

Input/Output Termination Techniques Introduction This document provides the Atmel ADCs and DMUX users with the different termination techniques to be used with Atmel products. A wide panel of configurations for the analog and clock inputs as well as for the data outputs are described in detail. Input/Output Termination Techniques The principles of each technique are also presented so that one can eventually choose the proper implementation at the input and output of our products, considering one’s application. Application Note Finally, this document is not exhaustive. Nevertheless, it covers a wide area in terms of IO termination techniques. TS83 ADC Family TS81 DMUX Family Rev. 2169A–BDC–07/02 1 Analog Input Termination Techniques There are many different termination techniques, which can be used to reduce the impact of the transmission line effects. An overview of the Standard Input termination methods, which can be used for Atmel ADCs analog inputs, is provided in the following sections. Single-ended Configuration The following figure illustrates two input configurations, when the single-ended mode is chosen for the analog input. Here, the common mode of the driving system is assumed to be the same as the one for the analog input of the ADC (Ground). Since Atmel ADCs are both single-ended and differential-compatible, both cases will be treated in the next sections. Figure 1. Configuration without Additional Termination Resistor 50Ω Driving Source ADC Package 50Ω 50Ω impedance line IN 50Ω 50Ω 50Ω 50Ω impedance line INB ADC Input Buffer Figure 2. Configuration with 50Ω Termination Resistor 50Ω Driving Source ADC Package 50Ω 50Ω impedance line IN 50Ω 50Ω 50Ω impedance line 50Ω INB ADC Input Buffer The first configuration may well be used in the case of an ADC device featuring an internal 50Ω termination (inside the cavity for the TS83102G0 10-bit 2 Gsps ADC and on package for the TS8388BG 8-bit 1 Gsps ADC). 2 Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques The second configuration should be used when the differential analog input of the device is not already 50Ω terminated. If the system, which is driving the analog input, needs to be terminated externally, the termination techniques are the following. Figure 3. Configuration without Additional Termination Resistor Unterminated Driving Source ADC Package 50Ω impedance line IN 50Ω 50Ω 50Ω 50Ω impedance line 50Ω INB ADC Input Buffer Figure 4. Configuration with 50Ω Termination Resistor Unterminated Driving Source ADC Package 50Ω impedance line 50Ω 50Ω 50Ω impedance line 50Ω IN 50Ω INB ADC Input Buffer 3 2169A–BDC–07/02 In all the previous configurations, it was assumed that there was no need to adjust the common mode (CM). If the common mode from the driving device is not the same as the one specified for the analog input of the ADC (GROUND), the user may have to choose between the configurations illustrated below. Figure 5. Configuration without Additional Termination Resistor and with Coupling Capacitor 50Ω Driving Source ADC Package 50Ω 50Ω impedance line 10 nF IN 50Ω 50Ω 50Ω 50Ω impedance line 10 nF Note: INB ADC Input Buffer The values of the coupling capacitors are given for information only. They may change depending on the input frequency. Figure 6. Configuration with 50Ω Termination Resistor and with Coupling Capacitor 50Ω Driving Source ADC Package 50Ω 50Ω impedance line 10 nF IN 50Ω 50Ω 50Ω impedance line 50Ω INB 10 nF ADC Input Buffer If the driving system has to be terminated, a 50Ω resistor has to be connected between the output of the system and the ground, as already described in the previous sections. Note: 4 The values of the coupling capacitors are given for information only. They may change depending on the input frequency. Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques Differential Configuration When the analog input is to be used in differential mode and assuming that the common mode of the driving system is the same as the one for the input of ADC (Ground), the possible configurations are the following: Figure 7. Configuration without Additional Termination Resistor ADC Package 50Ω Driving Source 50Ω impedance line IN 50Ω 50Ω 50Ω 50Ω 50Ω impedance line INB ADC Input Buffer Figure 8. Configuration with Differential 50Ω Termination Resistors and with Grounded Middle Point ADC Package 50Ω Driving Source 50Ω impedance line IN 50Ω 50Ω 50Ω 50Ω impedance line 50Ω INB ADC Input Buffer Figure 9. Configuration with Differential 50Ω Termination Resistors and with Decoupled Middle Point ADC Package 50Ω Driving Source 50Ω impedance line 50Ω 50Ω 50Ω IN 50Ω impedance line 40 pF 50Ω INB ADC Input Buffer Note: The values of the coupling capacitors are given for information only. They may change depending on the input frequency. 5 2169A–BDC–07/02 Figure 10. Configuration with Differential 100Ω Termination Resistors and with Floating Middle Point ADC Package 50Ω Driving Source 50Ω impedance line IN 50Ω 100Ω 50Ω 50Ω impedance line INB ADC Input Buffer If the common mode of the driving system is not the same as the one of the input of the ADC, the previous configurations become. Figure 11. Configuration without Additional Termination Resistor ADC Package 50Ω Driving Source 50Ω impedance line 10 nF IN 50Ω 50Ω 50Ω 50Ω impedance line 50Ω 10 nF INB ADC Input Buffer Note: The values of the coupling capacitors are given for information only. They may change depending on the input frequency. Figure 12. Configuration with Differential 50Ω Termination Resistors and with Coupling Capacitors ADC Package 50Ω Driving Source 50Ω impedance line 10 nF 50Ω 50Ω 50Ω IN 50Ω impedance line 10 nF 50Ω INB ADC Input Buffer Note: 6 The values of the coupling capacitors are given for information only. They may change depending on the input frequency. Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques Figure 13. Configuration with Differential 100Ω Termination Resistors and with Coupling Capacitors ADC Package 50Ω Driving Source 50Ω impedance line 10 nF IN 50Ω 100Ω 50Ω 50Ω impedance line 10 nF INB ADC Input Buffer Note: The values of the coupling capacitors are given for information only. They may change depending on the input frequency. The same schemes are valid when the driving system is not terminated. In these cases, the user only has to add the external 50Ω resistors on both outputs of the driving system in the schemes. The user may only have a single-ended generator to drive the ADC input differentially (preferred way at high sampling rates). In this case, the user still has the opportunity to use a balun. The different configurations in this mode of operation are described in the next section. 7 2169A–BDC–07/02 Configuration with a Balun The following section only represents the three general cases illustrating the use of a balun to convert the single-ended signal from the generator into a differential signal for the ADC input. The different cases with an unterminated driving system have not been presented. The user can refer to the schemes given previously for these configurations. Figure 14. Configuration without Additional Termination Resistor 50Ω Driving Source ADC Package 50Ω 50Ω impedance line Balun 50Ω impedance line IN 50Ω 50Ω 50Ω impedance line INB ADC Input Buffer Figure 15. Configuration with Differential 50Ω Termination Resistors and with Grounded Middle Point 50Ω Driving Source ADC Package 50Ω 50Ω impedance line Balun 50Ω impedance line IN 50Ω 50Ω impedance line 50Ω INB ADC Input Buffer Figure 16. Configuration with Differential 100Ω Termination Resistors and with Floating Middle Point 50Ω Driving Source ADC Package 50Ω 50Ω impedance line Balun 50Ω impedance line IN 100Ω 50Ω impedance line INB ADC Input Buffer 8 Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques Clock Input Termination Techniques In the case when the clock input of the ADC is not used in ECL levels but is centered around 0V, the configurations presented for the analog inputs (ground common mode voltage), except the AC coupled cases, can be transferred to the input clock. ECL Single-ended Configuration With a clock in ECL level, the main idea to abide by is to connect the negative clock to the common mode voltage of the positive clock input: -1.3V (ECL) through a 50Ω termination resistor (if not already implemented). Figure 17. Configuration without Additional 50Ω Termination Resistor ECL 50Ω Driving Source ADC Package 50Ω 50Ω impedance line CLK 50Ω 50Ω 50Ω impedance line CLKB -1.3V ADC Input Buffer Figure 18. Configuration with 50Ω Termination Resistor ECL 50Ω Driving Source ADC Package 50Ω 50Ω impedance line CLK 50Ω 50Ω impedance line 50Ω CLKB -1.3V ADC Input Buffer 9 2169A–BDC–07/02 ECL Differential Configuration (ADCs Only) When the clock is used in differential mode with ECL levels, two cases can be taken into consideration: • the ADC is 50Ω on-package (or internally) terminated; • the ADC needs an external termination. Each configuration is described in what follows. Figure 19. ADC Configuration with External Termination ECL Differential Open Emitter Output Buffer VCC = 0V ADC Package 50Ω impedance line CLK 50Ω impedance line CLKB 50Ω 50Ω ECL Differential ADC Input Buffer without Termination VTT = VCC - 2V = -2V 10 Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques Figure 20. ADC Configuration with 50Ω On-package (or internal) Termination ECL Differential Open Emitter Output Buffer VCC = 0V ADC Package 50Ω impedance line CLK 50Ω 50Ω impedance line 274Ω 40 pF 50Ω CLKB ECL Differential ADC Input Buffer 274Ω -5V Note: ECL Differential Configuration (DMUX Only) Since the ADC is already terminated, the standard termination scheme for the ECL driver (VTT = VCC - 2V with Rt = 50Ω) does not apply here. The Figure 20 is an equivalent termination scheme. Figure 21. DMUX Configuration with ECL Differential ECL Differential Open Emitter Output Buffer VCC = 0V DMUX Package 50Ω impedance line CLK 50Ω 50Ω impedance line 274Ω 274Ω 50Ω 10 pF CLKB ECL Differential DMUX Input Buffer -5V Note: Since the ADC is already terminated, the standard termination scheme for the ECL driver (VTT = VCC - 2V with Rt = 50Ω) does not apply here. The Figure 21 is an equivalent termination scheme. 11 2169A–BDC–07/02 Digital Input Termination Techniques for the DMUX The termination technique recommended for the DMUX Data inputs is similar to the one used for the DMUX input clock, since all the DMUX input buffers have been designed according to the same architecture. Figure 22. Digital Input Configuration ECL Differential Open Emitter Output Buffer VCC = 0V DMUX Package 50Ω impedance line DATA IN 50Ω 50Ω impedance line 274Ω 274Ω 50Ω 10 pF DATA INB ECL Differential DMUX Input Buffer -5V Note: 12 Since the ADC is already terminated, the standard termination scheme for the ECL driver (VTT = VCC - 2V with Rt = 50Ω) does not apply here. The Figure 22 is an equivalent termination scheme. Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques Data Output Termination Techniques Open Loaded Termination (ADCs) Figure 23. TS8388Bx and TS8308500 Open Loaded Output Termination VPLUSD Out 75Ω 75Ω 75Ω impedance line 75Ω impedance line + - OutB 11 mA DVEE ADC Output Buffer Figure 24. TS83102G0 Open Loaded Output Termination VPLUSD Out 50Ω 50Ω 50Ω impedance line 50Ω impedance line + - OutB 10.5 mA DVEE ADC Output Buffer In the previous configurations, the output level is determined by VPLUSD: ECL/LVDS modes are available (refer to the product data sheets for more information). 13 2169A–BDC–07/02 75Ω Termination For TS8388Bx and TS8308500 Only Figure 25. TS8388Bx and TS8308500 75Ω Termination VPLUSD Out 75Ω 75Ω 75Ω 75Ω impedance line 75Ω impedance line 10 nF + - 75Ω OutB 11 mA DVEE ADC Output Buffer 50Ω Termination For the TS8388BX and TS8308500 ADCs Figure 26. TS8388Bx and TS8308500 50Ω Termination VPLUSD Out 75Ω 75Ω 50Ω 50Ω impedance line 50Ω impedance line + - 10 nF 50Ω OutB 11 mA DVEE ADC Output Buffer 14 Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques For the TS83102G0 ADC Figure 27. TS83102G0 50Ω Termination VPLUSD Out 50Ω 50Ω 50Ω 50Ω impedance line 50Ω impedance line 10 nF + - 50Ω OutB 10.5 mA DVEE ADC Output Buffer (VTT + R) Termination (DMUX Only) In the specific case of the Atmel DMUX, the output buffers need to be terminated with a “VTT + R” termination (see the different schematics) because the DMUX output buffers are in openemitter configuration. There are three types of output signals for the DMUX: Data Ready, Digital Output Data and Reference Voltage. All of them have the same behavior against VPLUSD and Swing Adjust, and their associated buffers are similar. Figure 28. DMUX Differential Data Ready Output Buffer DMUX differential Data Ready Buffer Outside DMUX V+D 600 I 600 In Ir Out Inb Outb Vrefsa R I Ir R VTT 480 VEE (-5V) 15 2169A–BDC–07/02 Figure 29. DMUX Digital Output Data Buffer DMUX Data Buffer Outside DMUX V+D 600 I Ir 600 In Inb Out Vrefsa R Ir I VTT 480 VEE (-5V) Figure 30. DMUX Reference Buffer DMUX Reference Buffer Outside DMUX V+D 6k 600 Ir Out Vrefsa Ir 6k I R VTT 960 VEE (-5V) The only care to be taken to terminate these output buffers properly is to make sure that the output current Ir never exceeds 36 mA. The relationship between VTT, R, Ir and Vout (output voltage level) is given here: Vout – Vtt Ir = -------------------------R 16 Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques Block Diagram TS81102G0 DMUX Figure 31. TS81102G0 DMUX Block Diagram RatioSel FS/8 ADCDelAdjIn ADCDelAdjCtrl RatioSel SyncReset AsyncReset ClkIn NbBit ClkInType DEMUXDelAdjCtrl Clock Path I[0..7/9] BIST SwiAdj VplusDOut VCC GND VEE DIODE Data Path delay delay NAP B2 mux BIST 8/10 mux Phase control 8/10 RstGen Reset ClkPar even master latch odd master latch odd slave latch even slave latch Counter (8 stage shift register) 8 Counter Status Latch Sel Even/Odd [1..8/10] 8 FS/8 Port Selection Clock 8 8 8/10 Data Output Clock 1 Even Ports Odd Ports DataReady generation DR/DR ADCDelAdjOut A[0..7/9] RefA C[0..7/9] RefC E[0..7/9] RefE G[0..7/9] RefG B[0..7/9] RefB D[0..7/9] RefD F[0..7/9] RefF H[0..7/9] RefH 3 17 2169A–BDC–07/02 TS8388B ADC Figure 32. TS8388B ADC Block Diagram GAIN MASTER/SLAVE TRACK AND HOLD AMPLIFIER VIN, VINB ANALOG ENCODING BLOCK RESISTOR CHAIN 4 INTERPOLATION STAGES 5 4 REGENERATION LATCHES 5 4 CLK, CLKB ERROR CORRECTION AND DECODE LOGIC CLOCK BUFFER 8 OUTPUT LATCHES AND BUFFERS 8 GORB DRRB DR, DRB DATA, DATAB OR, ORB TS83102G0 ADC Figure 33. TS83102G0 ADC Block Diagram PGEB Sample and Hold VINB 50 50 Analog Quantizer VIN B/BG OR ORB D9 D9B Logic block D0 DR0B DR DRB GA CLK CLKB 18 50 50 Clock generation SDA DRRB Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques Internal Timing Diagram DMUX Timing Diagram This diagram corresponds to an established operation of the DMUX with Synchronous Reset. Figure 34. DMUX Timing Diagram 500 ps min Data In N N+1 N+2 N+3 N+4 N+5 N+6 N+7 N+8 N+9 N+10 N+11 N+12 N+13 N+14 N+15 N+16 N+17 N+18 N+19 N+20 N+21 N+22 N+23 N+24 N+25 N+26 N+27 N+28 N+29 N+30 N+31 DR In = Fs DR/2 In = Fs/2 = ClkPar Master Even Latch Master Odd Latch Slave Even Latch Slave Odd Latch N N+2 N+1 N+4 N+3 N N+5 N+2 N+1 N+6 N+7 N+4 N+3 N+8 N+9 N+6 N+5 N+10 N+11 N+8 N+7 N+12 N+13 N+10 N+9 N+14 N+15 N+12 N+11 N+16 N+17 N+14 N+13 N+18 N+19 N+16 N+15 N+20 N+21 N+18 N+17 N+22 N+23 N+20 N+19 N+24 N+25 N+22 N+21 N+26 N+27 N+24 N+23 N+28 N+31 N+29 N+26 N+25 N+30 N+30 N+28 N+27 N+29 Synchronous reset = Fs/8 Internal reset pulse Port Select A Port Select B Port Select C Port Select D Port Select E Port Select F Port Select G Port Select H Latch Select A Latch Select B Latch Select C Latch Select D Latch Select E Latch Select F Latch Select G Latch Select H N N+8 N+1 N+16 N+9 N+2 N+17 N+10 N+3 N+27 N+20 N+13 N+6 N+26 N+19 N+12 N+5 N+25 N+18 N+11 N+4 N+24 N+21 N+14 N+22 N+7 N+15 N+23 N to N+7 N+8 to N+15 N+16 to N+23 A to H Port Out A to H LatchOut DROut 19 2169A–BDC–07/02 ADCs Timing Diagrams The timing diagrams for the TS8388B and TS83102G0 ADCs are similar. Care should only be taken regarding the values of the specified timings (Refer to the corresponding device data sheets for more details). Figure 35. Data Ready Reset, Clock Held at LOW Level TA = 250 ps X (VIN, VINB) X X N+1 N N-1 X N+2 X N+3 X N+4 X N+5 TC = 1000 ps TC1 TC2 (CLK, CLKB) DIGITAL OUTPUTS TOD = 1360 ps TPD: 4.0 Clock periods 1360 ps DATA N-5 1000 ps DATA N-4 DATA N-3 DATA N-2 DATA N-1 DATA N+1 TD1 = TC1+TDR-TOD = TC1-40 ps = 460 ps TDR = 1320 ps TDR = 1320 ps DATA N Data Ready (DR, DRB) TD2 = TC2+TOD-TDR = TC2+40 ps = 540 ps TRDR = 720 ps DRRB 1ns (min) Figure 36. Data Ready Reset, Clock Held at HIGH Level TA = 250 ps X (VIN, VINB) N XN-1 N+1 N+2 X X X X X N+3 N+4 N+5 TC = 1000 ps TC1 TC2 (CLK, CLKB) DIGITAL OUTPUTS TOD = 1360 ps TPD: 4.0 Clock periods 1360 ps DATA N-5 1000 ps DATA N-4 DATA N-3 TDR = 1320 ps TDR = 1320 ps DATA N-2 DATA N-1 DATA N DATA N+1 TD1 = TC1+TDR-TOD = TC1-40 ps = 460 ps Data Ready (DR, DRB) TRDR = 720 ps TD2 = TC2+TOD-TDR = TC2+40 ps = 540 ps DRRB 1ns (min) 20 Input/Output Termination Techniques 2169A–BDC–07/02 Input/Output Termination Techniques ADC and DMUX Testbench Figure 37. Example of ADC and DMUX Testbench TSEV8388BG or TSEV83102G0 EVALUATION BOARD INPUT SIGNAL GENERATOR ADC TSEV81102G0 EVALUATION BOARD DMUX FILTER SYNCHRONIZATION ACQUISITION SYSTEM CLOCK SIGNAL GENERATOR DIGITAL ACQUISITION LabView - HISTOGRAM - FFT - RECONSTRUCTED SIGNAL - ENOB, SFDR, INL, DNL, ... SCIENTIFIC COMPUTER 21 2169A–BDC–07/02 Atmel Headquarters Atmel Operations Corporate Headquarters Memory 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 487-2600 Europe Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland TEL (41) 26-426-5555 FAX (41) 26-426-5500 Asia Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimhatsui East Kowloon Hong Kong TEL (852) 2721-9778 FAX (852) 2722-1369 Japan 9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan TEL (81) 3-3523-3551 FAX (81) 3-3523-7581 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314 RF/Automotive Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany TEL (49) 71-31-67-0 FAX (49) 71-31-67-2340 Microcontrollers 2325 Orchard Parkway San Jose, CA 95131 TEL 1(408) 441-0311 FAX 1(408) 436-4314 La Chantrerie BP 70602 44306 Nantes Cedex 3, France TEL (33) 2-40-18-18-18 FAX (33) 2-40-18-19-60 ASIC/ASSP/Smart Cards 1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759 Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom Avenue de Rochepleine BP 123 38521 Saint-Egreve Cedex, France TEL (33) 4-76-58-30-00 FAX (33) 4-76-58-34-80 Zone Industrielle 13106 Rousset Cedex, France TEL (33) 4-42-53-60-00 FAX (33) 4-42-53-60-01 1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906 TEL 1(719) 576-3300 FAX 1(719) 540-1759 Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland TEL (44) 1355-803-000 FAX (44) 1355-242-743 e-mail literature@atmel.com Web Site http://www.atmel.com © Atmel Corporation 2002. Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company’s standard warranty which is detailed in Atmel’s Terms and Conditions located on the Company’s web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel’s products are not authorized for use as critical components in life support devices or systems. ATMEL ® is the registered trademark of Atmel. Other terms and product names may be the trademark of others. Printed on recycled paper. 2169A–BDC–07/02 0M