View - Microsemi

advertisement

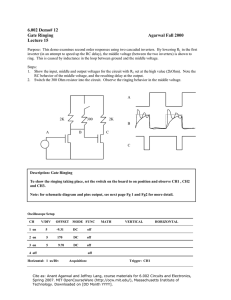

Am79R70/79/100/101Ringing SLIC Device Technical Overview Application Note The Am79R70/79 Ringing Subscriber Line Interface Circuit (SLIC) device is designed to internally generate the ringing voltage used in short loop applications such as Fiber-in-the-Loop, Radio-in-theLoop, hybrid fiber/coax, and video telephony, as well as the BORSHT functions of other Zarlink SLIC devices. In meeting the ringing requirements of TR909, the power supply for ringing is reduced to 70 V. The Am79R100 and the Am79R101 are the second generation devices of the Zarlink ringing SLIC family with operating batteries capable of running applications of up to 100 V. In addition to the functions of the Am79R70/79, the new chips have higher ringing and longer loop driving abilities. Additionally, adjustment of the Am79R101 DC offset enables sinusoidal through-chip ringing. It is the new features of the Am79R100/101 devices that give the Zalrink ringing SLIC family the ability to satisfy the requirements of emerging Voice over Broadband and other short/medium loop applications. RINGING SLIC DEVICE FEATURES The Am79R70/79 Ringing SLIC device has the necessary circuitry to generate the ringing voltage needed for short loop applications, and includes on-chip ring-trip detection. As with other Zalrink SLIC devices, the Am79R79 Ringing SLIC device has programmable features, such as current feed, two-wire impedance, overhead, and loop detect threshold. This device operates with two battery voltages. Typically, the most negative battery supply (VBAT1) is used for ringing and other onhook states, and the other less negative battery supply (VBAT2) is used for off-hook states. To prevent excessive voltage from appearing on the telephone line, the Am79R79 Ringing SLIC device provides anti-saturation guards that are adjustable for each battery supply. Digital interfaces on the Am79R79 Ringing SLIC device allow eight different states of operation. Except for the Ringing state, the characteristics of the other seven operating states are the same as the other Zarlink SLIC devices. Am79R70 is the looser specification of Am79R79, with lower cost and lower operating battery. In comparison, the Am79R100 is similar in function to the Am79R70/79. It provides trapezoid ringing through the chip but has a higher battery supply (up to 100 V) than the Am79R70/79. On the other hand, the Am79R101 has the same voltage rating as the Am79R100, but offers sinusoidal waveform through chip ringing with balance or DC offset adjustment. The Am79101 features are particularly popular in the European market. ON-CHIP RINGING resistance and on ringing load. The North American ringing load requirement is 5REN (ringer equivalent number), which is approximately 1400 Ω and is among the world’s most stringent requirements. Because many international specifications only require 3REN drivers, any ringing load that meets the North American requirement is almost certainly sufficient for any other application. Traditionally, the central office (CO) must be able to drive 5REN through 1500 Ω lines to 40 VRMS. One constraint of this demand is that a line of such length would require a ringing voltage of about 90 VRMS at the linecard. Additionally, multiparty ringing, requires that – 48 V and the superimposed AC ringing signal be applied to the tip or to the ring for ringing or ring-trip detection. The Am79R79 Ringing SLIC device overcomes these hurdles by taking advantage of the less stringent requirements for short loop applications and by using a new ringing technique to reduce the ringing supply requirements to 70 V. Table 1 shows the maximum loop resistance and ringing voltage crest factor for LSSGR, DLC, and FITL. The LSSGR maximum loop length of 1500 Ω requires a ringing voltage in excess of 90 VRMS at the linecard to supply the required 40 VRMS at the handset. With a 70 Ω maximum loop resistance for FITL, a lower ringing voltage is sufficient due to the considerably lower voltage drop in the line. Assuming a 150 Ω total series resistance in the linecard, 70 Ω in the line, and 1400 Ω of ringing load, approximately only 46 VRMS is needed at the SLIC A and B leads to attain 40 VRMS at the telephone. A ringing generator must provide an adequate signal at the linecard such that sufficient voltage across the telephone handset causes it to ring. This signal is typically 40 V root-mean-square (rms), and is dependent on loop Publication# 080158 Rev: C Amendment: /0 Issue Date: December 2000 0 Battery a. Sinusoidal Unbalanced Ringing 0 Tip Ring Battery b. Trapezoidal Balanced Ringing Figure 1. Unbalanced and Balanced Ringing Table 1. Crest Factor Requirements for Various Bellcore Specs Loop Resistance (Max) Ring Voltage Crest Factor (Spec) CO (LSSGR) 1500 Ω 1.35–1.45 DLC (TR57) 900 Ω 1.2–1.6 1 1.2–1.6 FITL (TR909) 17 Ω Note: 1. Specified as 500 feet of 22 American Wire Gauge (AWG) at 65°C. The crest factor (CF) of a waveform is the ratio of the peak (pk) value to its root-mean-square value. Thus, for the same rms value, a waveform with a higher crest factor will require a higher peak value. A sine wave has a crest factor of 1.414, while a square wave has a crest 2 factor of 1.0. A 1.0 VPK square wave will have the same rms value as a 1.414 VPK sine wave. The TR909 specification requires a ringing voltage of 40 VRMS at the handset with a crest factor between 1.2 and 1.6. To minimize the peak voltage required, and thus get the most out of the available supplies, the Am79R79/100 Ringing SLIC devices generate a trapezoidal waveform whose crest factor can be adjusted between 1.1 and 1.6. Note that a crest factor of 1.25 typically provides a voltage within requirements and allows for some margin. For a 40 VRMS ringing signal at the handset, a trapezoidal waveform with a crest factor of 1.25 only demands a 50 VPK ringing signal. On the other hand, if the waveform were sinusoidal, it would require over 56 VPK. But the sinusoidal signal does have an advantage, in that its harmonic content is limited. This is important when wires run in a common bundle for a long distance, where capacitance between pairs can cause them to couple Am79R70/79/100/101 Ringing SLIC Device Technical Overview into each other. However, for short loop applications (such as those discussed here), where wire pairs run alongside each other over short distances, the larger harmonic content of the trapezoidal waveform is insignificant, as short loop applications have inherently lower crosstalk.Traditional phone ringing is unbalanced, meaning that the ringing voltage is applied directly to the ring lead, as shown in Figure 1a. A typical ringing requirements demand an AC signal greater than 86 VRMS superimposed on –48 V. This allows for the use of a single-ended ringing generator which permits multiparty ringing. Because multiparty ringing is not a requirement of short loop applications, use of a singleended ringing generator is unnecessary, in other words, voltage need not be applied to only the tip or to only the ring. In this way, short loop ringing voltages have greater flexibility. With unbalanced ringing, it is impossible to achieve 45 VRMS at the linecard using a 75 V battery. Even a 70 V peak-to-peak (pk-pk) square wave would only result in 35 VRMS, and it’s 1.0 crest factor is 0.2 below the minimum. With balanced ringing however, a metallic (differential) signal appears across the SLIC A and B leads, as shown in Figure 1b. This differential signal can generate a ringing voltage with a peak value equal to the battery voltage minus a 5 V amplifier overhead. Therefore, a typical 70 V battery has a peak ringing voltage of 65 V. When the crest factor is 1.25, the ringing voltage at the A and B leads is 52 VRMS. The Am79R79/100 RSLIC generates a balanced ringing signal. During the Ringing state, VA (TIP) and VB (RING) alternate in polarity at a frequency determined by the RINGIN signal. In this way, a peak-to-peak voltage of nearly twice the VBAT1 voltage is obtained as shown in Figure 2. Notice that the signal level relative to ground is always lower in magnitude than VBAT1. Also note that the ringing waveform is trapezoidal. Its slope is controlled by the RSLEW and CSLEW components (see Figure 3). VAB 0V VA VB VBAT1 Figure 2. Balanced Ringing DC OFFSET DURING RINGING Traditionally, a DC offset between the tip and the ring leads was necessary for ring-trip detection. The need for a DC offset stemmed from the overlap between the AC impedance on-hook and off-hook states. For example, consider an LSSGR line with a 10 kΩ minimum line leakage. It’s on-hook and off-hook, AC and DC impedances are given in Table 2. Note that in the central office, the DC impedance has an off-hook maximum of 1.93 kΩ and an on-hook minimum of 10 kΩ, whereas the AC impedance has an off-hook maximum of 1.93 kΩ and an on-hook minimum of 1.23 kΩ. The AC on-hook impedance value range overlaps with the off-hook value range, making it impossible to reliably detect ring trip over all possible conditions. Table 2. On-Hook vs. Off-Hook Impedances, LSSGR Central Office AC DC On-hook 1.23 kΩ to infinity 10 kΩ to infinity Off-hook 0 Ω to 1.93 kΩ 0 Ω to 1.93 kΩ However, the DC on-hook to off-hook impedance ratio is over five times greater than the AC on-hook to offhook impedance ratio, indicating that DC detection is relatively easy. Consider the TR909 specification, Table 3 shows the results of operating within TR909 requirements. Table 3. On-Hook vs. Off-Hook Impedances, TR909 FITL/TR909 AC DC On-hook 1.23 kΩ to infinity 10 kΩ to infinity Off-hook 0 Ω to 500 Ω1 0 Ω to 500 Ω Note: 1. This assumes a loop resistance of 70 Ω and not the actual spec of 17 Ω, which gives extra margin to the spec. Under TR909 requirements, while the DC on-hook to off-hook impedance ratio is over 20, the AC ratio is just over 2. By setting the AC threshold to about 900 Ω, a sufficient margin for reliable detection is gained. Because AC detection is achievable in the TR909 case, there is no need for a DC offset to establish ring trip detection. Therefore, the ringing voltage does not require an offset between the tip and the ring leads. Eliminating the need for a DC offset allows the AC ringing voltage to use the entire supply for the AC waveform. Additionally, the sinusoidal ringing waveform generated through the Am79R101 device, has the advantage of low distortion, and satisfies traditional ringing waveform requirements including small PBX, WLL and Pairgain applications. With it’s offset ringing created through the application of a DC offset bias voltage on the RREF or VRING pins, the Am79R101 device also satisfies most phones that require an offset from ground to tip during ringing. Certainly, trapezoidal ringing still provides a good alternative to sinusoidal ringing, as it consumes less power and occupies less space. Am79R70/79/100/101 Ringing SLIC Device Technical Overview 3 Implementation RSLEW 150 kΩ RINGIN Waveshaping RDCR Buffer CSLEW 0.33 µF t1 t2 Ringin Input t1 t2 RDCR Ringing Waveform Figure 3. Ringing Input The ringing feed circuitry generates a trapezoidal ringing voltage from a square wave signal applied to the RINGIN pin. This circuitry, along with the external RC network at RINGIN, controls the crest factor of the ringing signal. RINGIN, the CMOS-compatible reference input, is shown in Figure 3. The input to this pin must be a 50% duty cycle square wave applied to the external resistorcapacitor network (made up of RSLEW and CSLEW), and must be as close as possible to VCC and GND. The VCC used to generate the square wave should be the same level of voltage used for the SLIC VCC to avoid a DC offset between the SLIC internal reference and the input to the ring signal. RSLEW and CSLEW should be chosen to obtain the rate of change needed for a given crest factor through the waveshaping circuitry. The resistor RDCR, which connects to pin RDCR, determines the current to drive to the A and B amplifiers. This current can be selected to achieve a desired peak value for a given application. This is discussed in more detail in the Ringing Circuitry section on page 8 and in Appendix 1. For the Am79R100/101 devices, the maximum voltage on RDCR is ±2.5 V, whereas the maximum voltage on RDCR is ±3 V for the Am79R79 device. Figure 4 shows that there exists a peak available current, IRINGLIM, that will drive into a short circuit. It also shows that in an open circuit, the voltage will increase to V BAT1 – 3 V . V BAT1 – 3 V Slope = R +R D CR1 DC R2 --------------------------------------------------200 50 VAB RINGING FEED Trapezoid Waveform 40 30 20 10 IRINGLIM 0 ILOOPRING Figure 4. Ringing Feed CREST FACTOR To calculate the appropriate values for an arbitrary crest factor, it is necessary to discuss the input circuitry characteristics. The transition region of the input is about 0.52 V. The equation for rate of change of voltage across a capacitor with a constant current through it is • ∆V∆t = C ----------------I For the 0.52 ∆V that the input moves, it is an adequate approximation to assume there is a constant current in C SLEW. A CMOS-compatible input will go nearly all to the supplies, so the current through RSLEW will be about 2.5 V ⁄ R SLE. Substituting the current through R SLEW, the value of ∆V, and C SLEW for "C" in the above equation yields the following expression: 4 Am79R70/79/100/101 Ringing SLIC Device Technical Overview C SLEW ( 0.52 V ) ∆t = -------------------------------------------- = 0.214 • R SLEW • C SLEW ( 2.5 V ) ⁄ ( R SLEW ) This equation represents the time spent in the Linear mode and is the actual transition time of the ringing waveform. For a trapezoidal ringing waveform, one can consider it as the sum of three parts: a square wave with a crest factor of 1, and two triangular sections (representing the leading and trailing transition times), whose crest factors are both 1.73. The total time of the triangular portions is twice the ∆t calculated in the equation above, and the square wave time is the period of the ringing waveform minus the total time for the triangular portions. In order to calculate the ringing crest factor, the rms value of the ringing waveform must be found. Because the peak value appears in both the numerator and denominator, and thus cancels out, the equation can be normalized to an amplitude of one, simplifying the equation. Therefore, the rms value of the overall waveform can be calculated by taking the rms value of the segments that make up the trapezoidal waveform and combining them. For the leading and trailing edge triangular segments, whose time period is equal to ∆t, the expression becomes: 0.214 • R SLEW • C SLEW . And so, these triangular segments have an rms value of 0.577. For a square wave with an rms value of 1, the period is equal to the overall period minus the time of the triangular segments. Therefore, the rms value of the total waveform can be found by adding the contribution of each segment, and dividing by the total period (Per), as shown by the following equation: 2 • 0.214 • R SLEW • C SLEW • 0.577 Trapezoid RMS = æ ------------------------------------------------------------------------------------------- ö ø è Per ( – • • • C ) ) • 1 Per ( 2 0.214 R SLEW SLEW + æ ----------------------------------------------------------------------------------------------------------ö è ø Per The crest factor is then the inverse of the previous expression, and can be simplified as follows: Per CF = ---------------------------------------------------------------------------------Per – ( 0.176 • R SLEW • C SLEW ) Rearranging to solve for RSLEWCSLEW for a given crest factor yields the equation: ( CF • Per ) – Per ( R SLEW • C SLEW ) = --------------------------------------------CF • 0.176 At a RINGIN frequency of 20 Hz and a crest factor of 1.25, RSLEWCSLEW is equal to 56.8 ms. Figure 12 on page 11 illustrates the ringing and DC Feed control loop for the Am79R79 Ringing SLIC device. Note that RSN is a virtual ground. The current output at the A and B leads is 1000 times the current into the RSN pin, IRSN. SINUSOIDAL RINGING AND DC OFFSET The Am79R100 is no different in trapezoidal waveform generation than the Am79R70/79. RSLEW and CSLEW can be calculated with the same formulas that were described previously. For sinusoidal ringing with or without DC offset, there are a variety of ways to interface Zarlink SLACs as detailed below. 1. Sinusoidal ringing without DC offset Connect the RREF pin to the digital GND, as show in Figure 5. For example, feed a 20 Hz sine wave signal to VRING pin. No AC coupling capacitor is needed, though the amplitude has to be lower than 2 VPK–PK to avoid clipping. Expect the sine wave to appear at VAB without DC offset. Am79R101 VRING VRING < 2 VPK-PK RREF Figure 5. Sinusoidal Ringing without DC Offset Am79R70/79/100/101 Ringing SLIC Device Technical Overview 5 2. Sinusoidal ringing with DC offset on the RREF pin Use two resistors to build a voltage divider between the VCC and DGND. Connect the junction of the resistors to the RREF pin. The DC voltage range at the RREF pin should be within 0 V to VCC/2. Apply the sinusoidal signal with higher (or lower) than the DC reference voltage level, and observe the offset ringing waveform at VAB. If the DC bias on VRING is higher than on RREF, the DC offset voltage at the Tip and the Ring will be negative. If the voltage on VRING is lower than on RREF, the DC offset voltage on the Tip and the Ring will be positive. Refer to Figure 6. Certainly, a larger offset may contribute to heavier clipping on one side of the ringing waveform. There is always a trade off between the amplitude and the DC offset. Increasing VBAT1 from –70 V to –90 V minimizes this problem. Note that if both RREF and VRING are biased, the DC difference between the inputs will be the same as the offset voltage. VOUT_OFFSET = ( V RING IN – V RREF ) • 100 For example, if a 20 V DC offset is required at VAB during the ringing, apply 200 mV DC difference between the VRING and the RREF pins. This creates a 180°-phase shift between the input and output pins. To create the voltage divider bias circuit, a 0.1 uf cap may be needed between the bias point and the GND to reduce the transient effect. Note that the RREF and VRING inputs should not be treated as regular opamp inputs. Am79R101 VRING < 2 VPK-PK VCC VRINGIN RREF RR1 VBIAS RR2 Figure 6. Sinusoidal Ringing with DC Offset between VRING and RREF Pins VCC RR1 Am79R101 VRING VRING < 2 VPK-PK RR2 RREF Figure 7. Sinusoidal Ringing with DC Offset on the VRING Pin 6 Am79R70/79/100/101 Ringing SLIC Device Technical Overview 3. Sinusoidal ringing with DC offset applied on the VRING pin Connect the RREF pin to the DGND and use the voltage divider described in the previous section to connect the VRING pin. The shortcoming for this configuration is that there is an internal impedance around 10K in series with the pin, more tolerance may accrue at the VAB. Refer to Figure 7. 4. Interface with Zarlink SLAC™ Devices The bias source from an Zarlink SLAC device can also be connected to the Am79R101 device. On both the QSLAC™ and ASLAC™ devices, there is a Vref pin (with a reference voltage of 2.1 V in each case) which provides the DC bias for the AC coupled signal at the SLAC input and output. However, the current driving ability is not the same between the SLAC families. For the QSLAC device, additional circuitry may be needed to compensate for the current driving difference. One option is to connect a positive buffer (OP27 from Analog Devices) to the Vref output, thereby supplying four channels on the QSLAC device evaluation board with reference voltage. However, any low offset opamp will work (refer to the manufacturer’s data sheet for multi-channel application). The ASLAC device has 1 mA driving ability, which is sufficient for single channel applications, and thus has no driving problem. See Figure 8 and Figure 9. QSLAC Am79R101 VOUT VRINGIN RREF1 OP270 VREF RR1 RREF2 RR2 RREF3 RREF4 Figure 8. QSLAC™ Interface with DC Offset Am79R70/79/100/101 Ringing SLIC Device Technical Overview 7 ASLAC Am79R101 VOUT VRINGIN RREF VREF RR1 RR2 Figure 9. ASLAC™ Interface with DC Offset RING GENERATION THROUGH QUAD SLAC Traditionally the ringing signal is fed into the RSLIC device by separate external devices. Here we are introducing a ringing source generated from a digital source through the PCM highway, such as DSP. In order to pass a ringing frequency like 20hz, some filters in the QSLAC™ or ASLAC™ devices need to be adjusted. Within the SLAC™ device, the low-pass filter band limits the signal. The R digital filters (IIR and FIR), need to be programmed to pass the lower frequency, AISN, and the Z and B filters need to be turned off to stop the feedback between the VOUT and VIN paths. Gain in the receive path needs to be adjusted to meet the ring output requirement. To minimize the changes, default settings were used where possible - only two commands need to be changed: the Command [60/61] Wrd/Rd Operating Function and the Command [82/83] Wrt/Rd GR filter Coeff. The level of the digital signal can also be adjusted to satisfy the ringing output requirement. QSLAC and ASLAC Device Settings for Ring Generation through the PCM Highway: 60 20 # Write Operating Functions: choose all the default settings except for EGR = 1, and for programmed GR filter = enabled. 82 0111 #Write GR Filter Coefficients: set Grain = 1. 0E #Activate 8 With the above filter settings at 20hz, a -0.4dbm0 sine wave signal on the PCM highway for the QSLAC device, and a 1.8 dbm0 sine wave signal on the PCM highway for the ASLAC device will generate around 1.96Vp-p on the VOUT pin. This VOUT is enough for the RSLIC device to reach the required ringing output. The data collected are based on the balance ringing configurations. Please remember, after generating ringing, the filters need to be reconfigured for normal transmission setup. RINGING CIRCUITRY In the Ringing state, VTX and RDC are inactive and RDCR is active. Contributions from the VRX signal can be ignored, because it is not applied during ringing. Keep in mind that the loop current is 1000 times IRSN. Thus, the expression for ILOOPRING can be written as follows: V RDC R I LOOPRI NG = ---------------------------------------- • 1000 R DCR 1 + R DCR 2 The series resistance of the ringing feed, RS, is then: R DCR1 + R D CR2 R S = --------------------------------------200 The ringing feed requires a time constant between 15 µs and 150 µs, making the pole between 1.0 kHz and 10 kHz. This pole range will not interfere with the ringing signal, but will attenuate higher frequencies. If the time constant of the ringing feed is too low, it will decrease the ringing signal in addition to the R SLEWC- Am79R70/79/100/101 Ringing SLIC Device Technical Overview SLEW time constant, and thus increase the crest factor. The time constant in the ringing state, τRING, can be written as follows: R DCR1 • R DC R2 τ RIN G = ---------------------------------------- • C DC R R DCR 1 + R DCR 2 Note that R DCR1 + R DCR 2 determines the total current available during ringing. In this example, it was assumed that the ringing load could be as low as 1.23 kΩ. To drive such a ringing load to 40 VRMS requires 33 mArms, and has a 41 mA peak, assuming a crest factor of 1.25. RDCR will drive to a maximum of 3 V. If the desired maximum drive is 100 mA, then the maximum current into RSN has to be 100 µA. Therefore, R DCR1 + R DCR 2 must be at most 30 kΩ. If both components contribute equally, each would be 15 kΩ. C DCR should then be chosen for a time constant of 15 µs – 150 µs ; thus a 2 nF to 20 nF cap will suffice. The ringing signal drives the A and B leads alternately (positive then negative) to the supply rails. When RINGIN is high, A is closest to ground and B is near VBAT1. This is the DC condition closest to normal polarity operation. Thus, it is important to synchronize the shift from the Ringing state to the normal Active state with the time period in which RINGIN is high. This coordination will minimize any switching transients that may occur, and will reduce glitches on loop and ring-trip detection as the states change. A current limit of approximately 18 mA per REN allows enough current to ring the phone and to reliably ring trip. Because the ring trip can be affected by temperature, variation in the ring trip voltage, and variation in the voltage at the RDCR pin, it requires a design margin on the ringing current limit to ensure reliable ring trip. To ensure that the designed current limit is met under worse-case conditions, the ringing current limit was increased by 1.6 times the equation limit. RING TRIP A DC offset is traditionally required in the ringing signal for reliable ring-trip detection. Recall that this DC offset is required due to the overlap between the AC impedance on-hook and off-hook states in the central office application. The DC impedance has an off-hook maximum of 1.93 kΩ and an on-hook minimum of 10 kΩ, whereas the AC impedance has an off-hook maximum of 1.93 kΩ and an on-hook minimum of 1.23 kΩ. Again, it is much easier to perform DC ring trip because the DC impedance ratio is over 5. Following TR909 requirements, there is no overlap in either the DC or AC case. Therefore no DC offset is necessary, and AC detection is viable. In the TR909 case, minimum on-hook impedance is 1.23 kΩ (AC) and 10 kΩ (DC). The maximum off-hook impedance for both is approximately 500 Ω with Am79R79 operation. For a 5REN load, an AC threshold of 900 Ω provides sufficient margin for reliable detection and can be raised for lighter loads, if desired. For both the Am79R100 and Am79R101, ring trip is similar to the Am79R79. (Please refer to the data sheets, PID #23115A and 23116A, respectively for calculations). Due to higher battery supply and extended loop driving ability, the ring trip exhibits difficulty for the same on/off hook AC impedance ring trip detection characteristics as mentioned above. For longer loop applications, ring trip operates better with 3REN load, as required by most European countries. We guarantee clear ring trip under a 2 kΩ minimum ringer load and 1K maximum total loop resistance, limits which are considered within the range of medium loop applications. The ring-trip threshold is defined as the resistance on the loop that causes the detect output (DET) to momentarily pulse low each ringing cycle. Refer to Figure 10 below for the ring-trip waveform. This DET pin requires system level debouncing. Unfiltered RTRIP1 pin voltage 0V On-hook Off-hook DET pin waveform (unfiltered trip current) 0V On-hook Off-hook Figure 10. Ring-Trip Waveforms See Figure 13 for the ring-trip and loop-detect circuitry. The loop current is sensed and scaled to I A + I B ⁄ 300 . It is then replicated twice and sent to both the RTRIP1 pin and the RD pin. The external components on the RTRIP1 pin determine the ring trip characteristics. RRT1 is an external resistor whose function is to establish the threshold for ring-trip detection. A 24 µA current source is provided to keep the RTRIP1 pin slightly negative such that the RTRIP1 node is prevented from inadvertently becoming positive when the Ringing state is entered. Such a switch in polarity at the node would lead to a momentary false ring-trip indication. The comparator for ring trip is referenced to ground. RRT2 will have 0 V across it in ringing mode, so it is not a factor in setting the ring-trip threshold. Therefore, to select RRT1, use the following equation: Am79R70/79/100/101 Ringing SLIC Device Technical Overview 9 I LOOP æ ---------------- – 24 µAö • R RT1 = V BAT1 è 320 ø ILOOP is equal to VAB divided by the total resistance in the loop. In this case, VAB is approximately equal to VBAT1 minus 5V, and this total resistance is the sum of the fuse resistors (RF ), the series resistance of the Am79R79 Ringing SLIC device (RS), and the desired ring-trip resistance (RLRT ). Signal filtering can be included by taking into account the crest factor CF. The equation for RRT1 becomes: RT1 = 320 ⋅ CF ⋅ V BAT1 -----------------------------------------------------------------------------------------------------------------------------V BAT1 – 5 – 24µA ⋅ 320 ⋅ CF ⋅ ( R LRT + R S + 2R F ) • ( R LRT + R S + 2R F ) The transients on DET can be minimized by synchronizing the RSLIC state change with the ringing waveform, as shown in Figure 11. Ringing Reference (Input to RSLEW) 0V B(RING) A(TIP) Battery 1 Note: 1. The best time to switch between Ringing and other states to minimize detect switching transients. Figure 11. Optimum Switching Time for Minimal Transients RRT1 will always connect to VBAT1 as RRT1 is only connected in the Ringing state. For a typical application, VBAT1 is 70 V, RS is 150 Ω, RLRT is chosen for 900 Ω, CF is 1.25, and RF is 40 Ω. These conditions give RRT1 a value of 584.3K, which under test conditions gives 604K. RRT1 is switched on-chip to conserve power, since using a battery of 70 V, would cause power dissipation in the resistor to be 11 mW. RRT2 and CRT provide filtering for ring trip and are selected for a time constant of approximately 18 ms. RRT2 should be chosen to keep the voltage on the RTRIP1 pin within ±3 V (±2.5 V for the Am79R100/101). The most common problem would be to select a large value of RRT2 during ringing, have RRT1 pull down towards VBAT1. For example, if RRT2 were 50 kΩ, RRT1 450 kΩ, and VBAT1 70 V during ringing with no ringing current, RTRIP1 would be –7 V, leading to erratic operation. A value of 12 kΩ for RRT2 is a widely suitable choice. 10 Am79R70/79/100/101 Ringing SLIC Device Technical Overview A2 IA A1 A RRX RSN IRSN x1000 VRX RTX VTX Σ A4 CHP 0.018 µF RINGIN RINGIN (Figure 3) Loop Monitor and Longitudinal Control RDC2 Ringing Input C SLEW RDCR VTX RSLEW R DCR2 CDC RDCR1 CDCR Anti Sat RDC1 A5 RDC x1000 RSGH B To VCC IB RSGH or GND A3 RSGL ILOOP = IA + IB RSGL See Text Figure 12. Ringing and DC Feed DC FEED During the Active state, RDCR is open circuited and VTX and RDC are active. IRSN is the total of the current flowing in RTX, R DC1 and RDC2, and RRX. The longitudinal control loop senses VLONG, and is defined as: V A – VB V LONG = -------------------. 2 This control loop then compares VLONG to VBATX/2 and adjusts the longitudinal voltage until it’s equal to VBATX/ 2, where VBATX is the battery voltage selected by the state or B2EN. To determine the DC bias, VRX is assumed to be zero such that there is no contribution from the signal input. In this analysis, it is also assumed that there is no metallic input signal from the line, and therefore that VTX will be zero. DC loop current is then determined by the voltage on RDC and by the resistance connected from RDC to RSN (RDC1 + RDC2). The current into RSN is as follows: V RDC I RSN = -------------------------------R D C1 + R DC 2 Assuming that VAB stays out of the anti-sat region, RDC is then a fixed reference at 2.5 V. Because I LOOP = 1000 • I R SN , we can substitute the above expression for IRSN, and write the following equation: 2500 R DC 1 + R DC2 I LOOP = --------------------------------- For a typical loop current of 25 mA, R DC1 + R DC 2 is 100 kΩ. The capacitor CDC is determined by the DC loop time constant, τDC, for RDC1 and R DC2 between 16 and 30 ms. This DC loop time constant is defined by the following equation: R DC1 • R DC2 τ DC = --------------------------------• C DC R D C1 + R DC2 Note that equal values of RDC1 and RDC2 result in the smallest CDC. Using the above equation, with Am79R70/79/100/101 Ringing SLIC Device Technical Overview 11 R DC2 = R D C1 = 50 kΩ , and C DC = 0.82 µF , gives a time constant of 20 ms. The tolerance on this time constant is not critical; ±30% is adequate. Table 4. SCALE Value vs. Battery Selected Battery Selected SCALE LOOP DETECT VBAT2 11.37 Loop detect in the Active, OHT, and Standby states is determined by the external resistor connected to pin RD. For Active and OHT states, the loop detect status is determined by the total loop resistance. As shown in Figure 13, a current proportional to the loop current flows into the RD resistor, and establishes a corresponding voltage in the loop detect comparator. In these Active and OHT states, the comparator’s reference voltage, REF, is dependent upon VAB divided by a reference voltage, which is determined by the battery selected B2EN. In the following equations, this reference voltage is referred to as BREF. Because loop resistance is defined by tip/ring voltage divided by loop current, it results in a threshold comparison of loop resistance. However, for the Standby state, the comparator’s reference, REF, is a constant voltage. Here, the comparator detects at a current threshold established by the RD resistor only. Because the Standby state feed is resistive, the loop current then becomes a function of battery voltage as well as loop resistance. The Standby state loop detect status is therefore also dependent upon the battery voltage. VBAT1 12.67 Consider the Active and OHT states, where the comparator for the loop detect has a reference determined by VAB divided by BREF. This prompts the following equation: I LOOP V AB ---------------- • R D = ---------------300 BREF ILOOP is VAB divided by the total resistance on the loop. Because the resistance is made up of the fuse resistors RF, the line series resistance RSL, and the desired loop resistance for loop detect threshold RLTH, the above equation can be rewritten as follows: V AB V AB ------------------------------------------------------------------ • R D = ---------------( R LTH + R SL + 2R F ) • 300 BREF By grouping constants, this expression simplifies to: R D = ( R LTH + R SL + 2R F ) • SCALE Rearranging the equation with respect to RLTH, for Active and OHT loop detect with VBAT1 and VBAT2 is: RD R LTH = -------------------- – R SL – 2R F SCALE Table 4 shows the value of SCALE for the two different batteries. Using 100 Ω for R SL, 100 Ω for 2RF, and a desired loop detection resistance R LTH of 5 kΩ, where SCALE is equal to 12.67 for VBAT1 gives 66 kΩ for R D. 12 Now consider the Standby state. In this state the A and B pins are connected to the supplies through approximately 200 Ω each. The switches that connect the resistors require approximately 3 V of overhead. The B amplifier also has a 7 V zener in series with VBAT1, so together, the A and B amplifiers have a total of 10 V voltage drop from VBAT1 to the open circuit voltage. In the Standby state, much of the internal circuitry is shut off to minimize power dissipation, so the circuitry that remains active detects the loop current, not the resistance. The detect level is then determined by: 915 ( R LTH + 2R F + 400 + R SL ) R D ----------------------------------------------------------------------------V BAT1 – 10 In terms of RD, the equation for RLTH in Standby state becomes: R D • ( V BAT1 – 10 ) R LTH = ------------------------------------------------ – 400 – 2R F – R SL 915 RLTH should be greater than the phone off-hook resistance of around 500 Ω, and less than the expected leakage resistance of 10 kΩ. It is therefore desirable to set RLTH at about 5 kΩ. Determine RLTH using the equation for Active and OHT loop detect with a SCALE value of 12.67 (VBAT1), and then calculate the resulting threshold resistance in the other states. RD must be greater than 56 kΩ to ensure that at the lowest possible specified Standby current, detect will still occur. It is important that the detect threshold is set so that a detect in one state will be a detect in the next state. This assurance is done automatically in the Am79R79 Ringing SLIC device. In the example above, RLTH for Active VBAT1 was 5 kΩ where RD was 66 kΩ. Using the same equation and the SCALE value for VBAT2, RLTH for Active VBAT2 would then be 5.6 kΩ. Conversely, in the Standby state, calculating RLTH using the same conditions and a BAT1 of 70 V, results in a Standby threshold of 3.7 kΩ. With a 50 V BAT1, the Standby threshold is even lower, at 2.3 kΩ. During normal operation, the linecard circuit state could switch from Standby to Active VBAT2. Since RLTH is 3.7 kΩ in Standby and 5.6 kΩ in Active VBAT2, there would still be a valid detect post state transition, as the detect in Standby is 3.7 kΩ or less, and the 5.6 kΩ threshold in Active VBAT2 detects any load which is less than 3.7 kΩ. The same is true for an Active VBAT1 to Active VBAT2 Am79R70/79/100/101 Ringing SLIC Device Technical Overview switch. The threshold changes from 5 kΩ to 5.6 kΩ, and again guarantees a valid detect. No possibility of oscillation exists between states. Upon the completion of the call, the line goes to a high impedance, and the state changes from Active VBAT2 to either Standby or Active VBAT1. Active VBAT2 detects at a higher resistance than the other two states, and thus prevents an indication of on-hook conditions, while the other two states indicate an off-hook condition, again preventing oscillation between states. ANTI-SAT CHARACTERISTICS DC Feed characteristics are shown in Figure 14 for Am79R79 applications. With a given loop current and the low battery voltage VBAT2, the voltage across the loop can increase to the anti-sat threshold value VASL. For the high battery voltage VBAT1, the voltage across the loop can increase to VASH. The apparent feed synthesis loop gain is then increased while the apparent output resistance is decreased. Because the output voltage increases at a lower rate with increasing loop resistance, the amplifiers are kept in a linear region despite the fact that they are near the supplies. The two battery voltages have separate resistors to adjust the anti-sat characteristics: RRSGH to adjust VASH, and RSGL to adjust VASL. Note that while RSGL solely determines VASL, VASH is dependent on both RSGH and VASL. Both RSGH and R SGL can independently be connected to either VCC to decrease the knee voltage, or to ground to increase the knee voltage. Current Mirror RTRIP1 |ILOOP| 15 µA 300 CRT 1.5 µF RRT2 12 kΩ VNEG Ring Trip RRT1 (See Text) VBAT1 RTRIP2 Ringing State = 1 Loop Detect RD RD (See Text) REF (SLIC State Dependent) Figure 13. Ring Trip and Loop Detect Am79R70/79/100/101 Ringing SLIC Device Technical Overview 13 50 VAPPH VASH 40 VAB, volts 30 20 VAPPL 10 VASL 16 ILOOP, mA 0 32 Figure 14. DC Feed for Am79R79 The low battery apparent voltage, VAPPL, is defined by the following equation: V APPL = 4.17 V + VASL In the resistive region, the current in the loop is given as: I LOOP V APPL = ------------------------------------------------------------------------------R + R DC1 D C2 æ ---------------------------------ö + 2R + R F LOOP è ø 600 Note that this equation is only valid specifically in the resistive region, meaning that RLOOP is sufficiently large such that the part is in the anti-sat region and ILOOP is less than the designed value for the constant current region. When RSGL is connected to ground to increase the knee voltage, VASL is: 1000 • ( 104 • 10 + R SGL ) = -------------------------------------------------------------------6 6.72 • 10 + 80 • R SGL 6 Notice that when RSGL is connected to VCC, it must have a value greater than 100 kΩ. VAPPH has the same form as VAPPL, and can be written as: V APPH = 4.17 V + V ASH Loop current in the resistive region is then determined by solving: V APPH I LOOP = ------------------------------------------------------------------------------R + R DC1 D C2 æ ---------------------------------ö + 2R + R F LOOP è ø 600 V ASH = V ASH H + V ASL Typically, designs require a target value of VASL and solve for RSGL, so rearranging the equation yields: 6 6 V ASL • 6.72 • 10 + 56 • 10 R SGL = -----------------------------------------------------------------------1000 – ( 80 • V ASL ) VASH is comprised of two parts: 3 V ASL Similarly, rearranging to solve for RSGL gives: where value of VASHH depends on whether RSGH is connected to VCC or to ground. In the case of RSGH connected to ground, the equation for VASHH is: 6 V ASL • 6.72 • 10 – 104 • 10 R SGL = --------------------------------------------------------------------------1000 – ( 80 • VASL ) When RSGL is connected to VCC to decrease the knee voltage, VASL is given by the equation: 3 1000 • ( 70 • 10 + R SGH ) V ASHH = --------------------------------------------------------------------------6 1.934 • 10 + ( 31.75 • R SGH ) Rearranging to solve for RSGH with the above VASHH yields the equation: 3 1000 • ( R SGL – 56 • 10 ) V ASL = ---------------------------------------------------------------6 6.72 • 10 + ( 80 • R SGL ) 14 6 6 V ASHH • 1.934 • 10 – 70 • 10 R SGH = ---------------------------------------------------------------------------------1000 – ( 31.75 • V ASHH ) Am79R70/79/100/101 Ringing SLIC Device Technical Overview When RSGH is connected to VCC, VASHH is given as follows: 3 1000 • ( 2.75 • 10 + R SGH ) V ASHH = --------------------------------------------------------------------------6 1.934 • 10 + ( 31.75 • R SGH ) The following is a Mathcad program calculation for the Am79R100/101 DC feeds. Now, rearranging to solve for RRSGH with the above VASHH gives: 6 lization of VBAT2. To meet the UL1950 specification requirements, the on-hook voltage is clamped at 54 V in the Standby state. 6 V ASHH • 1.934 • 10 – 2.75 • 10 R SGH = ---------------------------------------------------------------------------------------1000 – ( 31.75 • V ASHH ) Clearly, in order to calculate VASH, VASL must first be determined. Take for example, a case where the RSGH and RSGL pins are open circuit. The values of VASL and VASH can then be found straightforwardly. Since an open circuit is an infinite resistance; the equations reduce to give VASL equal to 12.5 V, and VASHH equal to 31.5 V. Recall that VASH, is the sum of VASHH and VASL, and so it is equal to 44 V. On the other hand, assume a design needs VASL to be 15 V and VASH to be 40 V. In this case, because VASL is increased, the equation in which RSGL is connected to ground is the proper one to use. Solving it yields R SGL equal to 16 kΩ. As the resistance decreases, VASL increases. Thus, the maximum VASL occurs when RSGL is zero, and it is equal to 15.47 V. Subtracting the necessary 15 V VASL from the target 40 V VASH yields VASHH equal to 25 V. The minimum VASHH occurs when RSGH is connected to VCC, and is equal to 20.1 V. The minimum allowable R SGH to VCC connection is 100 kΩ, so the target (VASH = 40 V) is achievable. With an RSGH value of 221 kΩ, VASHH will equal 25 V. Therefore, VASH will equal 25 V plus 15 V (equaling 40 V). So as one decreases VAS, the RSGL and RSGH values must remain greater than or equal to 100 kΩ. The Am79R100 and Am79R101 default settings are different from the Am79R79, as a new formula for the DC feed calculation was adopted. The Rsgl = open and Rsgh = open were changed to Rsgl = open and Rsgh = GND. The DC feed curves are still similar to one anoth er, except that the both the Am79 R100 a nd Am79R101 have more headroom than the Am79R79. The Am79R100/101 also have lower On-hook voltages (VAB = 45 V) than the Am79R79 (VAB = 49 V). Because the Rsgl is now set to GND, the knee of the low battery anti-sat entry can be raised to 25 V from its nominal value of 12.5 V. This increase boosts the maximum uti- Am79R100/101 DC Feed Curve RDC := 100000 VBAT1 := 95 VBAT2 := 24 Il := 0, 0.0001...0.06 R1 := 600 (RI = RI + RF, RF = 0) RSGL := 1000000000 Low bat operation: 2500 VAB := ------------- • R1 Rdc :Constant-current 61.44 ( 125000 + Rsgl ) VASL := ----------------------------------------------------------308000 + 4.92 • Rsgl :R SGL = open (1 GΩ) VASL = 12.489 VAPPL := 4.17 + Vasl :Vappl with low battery VAPPL = 16.659 ILIM := 0.025 :Constant current 4.17 V1(Il):= V APPL – ----------- • Il :Curve calculation I LIM VABl(Il) := if(Il >ILIM, ILIM, Vl(Il)) :Connect the curves High bat operation: RSGL := 0 :R SGH = GND default setting 61.44 • ( 101000 + Rsgh ) VASH := Vasl + ------------------------------------------------------------------223000 + 4 • Rsgh VASH = 40.316 VAPPH := 4.17 + VASH VAPPH = 44.486 4.17 Vh(Il) := V APPH – ----------- • Il :Curve calculation Ilim VAB2(Il):= if(Il > Ilim, Ilim, Vh(Il)) :Connect the curves Refer to Figure 15 for DC feed result. Am79R70/79/100/101 Ringing SLIC Device Technical Overview 15 60 50 VAPPH VAB(Volt) Vabl ( Il ) VASH 40 30 Vab2 ( Il ) 20 VAPPL VASL 10 0 0 0.005 0.01 0.015 0.02 0.025 0.03 0.035 0.04 Il(A) Figure 15. DC Feed for Am79R100/101 BATTERY VOLTAGES The Am79R79 Ringing SLIC device supports the selection of two battery voltages. VBAT1 is always connected to the substrate and must be more negative than VBAT2. Its value may go as low as –75 V. VBAT2 can range from –19.5 V to VBAT1. Figure 16 shows the recommended configuration as well as the general sense of the logic switch: if B2EN is a logic High, VBAT1 is selected; if B2EN is Low, VBAT2 is selected. The diode isolation allows VBAT1 to override VBAT2 when the internal switch closes. When the switch opens, the diode to VBAT2 is forward biased and VBAT2 is applied to the circuit. In the Standby state, the Am79R79 Ringing SLIC device is internally connected to VBAT1, so the selection of B2EN in the Standby state is irrelevant. The part (Am79R79) will always connect to VBAT1 to meet the open circuit voltage requirements for FAX machines and MTU’s. B2EN BAT1 (Most 0.1 µF Negative) BAT2 0.1 µF Subs. VBAT1 VBAT2 B2EN = H selects VBAT1 B2EN = L selects VBAT2 To Circuitry loop length, crest factor, load (number of REN), fuse resistors, and the ring current limit resistors. 70 Ω SLIC RS 2RF RLOOP + – RLOAD VBAT1 – 2.5 ( R DCR1 + R DCR2 ) R S = --------------------------------------------200 Figure 17. Simplified Ring Generator Model TR909 requires a ringing voltage of 40 Vrms and a CF of 1.2–1.6. To determine VBAT1, work backwards from the load using Ohm's Law. Using a value of 1.4 kΩ for a 5REN load, a current of 29 mArms is needed to get 40 Vrms. From the model, use the equation: V BAT 1 = I RIN G • CF • ( R LOOP + R LO AD + 2R F + R S + 70 ) + 2.5 For example, if CF = 1.25, R LOAD = 1.4 kΩ (5REN), RLOOP = 100 Ω, IRINGLIM = 55 mA, and RF = 50 Ω; then, RS = 166 Ω and VBAT1 = 68 V. If the load changes to 3REN, then I RING must be 17.1 mArms, RS = 277 Ω and VBAT1 = 64.2 V. Figure 16. VBAT1 and VBAT2 VBAT1 Specification VBAT1 is set on the high end by the silicon process, but limit it to 75 V. Factors that determine the low end are 16 If you want to lower V BAT1 or drive a longer loop, leave IRINGLIM higher in order to lower R S. For example, R S = 166 Ω with 3REN results in VBAT1 = 61.8 V. CALL WAITING AND CALLER ID Some Call Waiting Caller ID (CWCID) devices have special requirements to make them function correctly. The CWCID spec necessitates that the CPE respond to a tone requesting if the device can accept the CWCID Am79R70/79/100/101 Ringing SLIC Device Technical Overview data. If the device can accept the data, it mutes the connection to the phone, sends an acknowledgement, receives the data, and finally reconnects the phone. The CWCID device must also determine if there is another extension off hook, which could cause two undesirable problems. One, the voice from the other extension could interfere with the data sent, and two, the data could be objectionably loud to the extension phone. The solution to these two problems on some CWCID boxes is to go to a higher impedance state. An impedance state that is not at such a high impedance as to look like an on-hook event, but is at a high enough impedance as to see if the voltage on the line increases. If the low battery voltage is below a predefined value, the CWCID device will interpret the low line voltage as an extension phone off-hook, and will not acknowledge the request to send CWCID data thereby preventing the transfer of information. The voltage required at the tip and ring is about 20.6 V. Assuming 100Ω of fuse resistors, and a 25mA loop, there would need to be 23.1 V at the SLIC assuming a 25 mA loop of zero length. The voltage must increase to accommodate the loop resistance. About 5V of headroom is needed by the SLIC device for normal operation, thus the supply required amounts to approximately 29 V, including the diode in the supply lead. For the Am79R79, the RSGL pin must be tied to ground to increase the open circuit voltage to a voltage high enough to support the device. The Am79R100 and Am79R101 have sufficient default open circuit voltages to support these devices so long as the low battery supply is sufficiently high. VNEG The circuitry driven by VNEG includes a VEE regulator that allows VNEG to be driven by any voltage between –5 V and VBAT2. It is usually connected to the Vneg pin on the VBAT2 pin side, in so doing, the connection avoids the reverse substrate by connecting to the supply side. A resistor can be placed in series with the connection to limit on-chip power dissipation. The resistor value must be chosen such that it is less than the voltage drop between BAT2 and –5 V, when a 2 mA current is applied. For the Am79R100 and Am79R101 applications, the B2EN pin is eliminated. Software changes the batteries in each mode as defined in the following chart: Table 5. Operating modes via battery (Am79R100 and Am79R101 only) C1 C2 C3 State E1=1 E1=0 Battery 0 0 0 Open Circuit Ring Trip Ring Trip VBAT2 0 0 1 Ringing Ring Trip Ring Trip VBAT1 0 1 0 Active Loop Det. Ground Key VBAT2 0 1 1 On Hook TX (OHT) Loop Det. Ground Key VBAT1 0 1 0 Tip Open Loop Det. Ground Key VBAT1 0 1 1 Standby Loop Det. Ground Key VBAT1 0 1 0 Active Pol. Rev. Loop Det. Ground Key VBAT2 0 1 1 OHT Pol. Rev. Loop Det. Ground Key VBAT1 LIGHTNING AND POWER CROSS To meet Bellcore requirements, and survive a lightning and power cross test, an appropriate protection circuit is required to guarantee SLIC operation within the silicon limit. Because the supply voltages are different, the rating for the protection circuit must be adjustable. For level two protection circuits, there are two commonly used devices: 1) a diode bridge and thyristor surge protector; and 2) a battery tracking protection thyristor IC. For the Am79R79 device with a –70 V desired high battery voltage, the maximum thyristor breakover voltage must be specified not to exceed –70 V. Its minimum breakover voltage must be specified not to be less than the maximum A-to-B line voltage (on hook). These specifications ensure that the current is not sourced from the SLIC device under normal line conditions. The battery tracking protection device (which can be external programmed by the battery) has a minimum breakover voltage which is guaranteed to be greater than Vbat, such that no current is drained during normal operation. Power Innovation’s programmable over voltage protection device, part number TISP61089A (maximum 100 V limit) is suggested for Am79R100 and Am79R101 SLIC applications. Am79R70/79/100/101 Ringing SLIC Device Technical Overview 17 For the bridge rectifier and thyristor device combination, the fast or ultra fast diodes are strongly recommended for lightening protection. For details, please refer to the application note, PID# 22648A: Generic SLIC Device Protection From Lightning Surges and AC Mains Power Cross. RELAY DRIVERS The relay drivers RYOUT1 and RYOUT2 are transistors with internal snubber circuits, provided to permit up to 75 mA of relay driving, per driver, to energize a relay. To create additional versatility, the common emitter connection to the drivers was brought out to a pin. When an application does not need relay drivers, the drivers can be used to implement test functions as illustrated in Figure 18. With the addition of an external diode and test a load resistor, RYOUT2 is primed for loop continuity testing, whereas RYOUT1 is primed for ground-key testing. The control pin can be left open or connected through a resistor tie to VCC. A UL REQUIREMENT There are several UL requirements on secondary circuit operation. UL 1950 considers a hazardous voltage to be a voltage exceeding 42.4 V peak or 60 V DC. This is in line with MTU compliance, which requires DC voltage to be 42.75 V to –56 V on the 2-wire terminal during the idle line condition. The Am79R100/101 utilizes the diode clamp scheme to limit the on-hook voltage lower than 54 V DC in standby mode to meet the voltage and MTU compliance. Borrowed from FCC part 68 and applicable to UL 1950 regarding the ringing source requirement specified during the quiet intervals, the voltage to ground should not exceed 56.5 V DC. Am79R100/101 will meet this requirement in all 8- operation modes. For Am79R79 SLIC applications, tip open, standby and OHT mode will not meet the UL requirement if the VBAT1 is higher than 70 V. In order to meet that requirement, VBAT1 voltage should be reduced or RSGL and RSGH resistors need to adjust to maintain the voltage across Tip and Ring and the voltages from Tip and Ring to ground in the acceptable ranges. The active state should be used instead of the standby state. Design engineers should consult the agency to decide if the UL compliance is necessary. B RYOUT1 RYOUT2 RYE Figure 18. Using Relay Drivers for Test Loads 18 Am79R70/79/100/101 Ringing SLIC Device Technical Overview APPENDIX 1 DESIGN EXAMPLE The Am79R79 Ringing SLIC device has two current limits that can be set independently. These user-defined current limits are for the ringing feed and the DC loop feed. The currents are established by connecting a network from RDC to RSN for the DC Feed, and a network from RDCR to RSN for the ringing feed. The following illustrates the Am79R79 application. (Please refer to the data sheets, referenced previously). The equation that describes the DC loop current limit is: 2500 I LOOP = --------------------------------R DC 1 + R DC2 For the ringing feed, the current is: — Allows for about 18 mA per phone with some current for leakage and tolerance. In the Ringing state, the following points should be considered: The current limit set by the Am79R79 ringing SLIC device determines the peak current. The worst-case requirement for current drive occurs when the loop length is zero, and there are no fuse resistors. The phone goes off-hook in this case. — Zero loop requires more current because the fuses are in series with the phone, and add to the total impedance. The time constant for the DC loop is: V ( RDCR ) • 10 00 I LOOPRI NG = ----------------------------------------------R DC R1 + R DCR 2 R DC 1 • R D C2 τDC = --------------------------------- • C DC = 20 ms R DC1 + R DC 2 The maximum value of ILOOPRING occurs when V(RDCR) is at its peak value, which occurs at ±3 V. This current, called IRINGLIM, is defined by the following: With given values for RDC1 and RDC2, C DC = 820 nF . The ringing time constant is therefore: 3000 I RINGLIM = ---------------------------------------R DCR 1 + R DCR2 R D CR1 • R DCR 2 τ RIN G = ---------------------------------------- • C DC R R DCR 1 + R DCR2 IRINGLIM is the current limited peak value of the ringing current. To determine the rms value, IRINGLIM must be divided by the crest factor. = 15 µs to 150 µs Appropriate values for ILOOP and IRINGLIM must be chosen in order to supply sufficient loop current to power an off-hook phone (or two). ILOOP and IRINGLIM must also provide sufficient ringing current to recognize when the phone goes off-hook during ringing without prematurely tripping into a normal ringing load. Consider the current needed for the DC feed portion. The VBAT1 standby mode is in use with its current limit around 35 mA. But be aware that there will exist a brief moment when the phone will be off-hook (long loop). In such a case the phone would be operating in Active mode, VBAT1, and drawing more current. After off-hook is detected, firmware usually changes from VBAT1 to VBAT2 in Active mode, to conserve power. A typical value for ILOOP is 25 mA: 20 mA for an off-hook phone with touch tone 5 mA for leakage and component tolerance If the design requires two off-hook phones: 40 mA can be used — Sufficient current for a touch tone phone to initiate a call Using a τRING of 100 µs, CDCR ≈ 12 nF. RRT1 should be calculated from the equation for RRT1 on page 10. Because the value of IRINGLIM effects RRT1, the value of RRT1 must also be changed any time the ringing current limit is altered. Keep in mind that the value of RRT1 is also dependent on the chosen crest factor (CF), the battery VBAT1, and the desired load at which the ringing will be detected (RLRT). The ring detect threshold, RLRT, is the value at which ringing is just detected. Because the ringtrip is only lightly filtered, this detect can be expected to glitch, especially near values of R LRT. Hence, the ringtip value is typically chosen well away from the resistance presented by an the sum of an off-hook phone, line resistance, and fuse resistors. Here, a phone is specified to be no more than 430 Ω off-hook, and the sum of fuse resistors and line resistance may be a total of 70 Ω or more. Therefore 500 Ω is an acceptable number to use to determine off hook resistance. The ringing impedance of the load must to be taken into account when setting the threshold. If driving a 5REN load with a worst-case leakage resistance of 10 kΩ are the desired conditions, then expect the ring impedance to be about 1200 Ω. R LRT must then be selected about halfway between the off-hook resistance and the ringing impedance; 900 Ω is a recommended value for a 5REN load. Am79R70/79/100/101 Ringing SLIC Device Technical Overview 19 The following is a detailed example for a 5REN application: —IRINGLIM maximum = 0.110 Amps Assuming: —Using IRINGLIM nominal R DC1 = R DC2 — I RI NGLI M = 3000 ⁄ ( R DCR 1 + R D CR2 ) R DCR1 = R DCR2 —The RDCR value becomes 16890 Ω ( R DCR 1 = R DCR2 = 16.9 kΩ ) . RINGIN = 20 Hz VBAT1 = 70 V Overhead = 5 V — The nominal margin between the ring trip current and the ringing loop current limit is 40.15% T arg et total loop impedance = 900 Ω — RRT1 can now be found by solving the following: Estimated 5REN impedance = 1412 Ω RSLEW = 150K and CSLEW = 0.33 µ F R RT1 = 320 ⋅ CF ⋅ ( R LRT + 150 + 2RF ) ⋅ DC Loop Current V BAT1 --------------------------------------------------------------------------------------------------------------------------------------V BAT1 – 5 – ( 24mA ⋅ 320 ⋅ CF ( RLRT + 150 + 2RF ) ) — For a 25 mA DC loop current — R DC1 + R DC2 = 2500 ⁄ I LOOP Crest Factor Current needed to drive the target RLRT (V – Overhead ) BAT1 — I RLRT = æ -----------------------------------------------------ö = ( 0.072 Amps ) è ø R LRT = 590 K —Therefore, R DC1 = R DC2 = 49.9 kΩ ( Period ) — CF = ------------------------------------------------------------------------------------------------( Period – ( 0.176 • R SLEW • C SLEW ) ) The following is an abbreviated example for a 3REN application using the same previous assumptions: (V – Overhead ) — Therefore, IRINGLIM nominal = 0.070 Amps — IRINGLIM maximum = 0.086 Amps ( V BAT1 – Overhead )ö 928 Ω æ R LRT = -----------------------------------------------------è I R TD maximum ø —Therefore, IRINGLIM nominal is 0.089 Amps 20 — Using IRINGLIM nominal —The RDCR value becomes 21481 Ω ( R DCR 1 = R DC R2 = 21.5 kΩ ) . Ringing Current Limit — There is a ±16.5% tolerance on RDCR and a ±6% temperature tolerance. Ringing Current Limit — IRINGLIM = 0.055 Amps — Using IRTD maximum, the RLRT value becomes —IRINGLIM = 0.070 Amps — Using IRTD nominal, the RLRT value becomes 1205 Ω — Set IRINGLIM minimum equal to IRTD maximum —IRTD Maximum = 0.070 Amps — Set IRINGLIM minimum equal to IRTD maximum Current at ring trip —IRTD maximum = 0.055 Amps —IRTD nominal = 0.063 Amps — I3REN = 0.015 Amps —IRTD nominal = 0.050 Amps — IRTD maximum is the current the supply must be able to provide. IRTD minimum can be set a few mA above the current needed for 5REN. — There is a ± 10% tolerance range for IRTD Current at 3REN — Let's set IRTD minimum = 0.045 Amps Current at ring trip — Set IRTD minimum = 0.057 Amps Except target total loop impedance = 1200 Ω — IRTD maximum is the current that the supply must be able to provide. IRTD minimum can be set a few mA above the current needed for 3REN. Current at 5REN BAT1 — I5REN = æ -----------------------------------------------------ö = ( 0.046 Amps ) è ø [ 5REN ] Ring Trip Current Margin Ring-Trip Current Margin — The nominal margin between the ring-trip current and the ringing loop current limit is 40.15%. — RRT1 = 768 kΩ Am79R70/79/100/101 Ringing SLIC Device Technical Overview APPENDIX II AC CHARACTERISTICS This section assumes the use of a simple codec, and that an op-amp is used for the transhybrid balance. (Some codecs, such as the SLAC™ device, have the op-amp onboard. If you are using a SLAC device, you can set Z T and ZRX. You can choose a wide variety of real and complex two-wire impedances, transhybrid + balances, and gains with the DSP filters in the SLAC device.) In Figure 1, V IN and VOUT connect to the CODEC. Make the component calculations in this order: twowire input impedance, receive path gain, transhybrid balance, and transmit path gain. ZTX VTX ZFB – GTX = 0.5 RF ZT SLIC K = 1000 A ZRX ZB – ZL RSN + – B + VOUT VIN RF Figure 1. AC Model Two-Wire Input Impedance OR V1 Define: Z 2WIN = ------------I LOOP OR Write the loop equations: Now solve for ZT: (1) ALSO V TX = 0.5 • ( V 1 – I LOOP • 2R F ) V TX I LO OP = 1000 • --------ZT (2) Z T I LOOP V TX = ------------------------1000 For maximum power transfer, terminate the loop in the complex conjugate of its characteristic impedance (specified by the regulatory agencies in each country). ZT determines the input impedance (real or complex) of the SLIC. To calculate two-wire input impedance, Z 2WIN , replace Z L with voltage source V 1 and let VIN = 0. Substitute (2) into (1) Z T • I LOO P -------------------------- = 0.5 • ( V 1 – I LOOP • 2R F ) 1000 V1 ZT - + 2R F - = -------Z 2WIN = ------------I LOOP 500 Z T = 500 • ( Z 2WIN – 2RF ) To get a two-wire input impedance of 600 Ω with RF = 50 Ω, then: 5 Z T = 2.5 • 10 Ω Am79R70/79/100/101 Ringing SLIC Device Technical Overview 21 Receive Path Gain Gain from the four-wire side to the two-wire side, loaded, is G42L. Be careful not to exceed the drive capability of the SLIC. Refer to the AC model in Figure 1 and write the loop equations. V TX Define: G 44L = --------V IN Write the loop equations: I LOO P • Z L Define: G 42L = ------------------------V IN (1) V TX = – 0.5 • I LOOP • ( Z L + 2RF ) (2) æ V TX V IN ö - + ----------÷ I LO OP = 1000 • ç --------è Z T Z RXø Write the loop equations: (1) (2) I LO OP æ V TX V IN ö = 1000 • ç --------- + ----------÷ è Z T Z RXø V TX = – 0.5 • I LOOP • ( Z L + 2RF ) Substitute (2) into (1) and solve for VTX/VIN: –ZT 500 • ( Z L + 2R F ) V TX G 44L = --------- = ---------- • ------------------------------------------------------Z RX Z T + 500 • ( Z L + 2R F ) V IN So that: Substitute (2) into (1) and solve for ILOOP/VIN: I LO OP 1000 1 ------------- = ------------ • ---------------------------------------------------Z RX 500 • ( Z L + 2R F ) V IN 1 + ----------------------------------------ZT G 44L = – 0.583 Now calculate the component ZB for the balance circuit. Again, write the loop equations around the circuit. V TX • Z FB V IN • Z FB ------------------------- + ------------------------ = 0 Z TX ZB OR ZT 1000 • ZL I LOO P • Z L - • ------------------------------------------------------ = --------G 42L = ------------------------Z RX Z T + 500 • ( Z L + 2RF ) V IN ZFB drops out æ V INö V TX -÷ --------- = – ç -------è ZB ø Z TX Now solve for ZRX: ZT 1000 • Z L Z RX = ----------- • ------------------------------------------------------G 42L Z T + 500 • ( Z L + 2R F ) Continuing the example above with Z T = 250 kΩ, ZL = 600 Ω, RF = 50 Ω, and now G42L = unity, then: 5 Z RX = 2.5 • 10 Ω Transhybrid Balance A by-product of the two- to four-wire conversion is that some of the receive signal, VIN, appears in the transmit path at the VTX pin. You must reduce this echo. Use the op-amp circuit to remove as much of this signal as possible from the transmitted signal. OR æ Z TX ö -÷ Z B = – ç ---------è G 44Lø If ZTX = 20 kΩ, and G44L = –0.583 as before, then 3 Z B = 34.31 • 10 Ω and ZFB sets the transmit path gain. The total load on V TX must be greater than 20 kΩ to ensure proper operation of the RSLIC. Transmit Path Gain To optimize transhybrid balance, use the following procedure. First, find the transfer function of VIN to VTX, called G44L or four-wire return gain. Then calculate the impedance, ZB, to cancel VTX in the op-amp summing circuit. Notice that there is a 180° phase shift from VIN to VTX. If ZL is resistive, Z B also is resistive. If ZL is complex, Z B also is complex. Additionally, the SLIC contributes a small delay that you can adjust for by splitting Z T and connecting a capacitor (C T = 60 pF typical) from that junction to ground. When adjusting the gain in the transmit path, do not exceed the input range of the codec. First, calculate the two-to four-wire gain, G24. The total transmit path gain is G24 multiplied by the gain through the op-amp. Refer to the AC Model in Figure 1 and substitute V1 for ZL. Assume VIN = 0 V. Determine G44L (Refer to the AC Model in Figure 1) using the following equation: Write the loop equations: 22 V TX Define: G 24 = --------V1 Am79R70/79/100/101 Ringing SLIC Device Technical Overview V TX = 0.5 • ( V 1 – I LOOP • 2R F ) (1) (2) I LO OP So that: G 24 = 0.417 For unity transmit path gain select: 1000 • V TX = --------------------------ZT Z FB 1 --------= -------Z TX G 24 Substitute (2) into (1) and solve for VTX/V1: If ZTX = 20 kΩ, then: ZT V TX G 24 = --------- = 0.5 • -----------------------------------Z T + 2RF • 500 V1 3 Z FB = 47.96 • 10 Ω Application Schematic RD RTRIP1 RRT2 RD 0.1 µF ZTX RRT1 VTX CRT RTRIP2 0.1 µF ZRX RSN VOUT RF A(TIP) RDC2 RDCR2 IREF HPA BAT1 G Am79R79 18 nF U1 RREF HPB RDC1 B(RING) RF 2.2 nF CDC RDCR1 RDCR 0.1 µF 150 kΩ RINGIN BAT2 0.1 µF CDCR RDC VBAT1 BAT1 1/4 Am79Q5457 QSLAC™-NP ZB ZT 2.2 nF IIN RSLEW VBAT2 BGND AGND/ DGND See Notes CSLEW Notes: 1. The transmit path gain when using the QSLAC-NP differs slightly from the standard CODEC case. Replace ZFB in the equation with 3RREF. 2. The input to RSLEW should be a 50% duty cycle, CMOS-compatible signal. 3. If the protection device U1 is needed, battery-reference it with the gate tied to BAT1. 4. RSGH, RSGL are left open in this example. 5. VNEG can be connected to BAT2 through a current limiting resistor. 6. The digital signals B2EN, DET, E1, D1, D2, and C3–C1 are not shown. 7. The 0.1 µF capacitors at the QSLAC-NP are for AC coupling and can be 20% tolerance of type X7R. 8. The 0.1 µF capacitors on VBAT1 and VBAT2 are for supply de-coupling. 9. The 2.2 nF capacitors on A and B are for EMI susceptibility. 10. The 18 nF capacitor on HPA and HPB is a DC-blocking capacitor. 11. Not shown is the splitting of Z T and the delay compensation capacitor, CT. Am79R70/79/100/101 Ringing SLIC Device Technical Overview 23 ADDITIONAL REFERENCES Am79R70 Ringing SLIC Data Sheet, PID# 21776, Rev D Am79R79 Ringing SLIC Data Sheet, PID# 19752, Rev B Am79R79 Ringing SLIC Technical Overview, PID# 19768, Rev C Am79R79 Ringing SLIC Device Call Processing Considerations Application Note, PID# 21781, Rev A Am79R79 Ringing SLIC User’s Guide, PID# 21109, Rev A Am79R100 Ringing SLIC Data Sheet, PID# 23115, Rev A Am79R101Ringing SLIC Data Sheet, PID# 23116, Rev A Am79R100/101 vs. Am79R79 Device Comparison Brief, CPD/P-239, Rev A Linecard Products for the Public Infrastructure Market Data Book, 1998 Bigelow, S.,Understanding Telephone Electronics, Newnes, 1997 Reeve, Whitham D., Subscriber Loop Signaling and Transmission Handbook: Analog, IEEE Press, 1991 24 Am79R70/79/100/101 Ringing SLIC Device Technical Overview RING TIP A K2 K2 BAT2 D1 C2 0.01 µF D3 RNEG 10 kΩ D2 NC NC NC NC NC Prot. Rtn CHP 18 nF C1 0.1 µF CBX 2.2 nF A NC TISP 61089 G U2 K1 K1 BAT1 RFB 25 Ω BAT1 RFA 25 Ω CAX 2.2 nF RRT1 515 kΩ RRT2 12 kΩ CRT 1.5 µF VNEG VBAT2 VBAT1 U1 VCC AGND/DGND RINGIN B2EN C3 C2 C1 DET E1 VTX RDCR RDC RSN RD RSGL RSGH C3 0.1 µF Am79R79 SLIC BGND RYOUT1 RYOUT2 RYE D2 D1 B(RING) HPB HPA A(TIP) RTRIP2 RTRIP1 +5 V RDCR2 15 kΩ CSLEW 0.33 µF RSLEW 150 kΩ CDCR 10 nF RDCR1 15 kΩ CDC 0.82 µF RDC1 50 kΩ RDC2 50 kΩ RD 66 kΩ RSGL Open RSGH Open CB 0.1 µF RBAT2 365 kΩ ROUT1 47 kΩ CVTX 0.1 µF RIN 47 kΩ RBAT1 365 kΩ BAT1 RT 360 kΩ CM 0.01 µF CVRX 0.1 µF RM 68 kΩ RRX 220 kΩ NC NC NC NC NC IBAT I/O4 I/O3 I/O2 I/O1 C2 C1 VIN VREF VM VOUT U3 VCCD +5 V NC NC IRTA Am79C2031 ASLAC Device IRTB IDC VLBIAS IAB IDIF ISUM AGND VCCA +5 V CMOS RINGIN MCLK MPIINTERFACE INTERFACE MPI PCMINTERFACE INTERFACE PCM RREF 7.87 kΩ IREF MCLK RST INT CS DCLK DI/O DRA TSCA DXB DRB TSCB FS PCLK DXA DGND APPENDIX III QSLAC and Ringing SLIC Application Circuit (only one channel displayed) Am79R70/79/100/101 Ringing SLIC Device Technical Overview 25 Table 6. Parts List Single Channel Ringing Subscriber Line Circuit g g g D1 1N400X D2 1N400X D3 1N400X C1 0.1 µF, 20%, 100 V C2 0.01 µF, 20%, 100 V Vbat1 dependent C3 0.1 µF, 20%, 10 V Supply decoupling C4 0.1 µF, 20%, 10 V Supply decoupling C5 0.1 µF, 20%, 10 V Supply decoupling CAX 2.2 nF, 20%, 100 V EMI suppression CBX 2.2 nF, 20%, 100 V EMI suppression CRT 1.5 µF, 10%, 10 V Application dependent CHP 18 nF, 20%, 100 V CDC 820 nF, 20%, 5 V Application dependent CDCR 10 nF, 20%, 5 V Application dependent CM 10 nF, 20%, 5 V Application dependent CSLEW 0.33 µF, 20%, 5 V Application dependent CVTX 0.1 µF, 20%, 5 V CVRX 0.1 µF, 20%, 5 V CB 0.1 µF, 20%, 100 V RFA 25 Ω, 2%, 2 W Value and rating application dependent RFB 25 Ω, 2%, 2 W Value and rating application dependent RRT1 515 kΩ, 1%, 1/8 W RRT2 12 kΩ, 1%, 1/8 W RD 66 kΩ, 1%, 1/8 W Application dependent RDCR1 15 kΩ, 1%, 1/8 W Application dependent RDCR2 15 kΩ, 1%, 1/8 W Application dependent RDC1 50 kΩ, 1%, 1/8 W Application dependent RDC2 50 kΩ, 1%, 1/8 W Application dependent RT 360 kΩ, 1%, 1/8 W Application dependent RRX 220 kΩ, 1%, 1/8 W Application dependent RM 68 kΩ, 5%, 1/8 W Application dependent ROUT1 47 kΩ, 1%, 1/8 W Application dependent RIN 47 kΩ, 1%, 1/8 W Application dependent RBAT1 365 kΩ, 1%, 1/8 W RBAT2 365 kΩ, 1%, 1/8 W RREF1 7.87 kΩ, 1%, 1/8 W RNEG 10 kΩ, 10%, 1/4 W RSLEW 150 kΩ, 1%, 1/8 W U1 26 Vbat1 dependent Application dependent Application dependent Am79R79 U2 TISP61089 U3 Am79C2031 Am79R70/79/100/101 Ringing SLIC Device Technical Overview For more information about all Zarlink products visit our Web Site at www.zarlink.com Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively “Zarlink”) is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink. This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user’s responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink’s conditions of sale which are available on request. Purchase of Zarlink’s I2C components conveys a license under the Philips I2C Patent rights to use these components in an I2C System, provided that the system conforms to the I2C Standard Specification as defined by Philips. Zarlink, ZL, the Zarlink Semiconductor logo and the Legerity logo and combinations thereof, VoiceEdge, VoicePort, SLAC, ISLIC, ISLAC and VoicePath are trademarks of Zarlink Semiconductor Inc. TECHNICAL DOCUMENTATION - NOT FOR RESALE