5.5 the ebers-moll model (advanced topic)

advertisement

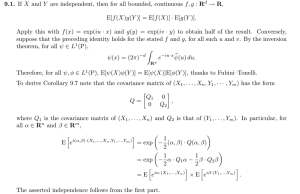

286 Chapter 5 Bipolar Junction Transistors C iC C B iC iB iR ββR iE E IS ββR B iT = iF – iR iB iF ββF [ ( ) IS ββF vBE vBC iT = IS exp V – exp V T T ( )] iE (a) E E iE E B iE iB iF ββF iC C IS ββF B iR ββR [ ( ) iT = iF – iR iB IS ββR vEB vCB iT = IS exp V – exp V T T ( )] (b) iC C Figure 5.8 (a) Transport model equivalent circuit for the npn transistor. (b) Transport model equivalent circuit for the pnp transistor. Exercise: Find i T if I S = 10−15 A, VBE = 0.75 V, and VBC = −2.0 V. Answer: 10.7 mA Exercise: Find the dc transport current I T for the transistor in Example 5.1 on page 282. Answer: I T = 1.47 mA 5.5 THE EBERS-MOLL MODEL (ADVANCED TOPIC) The classic mathematical model for the bipolar junction transistor is the Ebers-Moll model formulated by J. J. Ebers and J. L. Moll from Bell Laboratories in the early 1950s [5]. The Ebers-Moll model provides an alternative view or representation of the equations developed in Sec. 5.2 and is formulated using the same superposition of currents in the forward and reverse directions. 5.5 The Ebers-Moll Model 287 5.5.1 Forward Characteristics of the npn Transistor The total current crossing the emitter-base junction in the forward direction in Fig. 5.3 is described by Eq. (5.5) and can be rewritten as iE = vB E vB E IS exp − 1 = I E S exp −1 αF VT VT where I E S = IS αF (5.20) in which the new parameter I E S represents the reverse saturation current of the base-emitter diode. The collector current in Eq. (5.1) can be rewritten in terms of I E S as vB E vB E i C = I S exp − 1 = α F I E S exp −1 VT VT (5.21) The forward common-base current gain α F represents the fraction of the emitter current that crosses the base and appears in the collector terminal. 5.5.2 Reverse Characteristics of the npn Transistor For the reverse direction depicted in Fig. 5.4, the current crossing the collector-base junction is described by Eq. (5.11) and can be written as v BC v BC IS iC = − exp − 1 = −IC S exp −1 αR VT VT where IC S = IS αR (5.22) The new parameter IC S represents the reverse saturation current of the base-emitter diode. The emitter current from Eq. (5.9) can be rewritten in terms of IC S as v BC v BC i E = −I S exp − 1 = −α R IC S exp −1 VT VT (5.23) The reverse common-base current gain α R represents the fraction of the collector current that crosses the base from the emitter terminal. 5.5.3 The Ebers-Moll Model for the npn Transistor The full Ebers-Moll equations are obtained by combining Eqs. (5.20) to (5.23): vB E v BC i E = I E S exp − 1 − α R IC S exp −1 VT VT vB E v BC i C = α F I E S exp − 1 − IC S exp −1 VT VT (5.24) This model contains four parameters, I E S , IC S , α F , and α R . From the definitions of I E S and IC S , we can obtain the important auxillary relation α F I E S = α R IC S (5.25) 288 Chapter 5 Bipolar Junction Transistors which shows that there are only three independent parameters in the Ebers-Moll model, just as in the transport formulation. The base current, given by i B = i E − i C , is vB E v BC i B = (1 − α F )I E S exp − 1 + (1 − α R )IC S exp −1 VT VT (5.26) which is equivalent to the base current expression in Eq. (5.13). 5.5.4 The Ebers-Moll Model for the pnp Transistor The equation set for the pnp transistor can be derived in a manner analogous to that of the npn device, and such an analysis yields Eq. (5.27): vE B vC B i E = I E S exp − 1 − α R IC S exp −1 VT VT vE B vC B i C = α F I E S exp − 1 − IC S exp −1 VT VT vE B vC B i B = (1 − α F )I E S exp − 1 + (1 − α R )IC S exp −1 VT VT (5.27) Note that the current and voltage polarities for the pnp transistor are all opposite those of the npn device, as originally shown in Fig. 5.6. 5.5.5 Equivalent Circuit Representations for the Ebers-Moll Models Equivalent circuit representations of the Ebers-Moll equations are useful as aids in hand analysis and have been used as the model in many circuit simulation packages. The Ebers-Moll equivalent circuits for the npn and pnp transistors are presented in Figs. 5.9(a) and 5.9(b), respectively. Diode currents i F and i R are established by the voltages v B E and v BC applied to the base-emitter and base-collector junctions, as represented by Eqs. (5.20) and (5.22), and the current-controlled current sources represent the portions of the diode currents that are transported across the base region of the devices. Exercise: What are the values of α F , α R, I E S, and I CS for the transistor in Example 5.1? Show that α F I E S = α R I CS Answers: 0.980, 0.500, 1.02 × 10−16 A, 2.00 × 10−16 A, 1.00 × 10−16 A = 1.00 × 10−16 A Exercise: Derive the Ebers-Moll equation set that describes the pnp transistor. Answer: See Eq. (5.27) 5.6 The Operating Regions of the Bipolar Transistor 289 C iC C B iC iB iR iE ICS ␣F iF IES ␣RiR iB E B iF vBE VT −1 vBC VT −1 iF = IES exp iR = ICS exp iE E (a) C iC C B iC iB iR IES ␣RiR B E iF vEB VT −1 vCB VT −1 iR = ICS exp ␣F iF iB iE iF = IES exp ICS iE E (b) Figure 5.9 Equivalent circuit models for the Ebers-Moll models for the (a) npn and (b) pnp transistors. 5.6 THE OPERATING REGIONS OF THE BIPOLAR TRANSISTOR In the bipolar transistor, each pn junction may independently be forward-biased or reverse-biased, so there are four possible regions of operation, as defined in Table 5.2. The operating point establishes the region of operation of the transistor and can be defined by any two of the four terminal voltages or currents. The characteristics of the transistor are quite different for each of the four regions of operation, and in order to simplify our circuit analysis task, we need to be able to make an educated guess as to the region of operation of the BJT. When both junctions are reverse-biased, the transistor is essentially nonconducting or cut off (cutoff region) and can be considered an open switch. If both junctions are forward-biased, the transistor is operating in the saturation region8 and appears as a closed switch. Cutoff and saturation (colored in Table 5.2) are most often used to represent the two states in binary logic circuits 8 It is important to note that the saturation region of the bipolar transistor does not correspond to the saturation region of the FET. This unfortunate use of terms is historical in nature and something we just have to accept.