Wireless ECG/EEG with the MSP430 Microcontroller

advertisement

Wireless ECG/EEG with the

MSP430 Microcontroller

Tamas Hornos

Department of Electronics and Electrical Engineering

University of Glasgow

A thesis submitted for the degree of

Master of Science

2009

I would like to dedicate this thesis to my loving parents ...

Acknowledgements

I would like to thank my first supervisor, Dr. Bernd Porr, for introducing me to the ECG signal processing techniques and for his help

with the design of the circuit’s analogue part. I would also like to acknowledge the contribution of Colin Waddell, who wrote an MSP430

wiki page which was a great help in setting up the MSPGCC toolchain

under Ubuntu GNU/Linux. I am indebted to Prof. John H. Davies,

the author of the MSP430 Microcontroller Basics book, which served

as a good starting point. He has always been available to answer my

MSP430 related questions, and provided me with his development

tools which eased the project work.

Abstract

This thesis details the design of an ultra-low power wireless EEG and

ECG monitoring device working at 868MHz frequency and capable of

short range transmission. The motivation behind the project was the

need for a small, portable and ultra-low power wireless EEG recording system that is built from commercially available electronic components, to help the research of animal behaviour and learning. There

are many implementations of portable EEG and ECG monitoring devices, but most of them were designed using special ASIC or custom

built integrated circuits. These were either never commercialised or

are far too expensive to be used in academic researches. This work is

part of a wider university project that was initiated to research the

implications of schizophrenia in brain activity. This thesis work aims

to help support the rat experiments by providing a neccessary tool

and lowering the research expenses.

The paper starts with the specifications that point out the most important respects of the hardware and software design. In the forthcoming chapters the building elements are introduced, and the choice

of microcontroller and wireless transceiver chips are discussed by highlighting their features that make them suitable for the purpose. The

main parts of the project are hardware and software design. Both

the designed schematic and layout are described, along with the significant parts of the software. Code snippets are provided to exhibit

the techniques that take advantage of the capabilities of the ultra-low

power chip architecture. Finally, tests and measurements that were

carried out to benchmark the device are presented, to show how the

whole system performs in the real, “noisy” environment.

Contents

1 Introduction

1

2 Device Specification

3

2.1

2.2

Signal Processing Considerations . . . . . . . . . . . . . . . . . .

Portability Considerations . . . . . . . . . . . . . . . . . . . . . .

3 The Microcontroller

3

5

7

3.1

The SD16 A Sigma-Delta ADC . . . . . . . . . . . . . . . . . . .

8

3.2

Low-Power Operating Modes . . . . . . . . . . . . . . . . . . . . .

10

3.3

3.4

Serial Communication Interface . . . . . . . . . . . . . . . . . . .

Packaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11

13

4 The Transceiver Chip

15

4.1

Important Features . . . . . . . . . . . . . . . . . . . . . . . . . .

15

4.2

Packaging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17

5 Hardware Design

5.1 Monitor Node . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

19

21

5.1.1

Schematic Design . . . . . . . . . . . . . . . . . . . . . . .

21

5.1.2

Layout Design . . . . . . . . . . . . . . . . . . . . . . . . .

28

Receiver Node . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

32

6 Software Design

6.1 Embedded Software . . . . . . . . . . . . . . . . . . . . . . . . . .

33

33

5.2

6.1.1

Monitor Node . . . . . . . . . . . . . . . . . . . . . . . . .

33

6.1.2

Receiver Node . . . . . . . . . . . . . . . . . . . . . . . . .

38

iv

CONTENTS

6.2

CONTENTS

Computer Side Software . . . . . . . . . . . . . . . . . . . . . . .

41

7 System Benchmark

7.1 ECG Recording . . . . . . . . . . . . . . . . . . . . . . . . . . . .

44

45

7.1.1

ECG Tracing . . . . . . . . . . . . . . . . . . . . . . . . .

46

7.1.2

Placement of ECG Leads . . . . . . . . . . . . . . . . . . .

47

7.1.3

Signal Conditioning . . . . . . . . . . . . . . . . . . . . . .

7.1.3.1 Removal of Baseline Drift . . . . . . . . . . . . .

48

48

7.1.3.2

Removal of 50Hz Hum . . . . . . . . . . . . . . .

49

Acquired Raw Data . . . . . . . . . . . . . . . . . . . . . .

50

7.1.5 Signal Post-Processing . . . . . . . . . . . . . . . . . . . .

Measured System Parameters . . . . . . . . . . . . . . . . . . . .

51

54

7.2.1

Time to Send a Packet . . . . . . . . . . . . . . . . . . . .

54

7.2.2

Time to Receive and Forward a Packet . . . . . . . . . . .

54

7.2.3

Power Consumption . . . . . . . . . . . . . . . . . . . . .

55

7.1.4

7.2

8 Future Directions, Improvements

57

9 Conclusions

59

A Appdx A

60

References

62

v

List of Figures

2.1

Comparison of A/D converters . . . . . . . . . . . . . . . . . . . .

5

3.1

3.2

Block diagram of a sigma-delta A/D converter . . . . . . . . . . .

Typical current consumption of the MSP430 . . . . . . . . . . . .

9

11

3.3

Variety of MSP430F2013 packaging . . . . . . . . . . . . . . . . .

14

4.1

4.2

Block diagram of the CC1101 . . . . . . . . . . . . . . . . . . . .

Packaging of the CC1101 . . . . . . . . . . . . . . . . . . . . . . .

16

18

5.1

Functional block diagram of an EEG/ECG recording device . . .

20

5.2

5.3

Detailed block scheme of an EEG/ECG recording device . . . . .

Schematic with highlighted blocks . . . . . . . . . . . . . . . . . .

20

22

5.4

Voltage inverter circuit . . . . . . . . . . . . . . . . . . . . . . . .

23

5.5

Input and output of the voltage inverter . . . . . . . . . . . . . .

24

5.6

5.7

Instrumentation amplifier, high-pass filter and the pull-up circuit .

Output of the instrumentation amplifier . . . . . . . . . . . . . .

27

27

5.8

Top and bottom layers of the layout . . . . . . . . . . . . . . . . .

29

5.9

Top and bottom layers separately . . . . . . . . . . . . . . . . . .

31

5.10 MSP430 Experimenter board with the modified CC1101 module .

32

6.1

Flow chart of the monitor software . . . . . . . . . . . . . . . . .

35

6.2

6.3

SD16 interrupts and RFSendPacket() function . . . . . . . . . . .

CC1101 packet format . . . . . . . . . . . . . . . . . . . . . . . .

37

38

6.4

Flow chart of the receiver software . . . . . . . . . . . . . . . . .

39

6.5

RFReceivePacket() calls in the receiver software . . . . . . . . . .

41

6.6

Flow-diagram of the serial port reader program . . . . . . . . . .

42

vi

LIST OF FIGURES

LIST OF FIGURES

6.7

Converting SD16 sample to Intel compatible 16-bit integer format

43

7.1

Monitor node on the breadboard . . . . . . . . . . . . . . . . . .

45

7.2

Normal ECG tracing . . . . . . . . . . . . . . . . . . . . . . . . .

46

7.3

7.4

Frequency spectrum of the ECG . . . . . . . . . . . . . . . . . . .

Recorded raw ECG signal in time domain . . . . . . . . . . . . .

49

50

7.5

Frequency spectrum of the raw ECG signal . . . . . . . . . . . . .

51

7.6

Amplitude and phase characteristics of the bandpass filter . . . .

52

7.7

7.8

Frequency spectrum of the filtered ECG signal . . . . . . . . . . .

Filtered ECG signal in time domain. . . . . . . . . . . . . . . . .

53

53

7.9

Return time of the RFSendPacket() function . . . . . . . . . . . .

54

7.10 Return time of the RFReceive() and BlastString() functions . . .

55

vii

Chapter 1

Introduction

Electroencephalogram recordings have traditionally been carried out using a massive recording device, connected to the patients by several leads and tying them

down to the bed or seat. These peaces of equipment were perfectly fitted to

their purpose back then and they were great examples of the state-of-the-art

biomedical electronics design. As wireless telecommunication and manufacturing

technology have rapidly advanced, small mobile electronic devices have appeared

on the market and have soon become widespread thanks to their portability and

ease of use. They have not just become part of our everyday life, but they opened

new opportunities for scientific experiments to leave the four walls of the laboratory. Wireless communication is taking over the old wired solutions in the EEG

and ECG recorders too. Brain activity monitoring is not just becoming more

convenient, but will also be possible during exercise or on freely moving subjects.

A joint project has been initiated by the medical and electronics departments in

order to monitor, record and research the brain activity (EEG, ECoG, LFP and

Single Unit Activity) of schizophrenic rats. This interdisciplinary research area

involves both electronics knowledge and deep understanding of the processes in

the brain.

The whole project is far beyond the scope of this paper, that is why I do

not discuss the physiological aspects here in details. However a minimal understanding of the human body, heart or brain models was necessary to lay down

the specifications of the built system. I am going to touch on those aspects in

a chapter to help the reader getting familiar with the topic and the challenges I

1

1. INTRODUCTION

faced during the design. The electrocardiography, — better known as ECG —

will help in doing this, as it is far more suitable for demonstration purposes, as

many of us have already seen his/her own ECG traces and are a bit familiar with

the signal curves. The choice to test the whole system by monitoring my heart

activity was influenced also by the Digital Signal Processing course lectured in

the autumn semester by my supervisor, Dr. Bernd Porr.

The system specifications start the thesis and point out the more important

respects of the hardware and software design. The forthcoming chapter introduces

the used microcontroller by highlighting the features that make it fit for the role.

Wireless communication cannot be implemented without a wireless transceiver.

The reader is provided with a short general description of the today available

transceiver chips to review their functioning and then focus on the chip of my

choice. To unfold the advantages of this chip its performance and capabilities are

compared with its ancestor. I put more emphasis on the hardware and software

design as these made up the majority of my project work. The schematic and

layout are described along with the significant parts of the software. Code snippets are provided to exhibit the techniques taking advantage of the capabilities

of the chip architecture. The following chapter about testing the ECG recording

and benchmarking the device serves as evidence that the entire system works as

expected and ready to be utilised for the rat experiments. An overview of today’s

similar EEG/ECG monitoring solutions and areas for potential future improvement are also presented before the last conclusion chapter closes the dissertation.

2

Chapter 2

Device Specification

2.1

Signal Processing Considerations

Proper EEG or ECG signal acquisition is carried out using filters for noise suppression and amplifiers to enlarge the signal amplitude as much as possible, while

keeping it within the input voltage range of the analogue-digital converter (ADC).

The task of the ADC is then to digitise the analogue voltage with a resolution

high enough to represent the original signal. In other words, the quantisation

is the process of mapping a continuous range of values by a finite set of integer

values. These values can then be collected by a microcontroller (MCU) which

maintains the connection with the wireless transmitter. It is always dependent

on the application, what we consider to be high enough voltage resolution.

In EEG and ECG measurement the biggest challenge is the elimination of the

body’s DC offset and the 50Hz1 hum, that the human body —as an antenna—

collects. An instrumentation amplifier is a type of differential amplifier, and as

such it perfectly fits this application. Its differential inputs —with very high

common-mode rejection ratio— eliminate much of the DC offset and the interference picked up from the AC mains. Often the preferred implementation of signal

amplification consists of two stages. The first differential amplifier gets rid of a

substantial part of the noise while amplifying the signal. It is then further filtered

before is fed into the second amplifier, which augments its amplitude close to the

1

It is 60Hz in the USA, and needs extra attention during the hardware or software design,

if we are to tackle both.

3

2. DEVICE SPECIFICATION

2.1 Signal Processing Considerations

input range boundaries of the ADC. When it comes to measurement, instrumentation amplifiers are often used thanks to their great accuracy and stability of

the circuit, both short- and long-term. These features make them desirable in

our monitoring device.

Once the signal is filtered and amplified, we are intent on recording with

maximum accuracy on a battery powered device. In order to achieve that, we

have to choose an A/D converter offering high resolution along with reasonable

conversion time. The sigma-delta (SD) converters1 distinctive characteristics are

high precision and relatively low speed, whereas successive-approximation-register

(SAR) analogue-to-digital converters offer sample rates up to ≈ 5 megasamples

per second with a bit less voltage resolution. Observations show that a sample

frequency2 of 1kHz is suitable and sometimes even sample rates down to 500Hz

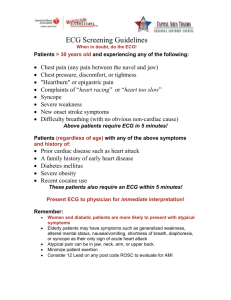

can be used. I provide the reader with a simple chart (Figure 2.1)—comparing

these two major features— that also helped making the choice in between these

three widely used A/D converters.

Here is a list summarising the features that the EEG/ECG recording device

has to have as far as the signal conditioning is concerned:

• High voltage resolution

• Moderate conversion speed

• Differential amplifier

• Two amplifiers

• High-pass filter

• Low-pass filter

1

The original name “Delta-Sigma” was coined by the inventors Inose and Yasuda in 1963,

who provided the first published description of its basic properties. Later the converse form

also became widely known and nowadays both notations are used.

2

In case of a sigma-delta converter, do not confuse it with sampling frequency or modulator

frequency, which is the rate of the output stream generated by the sigma-delta modulator, and

can be a few orders higher than that.

4

2. DEVICE SPECIFICATION

2.2 Portability Considerations

Sigma-Delta

Succ. appr.

Flash

8

16

bit resolution

24

Sigma-Delta

Succ. appr.

Flash

10

1K

100K

10M

Conversion speed (log)

Figure 2.1: Comparison of A/D converters

2.2

Portability Considerations

When looking for adequate components to use in the design, we have to keep

in mind that the final product will be secured onto the back of a rat. Average

sized rats weigh 100 to 200 grams and can easily carry 10% of their own weight.

Obviously the smaller the size, the better, but reducing the dimensions to the

possible minimum is not the primary goal of the project. However, I think when

significant size reduction can be achieved with not too much effort, it is worth

it. Unfortunately the board manufacturing and component soldering technologies

available in the departmental workshop set a lower limit to the board dimensions.

All in all, the board size is roughly equal to the dimensions of a two pence coin1

would certainly be more than satisfactory under these conditions.

The word “portability” also refers to the way the device should be powered.

It is desired to be able to function from a small single battery for at least a day to

a few days. Commercially available lithium coin batteries have capacities of 150

– 300mAh, while weighing less than 5 grams. They seem to be perfect for this

application, if we can keep the total power consumption at a low, or more ideally

1

The diameter of the coin is 25.9mm and of course I had no intention to make the board

round.

5

2. DEVICE SPECIFICATION

2.2 Portability Considerations

at an ultra low level. I did not search for an ultra-low power microcontroller and

wireless transmitter chip for too long. Most of the ultra-low power MCUs are

built on an 8-bit architecture, while the MSP430 family from Texas Instruments

(TI) offers true 16-bit architecture. There is another telling argument for the

MSP430: the MSP430F2013. It has a built in high precision 16-bit sigma-delta

ADC, which is exactly what I need, in one chip. The other important building

element is the wireless transceiver. Again, there are plenty of standalone chip

solutions on the market, but two of them seemed to do the job with surprisingly

low power consumption. One of them is the product of Nordic Semiconductor,

the other one is the CC1101, from TI. I opted for the latter, partly because there

is an extensive communication library written for it. Transmission range was not

really an issue for concern, as long as it was over 5 metres.

The following bulleted list concludes the key attributes the device should have,

regarding portability:

• Ultra low power consumption → single battery power supply

• Small size and weight

• Wireless transmission range of a few metres

• Reasonable wireless data throughput → in the order of kbps

In chapter 3 the microcontroller of my choice is introduced to the reader by

looking into the modules and features I make use of in the device.

6

Chapter 3

The Microcontroller

The MSP430 is the family name of the ultra-low power 16-bit mixed-signal RISC1

processors from Texas Instruments. The 16-bit central processing unit (CPU),

the peripherals and the flexible clock system are combined by using a Neumann2

architecture with common memory address bus and memory data bus. Both the

address and data buses are 16-bit wide, as well as the registers. They can be

used interchangeably for either data or memory addresses. This makes the microcontroller unit (MCU) simpler than any 8-bit processor with 16-bit addresses.

The MSP430 has 16 registers, and the ability to perform arithmetic directly on

values in the memory. C compilers can benefit from this and produce more compact, efficient code. Texas Instruments (2006) issued a competitive benchmarking

document that contains a comparison of the MSP430 with a range of other microcontrollers. Their performance was measured by compiling and executing the

source code of a bunch of frequently used applications.

Why does the MSP430F2013 fit this particular application? I partly touched

on the topic in chapter 2, but the features are discussed in detail in this chapter.

The chapter aims to cover only the most important hardware modules or features

1

High performance is achieved using a reduced (simplified) instruction set, that is executed

very quickly.

2

Neumann Janos (in Hungarian) (December 28, 1903 – February 8, 1957) was a Hungarian

mathematician who made major contributions to a vast range of fields, including set theory,

functional analysis, quantum mechanics, ergodic theory, continuous geometry, economics and

game theory, computer science, numerical analysis, statistics, as well as many other mathematical fields.

7

3. THE MICROCONTROLLER

3.1 The SD16 A Sigma-Delta ADC

of the microcontroller regarding the goal of the project. Davies (2008) is an extensive resource and easy to understand book introducing the MSP430. I found

it very handy for the project work. For the full documentation see the device specific user guide (Texas Instruments, 2008b) and data sheet. (Texas Instruments,

2007b)

3.1

The SD16 A Sigma-Delta ADC

The SD16 A is a single-converter 16-bit, analogue-to-digital conversion module implemented in the MSP430x20x3 series. It is made up of one sigma-delta

analogue-to-digital converter and an internal voltage reference. It has eight fully

differential multiplexed analogue input channels, of which three are internal. The

inputs to channel 7 are short-circuited together, allowing the measurement of the

system offset voltage. The operation of sigma-delta converters is totally different

from the successive-approximation ADCs. The idea behind them is to reduce the

analogue-to-digital conversion to 1 bit1 and to take samples a few order faster

than the desired sample rate to compensate for its very poor resolution. The

magnitude of the analogue input is then represented by the mean value of the

produced fast bit-stream. The average is then digitally processed to output the

samples at the specified rate. Figure 3.1 shows the architecture of a sigma-delta

converter. It can be broken down into two parts: The first with the feedback

loop is responsible for the analogue-digital conversion, while the second converts

the fast bit-stream to the desired sample rate.

The bit-rate of the first part is called modulator or oversampling frequency

(fm ). This is usually much faster than the sample rate (fs ) at the digital output.

The decimation filter is a comb type digital filter with selectable oversampling

ratios (OSR = fm /fs ) of up to 1024. The filter is also called sinc filter, because

its frequency response is alike the sinc(x) = sin(x)/x function.

The comb filter is the sigma-delta converter’s characteristic feature, which has

to be taken into account during the design stage. One may think it is a downside,

however when it comes to anti-aliasing or notch filtering, it can be utilised by

1

It is often called “the comparator”.

8

3. THE MICROCONTROLLER

subtractor

+

integrator

_

3.1 The SD16 A Sigma-Delta ADC

fm

ADC

low-pass

filter

fs

fm

decimator

analogue

input

digital

output

DAC

decimation filter

modulator

Figure 3.1: Block diagram of a sigma-delta A/D converter

sensible software design. It is described in more details in chapter 7, section 7.1.

There are other properties of the SD16 A module that needs to be mentioned

here. Its differential inputs, for instance. The ADC converts the ∆V = V+ − V−

voltage difference between a pair of inputs, rather than the voltage between a

single input and the ground. If this feature is not wanted, the V− should be tied

to ground. Sigma-delta converters often provide a programmable gain amplifier

(PGA) on their inputs, which may eliminate the need for additional external

operational-amplifier. These are plain op-amps with feedback resistors, and they

do not provide high input impedance. Their analogue input voltage range is

dependent on the actual gain setting, which can be increased up to 32 in the

SD16 A. The maximum full-scale range for Vref = 1.2V and GAINP GA = 1 is

±VF SR , where VF SR is defined by:

VF SR =

Vref /2

1.2V /2

=

= ±0.6V

GAINP GA

1

(3.1)

A side effect of the averaging applied in the digital sinc3 filter is that the

output does not react promptly to the change of the input. It needs 4 periods

of Ts to elapse, until the reliable value appears. This is called latency, and sets

probably the most severe limitation of sampling frequency when more than one

channel is used.

9

3. THE MICROCONTROLLER

3.2 Low-Power Operating Modes

The built-in 1.2V reference can be used both inside and outside the chip. It

comes in handy not only for the SD16 A, but for any external component that

needs regulated voltage source. It can supply currents up to ±1mA, but a 100nF

– 470nF stabiliser capacitor is recommended to be connected to it. There is also

the possibility to use an external reference voltage between 1.0 and 1.5V, but in a

digital or mixed circuit device it may be an additional burden on providing good

decoupling.

3.2

Low-Power Operating Modes

The MSP430 family is designed for ultra-low power applications and offers five

low-power modes, of which two are rarely utilised (Texas Instruments, 2008b).

The most important modes are: Active mode, LPM0, LPM3 and LPM4. The

comparison chart below shows the typical current consumption of each mode for

Vcc = 3V and Vcc = 2.2V , while the DCO1 is running at 1MHz and the LFXT12

at 32KHz from a crystal.

All five low-power modes are software selectable. An interrupt event can

wake up the chip from any of them, service the request, and restore back to the

low-power mode upon return from the interrupt routine. The MSP430 starts up

in Active mode with the CPU, all clocks and enabled modules being active. It

consumes ≈ 300µA at Vcc = 3V , but the current can be reduced to ≈ 200µA by

running the MCU at 1.8V, which is its lowest supply voltage. It is rational to do

so, as it lessens the current and provides longer battery capacity. The essential

features of the operating modes are listed in Table 3.1 along with the current

consumption at 1MHz DCO and 32KHz LFXT1 frequency at Vcc = 2.2V . For

supply currents at different temperatures and more details, see the device specific

data sheet.

1

Digitally controlled oscillator. One of the aims of the design of the MSP430 was to provide

a rapid clock start from low-power mode. The settle time in the MSP430F2xx family has been

reduced to ≈ 1µs. Its temperature-stability and accuracy have also improved a lot, but are still

not as good as a crystal’s.

2

Low- or high-frequency crystal oscillator. It is usually used with a low-frequency (32KHz)

watch crystal.

10

current consumption @ 1MHz [uA]

3. THE MICROCONTROLLER 3.3 Serial Communication Interface

300

315

270

225

180

135

90

45

2.2V

3.0V

200

55

32

0.1 0.1

0.9 0.7

LPM4

LPM3

17

11

LPM2

operating mode

LPM0

active

Figure 3.2: Typical current consumption of the MSP430

When the CPU is required, active mode must be used. An interrupt automatically switches the microcontroller from any low-power mode to active mode,

and returns back after the interrupt is serviced. However, sometimes it may be

desired to stay in active mode after waking from low-power mode. Probably the

most important mode is the LPM3, when only ACLK remains active. It is used

when the device must wake itself up regularly to quickly execute a series of commands before returning to “sleep” mode. The DCO then has to be started, which

takes more time, than starting from LPM0. It is around 1.1µs, which is a very

tiny interval.

3.3

Serial Communication Interface

The MSP430 family offers three types of serial communication peripherals:

• Universal Serial Interface (USI)

• Universal Serial Communication Interface (USCI)

• Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The last one has been around for a while and can even be found in older

chips. It has been superseded by the USCI modules in newer devices. The USI

11

3. THE MICROCONTROLLER 3.3 Serial Communication Interface

Table 3.1: Operating modes, current consumption, CPU and clock status

Mode

Current consumption [µA] CPU & Clock Status

CPU is active

Active

≈ 200

All clocks are active

CPU is disabled

LPM0

≈ 65

ACLK and SMCLK remain active

MCLK is disabled

CPU is disabled

MCLK and SMCLK are disabled

LPM2

≈ 22

DCO’s dc-generator remains enabled

ACLK remains active

CPU is disabled

MCLK and SMCLK are disabled

LPM3

≈ 0.7

DCOs dc-generator is disabled

ACLK remains active

CPU is disabled

MCLK and SMCLK are disabled

LPM4

≈ 0.1

DCOs dc-generator is disabled

ACLK is disabled

Crystal oscillator is stopped

peripheral is a lightweight module, included in the chosen F2013 MCU. It provides basic functionality to support synchronous communication, such as SPI or

I 2 C. Even though it is the simplest communication peripheral, it is perfectly

enough for interfacing with any device supporting the same communication standards. EEPROMs, flash memory modules, sensors, transceivers and many more

devices become easy to interface with, by exploiting the USI interface of this

microcontroller.

In its simplest form, USI is an 8- or 16-bit shift register that can be used

to output data streams, or with minimal software, can implement serial communication. USI includes additional built-in hardware functionality to ease the

12

3. THE MICROCONTROLLER

3.4 Packaging

implementation of 3-wire/4-wire SPI or I 2 C communication. The USI provides

interrupt support, which reduces the software overhead in the serial communication and maintains the low-power capabilities. Its clock generator contains a

clock selection multiplexer, a divider and the ability to select clock polarity. The

module can be utilised both as master and as slave, which further broadens its

usability.

3.4

Packaging

As electronics manufacturing technology advances, more functionality becomes

available on a single chip. Microprocessor shrinkage plays a great role in the

device miniaturisation race, as well as in the reduction of power consumption.

The MSP430 microcontrollers also follow the trend and are available only1 in

SMD (Surface Mount Device) packages. Chips with less pins come in SSOP2 ,

SOIC3 or QFN4 packages, while the big siblings are marketed mainly in QFP5 ,

QFN or BGA6 packages. The first two have their leads on two sides of the

package, while the rest have leads on all four sides. To be more precise, the

QFN and BGA packagings have contact pads instead of leads. The BGA type

has the smallest footprint among all, and can only be soldered using professional

soldering machines. Even huge manufacturing companies choose this packaging

rarely, as the optical inspection of the contacts is impossible.

The MSP430F2013 is available in three different types of packaging (Texas Instruments, 2007b): PDIP7 , TSSOP8 and QFN. Figure 3.3 illustrates all of them

with different aspect ratios. Their respective dimensions along with their package

area are listed in Table 3.2.

For comprehensive package information see Texas Instruments (2009f).

1

The only exception is the MSP430F20xx series.

Shrink Small-Outline Package

3

Small-Outline Integrated Circuit

4

Quad Flat No leads

5

Quad Flat Package

6

Ball Grid Array

7

Plastic Dual In-line Package

8

Thin-Shrink Small Outline Package

2

13

3. THE MICROCONTROLLER

3.4 Packaging

Figure 3.3: Variety of MSP430F2013 packaging

Table 3.2: Package dimensions and area

Package type

PDIP

TSSOP

QFN

Length

[mm]

Width

[mm]

19

5

4

6.3

4.4

4

Pin/Pad

width

[mm]

1.5

0.25

0.3

14

Pin/pad

distance

[mm]

2.54

0.65

0.65

Package

area

[mm2 ]

119.7

22

16

Chapter 4

The Transceiver Chip

The CC1101 is a sub-1GHz transceiver designed for low-power wireless applications. It is intended for the ISM1 and SRD2 frequency bands at 315, 433, 868,

and 915MHz, but is capable of operation at other frequencies in the 300-348MHz,

387-464MHz and 779-928MHz bands. The major modules making up the chip

are depicted in Figure 4.1.

CC1101 features a low-intermediate frequency (IF) receiver. The incoming RF

signal is amplified by the low-noise amplifier (LNA) then down-converted to the

IF3 , where it is digitised by the ADCs. Channel filtering, automatic gain control

and demodulation bit/packet synchronisation are performed digitally. Direct synthesis of the RF frequency is carried out in the transmitter part. The frequency

synthesiser includes an on-chip VCO, which is used for the down-conversion mixers in receive mode. (Texas Instruments, 2009b)

4.1

Important Features

When power consumption is a major concern, one has to keep an eye on both

the current consumption and the operating conditions. The CC1101 is able to

1

Industrial, Scientific and Medical frequency bands, that have later become popular in

unlicensed communications.

2

Short Range Device

3

Typically to the megahertz range. The technique is widely utilised in FM receivers and

mobile phones.

15

4. THE TRANSCEIVER CHIP

4.1 Important Features

Figure 4.1: Block diagram of the CC1101

function at operating supply voltages down to 1.8V, without significant changes

in its general characteristics. A few typical parameters are tabulated in Table 4.1

to illustrate the capabilities of the chip. The parameters were measured at 3V

supply voltage, with the carrier frequency set to 868MHz and at transmission

speed of 250kBaud.

The CC1101 was designed with the intention to keep the number of necessary additional components low. The transceiver chip has balanced RF input

and output, sharing two common pins. The receive- and transmit-switching is

controlled by a dedicated on-chip function. Antenna matching in both receive

and transmit modes is ensured by combining a few external passive components

with the internal termination circuitry. The external components convert the

differential RF signal at the RF N and RF P pins to a single-ended RF signal,

then an appropriate LC network matches the impedance to a 50Ω antenna. This

is the most often followed scenario. The circuitry transforming the single-ended

signal to differential is called balun1 . It makes up a crucial part of the whole

1

The name comes from the combination of the words BALanced and UNbalanced.

16

4. THE TRANSCEIVER CHIP

4.2 Packaging

Table 4.1: Characteristic numbers of the CC1101

1.8 − 3.6V

−40 − 85◦ C

Operating supply voltage

Operating temperature

Current

Current

Current

Current

consumption

consumption

consumption

consumption

in

in

in

in

power down mode

receive mode

transmit mode 0dBm

transmit mode -6dBm

≤ 165µA

≈ 16mA

≈ 16.8mA

≈ 16.4mA

−95dBm

86.5 + j43Ω

Receiver sensitivity

Differential load impedance

circuit. Fortunately some manufacturers noticed the demand for these circuits,

and marketed their integrated equivalents to help further shrinking the printed

circuit boards.

The key features of the CC1101 —regarding the EEG/ECG monitoring application—

are tabulated in Table 4.2 for the sake of readability.

4.2

Packaging

The CC1101 transceiver chip hit the market in 2007. As it is a recent model, TI

chose to manufacture it solely in the small no-lead quad-flat-pack, abbreviated

QFN. Although it is good news for those who build high quality surface mounted

boards, some of the potential customers may fall away as a result of difficulties

with soldering. The packaging dimensions are 4.1mm*4.1mm, and the height is

slightly below 1mm. It comes with contact pads at the sides of the bottom of the

package and a large ground/thermal plane in the middle. Although soldering it

by hand proved to be possible, to create proper contacts with the printed circuit

board (PCB), reflow soldering technique must be used. This technique is widely

used in manufacturing plants, where all technological steps are accomplished by

machines. Figure 4.2 depicts the outlines of the QFN packaging. (Texas Instruments, 2009b)

17

4. THE TRANSCEIVER CHIP

4.2 Packaging

Table 4.2: Analogue, digital and low-power features of the CC1101

Analogue features

Digital features

Modulation modes: 2-FSK, GFSK, MSK, OOK, ASK

Programmable data rates (from 0.8 to 500kBaud)

Programmable output power (from -30 to 10dBm)

Fast settling frequency synthesiser (90µs)

Support for packet oriented systems (separate 64-byte

RX and TX FIFOs)

Hardware support for sync word detection

Hardware support for address checking

Hardware support for CRC checking

Flexible packet length handling

4-wire SPI interface for easy configuration and FIFO

read/write

Programmable sync word length for protection against

false detection

Per-package link quality indicator

200nA sleep mode current consumption

Low-power features 240µs startup time from sleep to RX/TX

Wake-on-radio for low-power RX polling

Figure 4.2: Packaging of the CC1101

18

Chapter 5

Hardware Design

The requirements that the EEG/ECG monitoring device have to meet have been

already partly touched upon in chapter 2. That chapter served as a starting point

for the final hardware design. It is now necessary to lay down the whole spectrum

of the intended functionality of the device. In other words, the full specification

has to be defined, so that the complete block scheme can be drawn. Once the

entire system is given, and all the connections between the blocks are known, the

task can be broken down into the implementation of the separate parts. (Chen,

2008)

Figure 5.1 illustrates a functional diagram of the whole system, including the

monitor node, the receiver node and the computer. The role of the monitor

node is to acquire the samples at the specified sample rate. The receiver node is

responsible for the reception of the samples and forwarding the samples to the

computer. The digital signal post-processing and recoding is than carried out on

the more powerful PC. I intentionally pushed all the resource hungry or lengthy

operations to the computer side to lighten the load on the battery powered node.

There are some ECG applications though —such as arrhythmia monitoring or

cardiac alarm systems—, where it is necessary to pre-process the raw data real

time on the monitor side. This is not the case in “passive” monitoring, which

saves some valuable energy and CPU time.

The block scheme presented in Figure 5.2 depicts all the connections between

the different functional modules in the system. The following two sections deal

19

5. HARDWARE DESIGN

Computer

Electrodes

GUI for

visualisation

and recording

Amplifier

High-pass Filter

Serial Port

Low-pass Filter

Amplifier

A/D Converter

Serial Transmitter

Wireless

Transmitter

Wireless Receiver

Monitor node

Receiver node

Figure 5.1: Functional block diagram of an EEG/ECG recording device

with the introduction of the monitor side and the receiver side. They describe

the necessity and, objective of each block and how they are implemented.

voltage

regulator

voltage

regulator

Figure 5.2: Detailed block scheme of an EEG/ECG recording device

20

GUI

port/file handler

COMPUTER

serial port

MSP430xxx

crystal

crystal

voltage

inverter

SPI

RF circuit

balun

CC1101

balun

SPI

RF circuit

CC1101

SPI

PGA

16-bit ADC

MSP430F2013

high-pass filter

instrumentiation

amplifier

INA126

RECEIVER NODE

SPI

UART

MONITOR NODE

5. HARDWARE DESIGN

5.1

5.1 Monitor Node

Monitor Node

The monitoring subsystem received a lot attention during the design, as it is

the main part of the project. All the size and power consumption requirements

I mentioned earlier applied to this device. When it comes to hardware design,

finding the golden balance between size and functionality is not a straightforward

task, and a few iterations might be necessary to get a satisfactory solution. Only

the finalised schematic and layout are presented here, although other implementations may also be operable and adequate. Since the two major elements of the

design have already been selected (the MSP430F2013 microcontroller and the

CC1101 transceiver), the task got a bit easier. The objective was to keep the

number of additional components low, and consequently the size small.

5.1.1

Schematic Design

The first step of the hardware design (KiCAD, 2009) is to set out the hierarchy

of the elements. It is sensible to follow the hierarchical order when looking for

the way to connect them together. Obviously the two main parts stand on the

top, and the instrumentation amplifier follows them. The remaining three blocks

are the high-pass filter, the voltage regulator and the voltage inverter. All of the

blocks are circled and highlighted on the schematic in Figure 5.3.

As it has been mentioned before, the MCU and the transceiver both support

SPI communication. SPI is a master-slave type of communication, where the

master initiates the data frame. Multiple slave devices are allowed with individual

chip select line. The microcontroller’s USI peripheral supports only the 3-wire

SPI natively, while the CC1101 uses 4-wire SPI interface. This problem can be

overcome easily by utilising one of the 10 general I/O pins of the MSP430 as the

chip select line. The four lines used for the interfacing are as follows: MISO1 ,

MOSI2 , SCLK3 , CSn4 . An interrupt line is also necessary in between the two

chips, to signal to the MCU when packets have been received. But why would

1

Master In – Slave Out

Master Out – Slave In

3

Serial Clock

4

Chip Select negated

2

21

5. HARDWARE DESIGN

5.1 Monitor Node

Figure 5.3: Schematic with highlighted blocks

22

5. HARDWARE DESIGN

5.1 Monitor Node

we want to use the transceiver on the monitor node for receiving? The answer is

simple; Although it is not used yet, it can give extra features to the device later,

such as remote controlling or remote setup capability.

As for the amplifier and the voltage inverter sub-circuit, the INA126 precision

instrumentation amplifier was chosen because of its wide supply range, that allows

its operation even at ±1.35V . (Texas Instruments, 2005) Unfortunately as a

differential amplifier, it sets an extra challenge in design. Negative voltage has to

be produced for its negative supply, in order to exploit the negative (differential)

input voltage range. Commercially available charge pumps could be used for this

purpose, but they occupy too much space with their two additional capacitors.

A simpler and smaller solution would be preferred, as usual. Luckily, there is a

tiny voltage inverter circuit (Figure 5.4), that may be suitable instead.

Figure 5.4: Voltage inverter circuit

The two diodes look like half of a rectifier bridge, but they work in a different

way than the common diode bridges. When the input square-wave is high (VCC),

diode D1 conducts and charges the C13 capacitor (diode D2 blocks). As the signal

toggles low (D1 blocks), the positive side of the capacitor becomes the zero-volt

level. Since there is still charge in C13, the other side must be minus VCC 1 . In

turn, D2 starts conducting and C13 is charging C12 with a negative voltage. C12

serves as a smoothing capacitor.

The oscilloscope figure proves that a smooth -1.9V negative voltage can be

generated by feeding a ≈1KHz 2.5V (peak to peak) square-wave into the circuit.

The ripples on the output (80mV peak to peak) can be diminished by choosing

1

VCC – D1 threshold to be accurate

23

5. HARDWARE DESIGN

5.1 Monitor Node

Figure 5.5: Input and output of the voltage inverter

the capacitance of C12 to be higher. The advantages of the circuitry are its

simplicity and the fact that it can be driven with a square wave, which is easy to

generate with one of the timers of the microcontroller.

The gain of the amplifier still needs to be set to fulfil both the EEG and

ECG signal amplification requirements. To find the best fitting value, the signal

levels in section 3.2 are used in the calculations. The whole EEG voltage range

lies within ±100µV . Dividing this range up into 212 = 4096 levels would give

satisfactory voltage resolution (VR):

f ull eeg range

200µV

=

= 0.0488µV ≈ 0.05µV

(5.1)

usef

ul

bits

2

212

For conditioning reasons the signal gets amplified in two steps: in the instruVR =

mentation amplifier and in the programmable gain amplifier. This gives us the

freedom to vary their gains while leaving their product intact. The PGA in the

microcontroller offers a gain of 1 to 32 in powers of two. The gains are not particularly accurate. For instance, the 32 setting gives a real gain of 28.4 ± 1.4 in the

MSP430F2013. (Texas Instruments, 2007b) The instrumentation amplifier has

an adjustable gain between 5 and 10000, which can be set with a single external

24

5. HARDWARE DESIGN

5.1 Monitor Node

resistor. In real situations, some of the LSB bits are affected by noise, which

leads to the degradation of effective resolution of the conversion.

VR =

P GA f ull input range

2ef f ective bits ∗ GAINtotal

(5.2)

where the PGA full input range is ±500mV → 1000mV (per datasheet).

Equation 5.2 has been rearranged to give the following formula for the GAINtotal :

P GA f ull input range

(5.3)

2ef f ective bits ∗ V R

In a noise-free environment, conversion with 16 bits, desired sensitivity from

GAINtotal =

Equation 5.3:

GAINtotal =

216

1V

= 312.68 ≈ 320

∗ 0.0488µV

(5.4)

The ECG voltage range lies within ±5mV . Dividing this range up into 212 =

4096 levels would allow nice signal reconstruction. Voltage resolution (VR):

f ull ecg range

10mV

=

= 2.44µV ≈ 2.5µV

(5.5)

2usef ul bits

212

In a noise-free environment, conversion with 16 bits, desired sensitivity from

VR =

Equation 5.3:

GAINtotal =

216

1V

= 6.2536 ≈ 10

∗ 2.44µV

(5.6)

The differential low-noise instrumentation amplifier along with thoughtful layout design can suppress substantial part of the ambient noise. So I used the results

of the ideal cases to determine the gains of the amplifiers. For the EEG and ECG

monitoring gains of 320 and 10 should be used, respectively. Setting the gain of

the external amplifier to 10 and the PGA to 32, is adequate, for instance. 20 and

16 would also fit. I chose the former, since a single 16KΩ resistor is enough to

set the gain of the instrumentation amplifier.

Once the signal gets amplified, it may contain notable amount of DC component. This has to be eliminated before it is fed into the PGA. Otherwise the

second stage would amplify the DC drift as well, resulting in a signal that falls

25

5. HARDWARE DESIGN

5.1 Monitor Node

out of the input range of the analogue-digital converter. A simple first order highpass filter with a wisely chosen cut-off frequency is eligible for the task and adds

only two extra components to the circuit. The cut-off frequency should be below

the lowest frequency component of the EEG/ECG signal, which is ≈ 0.05Hz in

diagnostic mode. It is calculated with Equation 5.7. The equation confirms that

the chosen values yield the proper cut-off frequency.

fcutof f =

1

1

=

= 0.0482Hz

2π ∗ R ∗ C

2π ∗ 1M Ω ∗ 3.3µF

(5.7)

The SD16 A module of the MSP430 should be used in bipolar mode to utilise

its entire differential input voltage range: ±Vref /(2*GAIN). However in a system

with single positive voltage supply, it is only possible if the middle point of that

voltage range is pulled up from the GND by at least Vref /(2*GAIN), to keep the

signal from falling below zero. Figure 5.6 depicts the amplifier, the high pass

filter and the pull-up resistors too. Pin no. 4 supplies the 1.2V reference, which

is divided by R3 and R4. The 0.6V is connected directly to the negative input

pin of the SD16, while the positive pin is pulled up to 0.6V with an 500KΩ

resistor. This way when the input pins of the instrumentation amplifier are

shorted, both the negative and positive inputs of the channel will see 0.6V. Since

the SD16 is equipped with a differential amplifier, zero will be digitised. Input

and output signals of this sub-circuit are shown in Figure 5.7. The yellow trace

with roughly 78mV amplitude peak-to-peak is the signal going to the differential

inputs of the amplifier. The blue trace represents the amplified output signal,

which goes through the high-pass filter and is pulled up to 0.6V to give the

purple trace. Unfortunately the massive noise on the input spoils the accuracy

of the measurement, thus the ratio of the measured peak-to-peak values is not

exactly equal to the gain, which was set to 5. The effect of the pull-up resistor is

clearly visible.

The aim of having a voltage regulator in the circuit was dual. Firstly, it

provides stable +2.5V for the amplifier and ensures that the negative supply

voltage (generated using square waves from the microcontroller) stays at -1.9V.

Actually, until its absolute value is higher than 1.35V, the amplifier should work

well. Secondly, it ensures the proper functioning of the SD16 A module, which

26

5. HARDWARE DESIGN

5.1 Monitor Node

Figure 5.6: Instrumentation amplifier, high-pass filter and the pull-up circuit

Figure 5.7: Output of the instrumentation amplifier

27

5. HARDWARE DESIGN

5.1 Monitor Node

needs higher supply voltage (≥2.5V) than other peripherals in the MCU. Without

the voltage regulator, it might happen, that the CPU worked (needs minimum

1.8V), but the sigma-delta converter did not. Failures like this are annoying and

can corrupt the samples sent to the computer.

The role of the balun component has already been mentioned in chapter 4,

section 4.1. The circuit and the passives it substitutes can be found in the reference design of the CC1101 transceiver module. (Texas Instruments, 2009c)

(Texas Instruments, 2009a)

Finally, the three connection points for the programmer, the ground and the

Vcc of the battery and the two connections for the electrodes have to be added to

the circuit.

5.1.2

Layout Design

The best way to start the layout design is to search for all the elements —listed in

the bill of materials— on distributors’ website. The same components are usually

sold in different packings. It is recommended to choose components according to

their availability and the ease of soldering/surface mounting/PCB manufacturing.

I chose the “0603” case style for all the passives, as it is easier to solder than the

“0402”, but is not substantially bigger. The components and their cases are

tabulated in Table 5.1 for the sake of readability.

Once all the components are picked and the respective footprints are found

in the CAD software, the component placement and wiring can commence. This

is an intuitive part of the design, and certainly takes a few iterations before the

“close-to-optimal” solution is found. The important technological settings are

listed in Table 5.2.

The technology used for board manufacturing and soldering has to be taken

into account when choosing the above settings. In this case hand soldering and

handmade vias set the lower limit on size. If the via diameters and drills were

any smaller, they could not have been soldered by hand. The 0.3mm line width

was the narrowest that could be laid out in the departmental workshop, so I paid

attention during the design not to draw the tracks closer than that.

28

5. HARDWARE DESIGN

5.1 Monitor Node

Table 5.1: Components and their chosen case styles

Component

Case style

capacitors

resistors

dual-diode

NX3225SA

CC1101

MSP430F2013

INA126

TPS71525

0896BM15A0001

0603

0603

SOT23-3

NX

QFN

QFN

8-MSOP

SOT23-5

special

Figure 5.8: Top and bottom layers of the layout

The power lines are slightly wider than the signal lines, and they do not run

close to each other for long. There are only 45 bends in the lines, as 90 turns have

29

5. HARDWARE DESIGN

5.1 Monitor Node

Table 5.2: Technological settings

Track width

Clearance

Mask clearance

Via pad diameter

Via drill

Connector pad diameter

Connector drill

Antenna width

Copper zone clearance

Copper zone min. thickness

0.3mm

0.15mm

0.15mm

1mm

0.5mm

2mm

1mm

0.5mm

0.4mm

0.254mm

higher electromagnetic radiation. I paid attention to place the filtering capacitors

of the CC1101 as close to the chip as possible. The connection points of the

electrodes and the battery were placed at the edge of the board for convenience.

The two sided board in Figure 5.8 was designed to have ground planes as large

as possible on both sides. The plains are connected together using vias at a

few points. Although placing components on the bottom side could reduce the

board dimensions, I did not put any there for a good reason. It is best to solder

the surface mounted components using a reflow oven, which heats up the whole

board. While slightly displaced components on the top are pulled to their proper

place by the surface tension of the melted solder, components on the bottom fall

down.

The original board design used the smallest 50Ω-matched antenna solution

provided by Texas Instruments (2008a) for 868MHz communication. It consisted

of a chip antenna in conjunction with a special PCB trace. Unfortunately it

proved to be hard to obtain the component, so another solution became necessary.

A pure PCB bent monopole antenna was designed in place.

The most important attribute of a quarter-wavelength monopole antenna is

its length. It has to be calculated for the particular frequency it will be used at.

For 868MHz the length is given by the following equations:

30

5. HARDWARE DESIGN

5.1 Monitor Node

Figure 5.9: Top and bottom layers separately

c

3 ∗ 108 [m/s]

=

= 0.3456[m] = 34[cm]

f

868 ∗ 106 [1/s]

(5.8)

λg ≈ 0.75 ∗ λ0 = 0.75 ∗ 0.3456[m] = 0.2592[m]

(5.9)

λ0 =

0.2592

λg

=

= 0.0648[m] = 6.48[cm]

(5.10)

4

4

where λ0 is the wavelength in free air, λg is the approximated guided wavelength and L is the approximated physical length of the printed square-wave

L=

monopole antenna.

As the antenna is intended for short range communication, proper 50Ω matching —thus sticking to the accurate theoretical length— was not crucial. Keeping

the size low, was more important as long as the communication would be functional. The length of the antenna on the final design is 3.79cm, which is ≈ 60%

of the theoretical length. The size of the ground plane also has an effects on

the impedance. Experiments show that bigger ground plane requires a shorter

antenna.

31

5. HARDWARE DESIGN

5.2

5.2 Receiver Node

Receiver Node

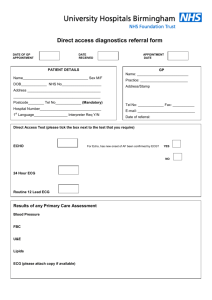

The receiver node was built up from the genuine TI MSP430FG4618/F2013 Experimenter Board (Texas Instruments, 2007a) and the modified CC1101 transceiver

module. The goal was to have a properly functioning wireless receiver equipped

with RS232 connectivity. Its USCI interface takes care of the serial communication with the computer, while the USART is responsible for interfacing with

the CC1101. Figure 5.10 shows the entire receiver subsystem, that suits these requirements. The high-end MCU on the board is far feature-richer than necessary,

the receiver side can be build from middle-class MSP430.

Figure 5.10: MSP430 Experimenter board with the modified CC1101 module

32

Chapter 6

Software Design

In this chapter the implementations of three different pieces of software is presented. All are written in the general purpose C programming language. (GCC,

2009) Two of them are embedded software, compiled for MSP430 microcontrollers, the third one runs on the most commercially successful x86 architecture.

The objective is to introduce their structure and to portray their high level code

flow models. Code snippets are provided only where necessary.

6.1

Embedded Software

Both the monitor and the receiver side programs can be broken down to two parts.

One part takes care of the wireless communication, the other part is responsible

for the rest. It is more challenging to implement the previous, that is why TI

provides an interfacing library to speed up development time. The MSP430 CC1101 library (Texas Instruments, 2009d) served as a good starting point in

code writing. Unfortunately it is a bit contrary to TI’s another application note

and contains a few bugs as well. Table 6.1 lists the low-level functions of the

library. These are used in both nodes.

6.1.1

Monitor Node

The subsystem carries out signal acquisition and 16-bit analogue-digital conversion at a specified frequency. The 16-bit integer numbers are collected in the

33

6. SOFTWARE DESIGN

6.1 Embedded Software

Table 6.1: Low-level functions utilised in both wireless endpoints

void TI

void TI

void TI

void TI

Low-level functions

char TI

void TI

char TI

void TI

CC

CC

CC

CC

CC

CC

CC

CC

SPISetup(void)

PowerupResetCCxxxx(void)

SPIWriteReg(char, char)

SPIWriteBurstReg(char, char*, char)

SPIReadReg(char)

SPIReadBurstReg(char, char *, char)

SPIReadStatus(char)

SPIStrobe(char)

meantime, then sent to the receiver in packets, to be forwarded to the computer.

The code architecture is interrupt driven to provide the most opportunities to

power down the device. The functions taking care of the SPI and thus the wireless

communication are tabulated in Table 6.2. A flow-chart of the written software

is depicted in Figure 6.1. It is a minimalistic program, that later can be easily

extended with new features.

Table 6.2: High-level functions of the monitor side software

High-level functions

void writeRFSettings(void)

void RFSendPacket(char *, char)

The program flow starts with port and peripheral initialisation. Once the

communication interface is initialised, the CC1101 is reset and configured to start

up in receive mode. The TI CC SPIWriteBurstReg() function is called to put the

predefined configuration data into the respective registers of the transceiver. The

Global Interrupt Enable (GIE) flag is set. The sigma-delta converter is then

started for one conversion on channel no. 7 to measure the offset of the PGA for

later compensation. Channel no. 4 is selected for the SD16 A before the MCU is

taken into low-power mode 3, to wait there until an interrupt is triggered.

I ought to mention that it is very important to put the microcontroller into

LPM3 mode between conversions at high frequency. The single clock that remains

34

6. SOFTWARE DESIGN

6.1 Embedded Software

MAIN()

START

ISR

Interrupt Service

Routine

(periodic wake-up)

initialise I/O ports,

peripherals, the

CC1101 and

variables

modify SR contents

on the stack, to

keep CPU awake

after return

measure offset

enter sleep mode

(LPM3)

return from

interrupt

conversion,

offset compensation

store sample

in TXbuffer

NO

Enough

samples

collected?

YES

send samples

in packet

Figure 6.1: Flow chart of the monitor software

35

6. SOFTWARE DESIGN

6.1 Embedded Software

active in that mode is the slow ACLK, —as it is seen in Table 3.1— which is not

fast enough to provide ≈ 1MHz CLK for the SD16. An external clock signal has

to be fed in to the TACLK input pin of the MSP430, to resolve this problem.

The crystal of the CC1101 is useful in this situation. Its accurate 26.000MHz

frequency can be divided down by 24 (26MHz/24 ≈ 1.083MHz), and can be

output to the GDO2 I/O pin of the transceiver chip. The highest clock frequency

the converter can operate at is ≈1.1MHz.

The SD16 A module is configured with OSR = 1024, to achieve the best resolution but the slowest conversion. Although it is relatively slow, the 1.083MHz/1024

≈ 1.058KHz sample frequency is still perfect for EEG/ECG recording. An interrupt is triggered with the mentioned frequency to return the CPU to active mode

and carry out the necessary tasks. Such as saving the content of SD16MEM0 into

a register, subtracting the earlier measured offset from it, saving the result into

the RXbuffer, checking if the buffer is full and a packet can be sent. Listing 6.1

shows the infinite loop making up the major part of the program.

Listing 6.1: Infinite loop in the monitor side software

for (;;)

{

for ( i =0; i < TX_PAYLOADSIZE /2; i ++)

{

average = 0;

for ( j =0; j < NSAMPLES ; j ++)

{

_BIS_SR ( LPM3_bits );

average += ( int16_t ) SD16MEM0 ;

}

// averaging = low pass filt

// sleep mode ( low power )

// accumulate sum

average /= NSAMPLES ;

// calculate mean

// subtract offset

result . sixteenBitReg = (( int16_t ) average ) - offset ;

txBuffer [0] = TX_PAYLOADSIZE + 1;

txBuffer [1] = DESTIN_ADDR ;

txBuffer [2* i +2] = result . twoByteReg . upperByte ;

txBuffer [2* i +3] = result . twoByteReg . lowerByte ;

36

6. SOFTWARE DESIGN

6.1 Embedded Software

}

RFSendPacket ( txBuffer , aa );

// send value over RF

}

A big advantage of the true 16-bit architecture is that the 16-bit arithmetic

on registers is both simple and fast. It is important that the enumerated tasks

have to fit into the 1/1.058KHz ≈ 945ms time-window to get finished before

the next interrupt is triggered by the peripheral. Figure 6.2 shows the time

it takes for the RFSendPacket() function to return. The 600µs was measured

with TX PAYLOADSIZE = 4, meaning that two samples were collected into one

packet, and transferred to the CC1101 for sending. The period of the squares

(≈1.900ms) confirms that the RFSendPacket() is called after two samples.

Figure 6.2: SD16 interrupts and RFSendPacket() function

The packet format utilised in the communication is portrayed in Figure 6.3.

The preamble is an alternating one-zero sequence which precedes the 4-byte sync

word. Byte synchronisation of the incoming packet is provided by the latter. The

CRC field is appended to all, while the hardware filtering makes sure that the

incoming packets failing at the CRC check get discarded and the entire RX FIFO

flushed. The horizontal arrow shows the fields included in the CRC calculation.

37

6. SOFTWARE DESIGN

6.1 Embedded Software

Listing 6.1 it is seen that the first byte of the payload indicates the size of the

data field for the receiver. Though it might seem unnecessary overhead, as the

packet size never changes, it gives high flexibility to the system, which allows easy

improvement later. The second byte contains the destination address, which is

intended for use in a wireless network. Although it is absolutely optional in this

case, it lessens the probability of false packet detection still further.

CRC calculation

preamble sync

length address

1010...10 word

field

field

(32 bits) (32 bits) (8 bits) (8 bits)

data field

(n * 8 bits)

CRC

(16 bits)

Inserted automatically in TX, processed and removed in RX

Figure 6.3: CC1101 packet format

6.1.2

Receiver Node

The receiver endpoint is built on the MSP430FG4619 MCU and the CC1101

transceiver module. It is a high-end member of the MSP430 family equipped

with 120KB Flash and 4KB RAM memory. Besides the many communication

peripherals, it features a 3 channel DMA too. The experimenters board offers

much more than is required for a wireless-RS232 gateway.

Thanks to the GDO0 output of the CC1101, packet reception is signalled to

the microcontroller to call the service routines that handle the incoming data. An

interrupt based program best fits this particular application. A power-on reset is

followed by the initialisation of the I/O ports, the peripherals and the transceiver

chip. The latter is started in receive mode, then the MCU is taken into low-power

mode 3, to wait until a received packet triggers some action. Figure 6.4 depicts

the flow-diagram of the written software. The blocks on the left side represent

the tasks carried out in the main() function, whereas the other side contains the

actions to be taken to handle the incoming samples.

High-level functions used in the receiver software are listed in Table 6.3.

38

6. SOFTWARE DESIGN

6.1 Embedded Software

MAIN()

ISR

START

initialise I/O ports,

peripherals, the

CC1101 and

variables

Interrupt Service

Routine

(externally triggered

by falling edge of

GDO0)

enter sleep mode

(LPM3)

NO

Packet

received?

store payload

in RXbuffer

NO

Enough

packets

collected?

YES

send cumulated

packets through

RS232

Figure 6.4: Flow chart of the receiver software

39

6. SOFTWARE DESIGN

6.1 Embedded Software

Table 6.3: High-level functions of the receiver side software

High-level functions

void writeRFSettings(void)

char RFReceivePacket(char *, char *)

The GDO0 output of the CC1101 is toggled low when a packet is received.

The interrupt service routine is immediately called to read in the data from the

transceiver. RFReceivePacket() function returns either the contents of the RX

FIFO, or zero, if it was a false signalling. The data fetched are collected in

the RX buffer and when enough packets are received, they are forwarded to the

serial/USB port of the computer by calling the blastString() function. Listing 6.2

shows the instructions executed in the ISR upon packet reception.

Listing 6.2: Interrupt service routine of the receiver side software

ISR ( PORT1 , port1_isr )

{

switch ( P1IFG )

{

case TI_CC_GDO0_PIN :

TI_CC_GDO0_PxIFG &= ~ TI_CC_GDO0_PIN ;

// clear flag manually

// fetch packet

if ( RFReceivePacket ( rxBuffer +( RX_PAYLOADSIZE + 1)* i ,& len ))

{

TI_CC_LED_PxOUT ^= TI_CC_LED3 ;

// toggle LED3

i ++;

if ( i == RX_PKT_NO )

{

blastString ( rxBuffer , len -1 , RX_PKT_NO );

i = 0;

}

}

break ;

default :

P1IFG = 0;

break ;

// we should never get here

// clear ISR flag register

40

6. SOFTWARE DESIGN

6.2 Computer Side Software

}

}

The serial communication proved to operate reliably at 230.4KBaud when

the CPU ran at 4MHz. Figure 6.5 portrays the periodic calls of the RFReceivePacket() with RX PKT NO = 8 setting. The function returns in 160µs

when blastString() is not called, and it takes roundabout 1520µs when 8 packets of two samples are transmitter through the RS232 port. The periodic time is

≈1.9ms, which matches the time measured on the transmitter side, and is ≈380µs

longer than the worst case interrupt return time.

Figure 6.5: RFReceivePacket() calls in the receiver software

6.2

Computer Side Software

The third program aims to collect and store the acquired samples on a GNU/Linux

operating system. (Foundation, 2009) It is designed to provide only serial port

and file handlers, while Gnuplot (Gnuplot, 2009) served as a temporary plotting

application. The code is meant to be lightweight to make its later integration

into the Comedi framework (Comedi, 2009) as easy as possible. Real time data

41

6. SOFTWARE DESIGN

6.2 Computer Side Software

plotting is out of the scope of the project work, but is highly desired. Figure 6.6

illustrates the flow-chart of the software.

MAIN()

START

closing raw-data

file

binary open

raw-data file

write reception

summary to stdio

configure modem

Enough

packets

collected?

open raw-data

file

YES

read raw-data

into buffer

NO

read in packet

from serial port

open file for

Gnuplot samples

converting 16-bit

samples to

Intel format

write buffer to file

in Gnuplot format

close file

writing raw-data

into file

STOP

Figure 6.6: Flow-diagram of the serial port reader program

The serial port handler features character oriented input processing, also

known as non-canonical. Fixed amount of bytes are read each time in asynchronous input mode. The advantage of using the read statement in this mode

is that it returns immediately with the number of characters successfully read

(without blocking the subsequent instructions). If there were no bytes read it is

zero. The definitions at the start of the file set the number of bytes expected

to arrive in a burst (PKT LEN), the number of packets to be received before

closing the connection (PKT NO) and to specify the serial/USB port the device

42

6. SOFTWARE DESIGN

6.2 Computer Side Software

is connected to.

Before any reading is started, the destination files and the port buffer are

opened. Once this has occured, packet reception commences. Packets are collected and are promptly written to the binary raw-data file until the desired

number of samples is reached. Figure 6.7 shows how the incoming 2-byte samples

are converted to an Intel compatible format. Intel conventionally regards the first

byte of a 16-bit integer as the least significant byte.

Sample from

the SD16

MSB

LSB

Intel format

(16-bit integer)

LSB

MSB

Figure 6.7: Converting SD16 sample to Intel compatible 16-bit integer format

The contents of the raw-data file are copied to a new file in a Gnuplot compatible format. Each line consists of a sample number and the actual 2-byte integer.

Gnuplot can plot the contents then without additional input arguments.

43

Chapter 7

System Benchmark

An ECG recording and various system parameter measurements were carried

out to benchmark the built device and give a picture of its capabilities at its

actual form. Since the small prototype board has not been printed out and

soldered at the time of writing, benchmarking was performed on the system

built up on a matrix breadboard. However, it has to be mentioned that, the

device is fully functional, and its circuit differs only at a few points from the

prototype the aim of the test was to show it working rather than to demonstrate

its real signal conditioning and noise suppression abilities. The breadboard itself,

through hole components, poor soldering, unoptimised and aerial wiring and the

lack of extensive ground plane all contribute to noise susceptibility. The tested

device “featured” all of these, and therefore had very poor performance in noise

diminishing.

A picture (Figure 7.1) of the measured device was taken to show its dimensions

and imperfection. The layout of the prototype can be seen next to it, in 1:1 scale.

The analogue part is the source of most problems. It contains signal and power

supply wires running side-by-side for long, noisy, through-hole capacitors and

unshielded long electrode cables, that work also as an antenna.

Being aware of the limitations of the circuit is crucial, when it comes to testing. The results always have to be assessed by taking them into account, and

treating the outcome accordingly. The upcoming sections introduce the important concepts in ECG recording to help evaluate the recorded ECG trace.

44

7. SYSTEM BENCHMARK

7.1 ECG Recording

Figure 7.1: Monitor node on the breadboard

7.1

ECG Recording

The heart is —in simple terms— the blood pump of the body made up of muscle

tissue. Its regular contraction is controlled by the sinus node which generates

the electrical stimulus every time the heart beats. This special area is located

in the right upper chamber (atrium) of the heart, and is connected to the lower

chambers (ventricles) by conduction pathways. Its generated energy travels down

and causes these lower chambers to pump out blood. A healthy person’s sine node

generates roundabout 60 – 80 heartbeats in repose.

The electrocardiogram (ECG) is a simple but crucial tool in clinical practice.

It is a non-invasive recording produced by an electro-cardiographic device, and

particularly useful in diagnosing rhythm disturbances. Electrodes are placed on

different parts of the skin over different parts of the heart to measure the electrical

activity mentioned above. An ECG displays the voltage difference between pairs

of electrodes which not only indicates the rhythm of the heart, but weaknesses

or damage in certain parts of the heart muscle. Its importance is undisputed.

The following sections of the chapter introduce a normal ECG tracing, briefly

discuss the importance of lead placement and summarise the signal conditioning

techniques.

45

7. SYSTEM BENCHMARK

7.1.1

7.1 ECG Recording

ECG Tracing

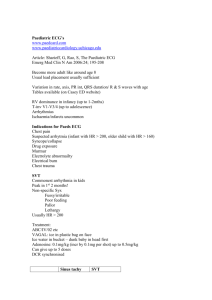

A typical ECG tracing of a normal heartbeat consists of a P wave, a QRS complex

and a T wave. (Klabunde, 2004) A small U wave is normally visible in 50 to 75%

of ECGs. The baseline voltage of the electrocardiogram is called the isoelectric

line. Figure 7.2 beneath is the schematic of a normal ECG.

QRS

Complex