UPC3250T7L

advertisement

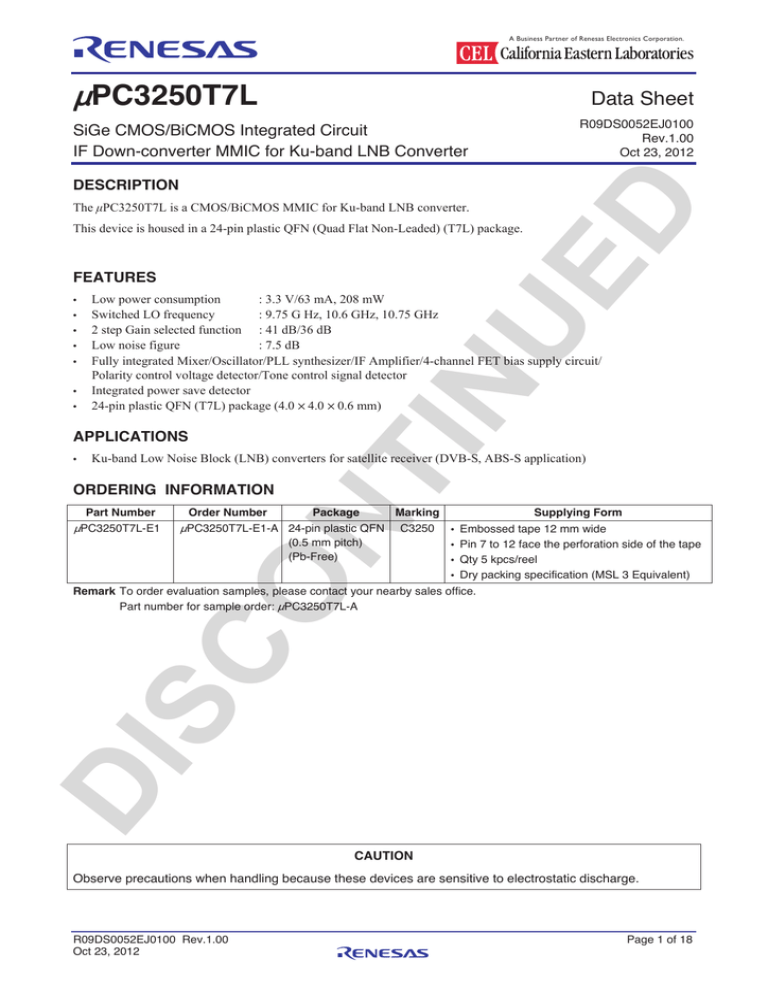

A Business Partner of Renesas Electronics Corporation. Preliminary μPC3250T7L Data Sheet R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 SiGe CMOS/BiCMOS Integrated Circuit IF Down-converter MMIC for Ku-band LNB Converter The μPC3250T7L is a CMOS/BiCMOS MMIC for Ku-band LNB converter. ED DESCRIPTION This device is housed in a 24-pin plastic QFN (Quad Flat Non-Leaded) (T7L) package. FEATURES • • Low power consumption : 3.3 V/63 mA, 208 mW Switched LO frequency : 9.75 G Hz, 10.6 GHz, 10.75 GHz 2 step Gain selected function : 41 dB/36 dB Low noise figure : 7.5 dB Fully integrated Mixer/Oscillator/PLL synthesizer/IF Amplifier/4-channel FET bias supply circuit/ Polarity control voltage detector/Tone control signal detector Integrated power save detector 24-pin plastic QFN (T7L) package (4.0 × 4.0 × 0.6 mm) IN U • • • • • APPLICATIONS Ku-band Low Noise Block (LNB) converters for satellite receiver (DVB-S, ABS-S application) NT • ORDERING INFORMATION Part Number Marking Supplying Form C3250 • Embossed tape 12 mm wide (0.5 mm pitch) • Pin 7 to 12 face the perforation side of the tape (Pb-Free) • Qty 5 kpcs/reel • Dry packing specification (MSL 3 Equivalent) Remark To order evaluation samples, please contact your nearby sales office. Part number for sample order: μPC3250T7L-A Order Number Package μPC3250T7L-E1-A 24-pin plastic QFN DI SC O μPC3250T7L-E1 CAUTION Observe precautions when handling because these devices are sensitive to electrostatic discharge. R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 1 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L PIN CONNECTIONS (Bottom View) 6 5 4 3 2 1 1 2 3 4 5 6 24 24 7 8 23 23 8 9 22 22 21 21 11 20 20 12 19 19 C3250 9 GND 10 11 12 18 17 16 15 14 13 Pin Name Pin No. Pin Name 1 NC 7 VDV 2 RFin 8 VGV 3 NC 9 VD1 4 Rcal 10 VG1 5 VDH 11 VD2 6 VGH 12 VG2 Pin No. Pin Name Pin No. Pin Name 13 GSW 19 VDDPLL 14 CVNeg 20 TonePol 15 XO2 21 IFout 16 XO1 22 VCCIF 17 Vref 23 VCCRF 18 CPout 24 LOsel NT Pin No. IN U 13 14 15 16 17 18 ED 7 10 Remark (Bottom View) Pin 1 Identifier NC means no connection pin. Heat sink of bottom side of this device is connected to GND. ABSOLUTE MAXIMUM RATINGS Symbol Ratings Unit VCCRF, VCCIF, VDDPLL +4.0 V Control Voltage (TonePol, LOsel, GSW) Power dissipationNote VPOLA, VLOsel, GSW +4.0 V Ptot 1.53 mW Storage Temperature Tstg −55 to +125 °C Operating Ambient Temperature TA −40 to +85 °C Input Power Pin 0 dBm SC O Parameter Supply Voltage Mounted on double-sided copper-clad 50 × 50 × 0.51 mm laminated PWB, TA = +85°C DI Note: R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 2 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L BLOCK DIAGRAM Top View GSW XO2 XO1 Vref 19 CVNeg 13 CPout 18 12 VG2 Tone Polarity TonePol XO Vnega PDCP Bias1 ED VDDPLL VD2 IFout VG1 Bias2 IF Amp VCCIF VD1 VCO Mix Bias3 VCCRF VGV Pre Amp LOsel Bias4 IN U Divider VDV IVref VGH VDH RFin NC 1 Rcal 7 1 pin NC 24 6 Name Description 1 NC No Connection 2 RFin Ku band RF signal input, AC coupling required. 3 NC No Connection 4 Rcal LNFET drain current adjust by resister 5 VDH Horizontal LNFET drain voltage supply 6 VGH Horizontal LNFET gate bias voltage 7 VDV Vertical LNFET drain voltage supply 8 VGV Vertical LNFET gate bias voltage 9 VD1 Common LNFET drain voltage supply 1 10 VG1 Common LNFET gate bias voltage 1 11 VD2 Common LNFET drain voltage supply 2 12 VG2 Common LNFET gate bias voltage 2 13 GSW Gain control input terminal 14 CVNeg 15 XO2 Crystal oscillator connection terminal 2 16 XO1 Crystal oscillator connection terminal 1 17 Vref Reference voltage line decoupling 18 CPout Charge pump output, connect capacitor for loop filter 19 VDDPLL PLL Power supply terminal. Decoupling capacitor required 20 TonePol Tone and Polarity control signal input terminal 21 IFout L band IF signal output, AC coupling required 22 VCCIF IF Power supply terminal. Decoupling capacitor required 23 VCCRF RF Power supply terminal. Decoupling capacitor required 24 LOsel Local Oscillator frequency control input terminal DI SC O NT Pin No. Remark Negative voltage line decoupling NC means no connection pin. Heat sink of bottom side of this device is connected to GND. R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 3 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L RECOMMENDED OPERATING RANGE (TA = +25°C, unless otherwise specified) MIN. TYP. MAX. Unit VCCRF, VCCIF, VDDPLL V_High +3.0 +3.3 +3.6 V VDD − 0.5 − VDDNote 1 V V_Low 0 − 0.5 V TA −40 +25 +85 °C RF Input frequency fRF 10.7 − 12.75 GHz IF Output frequency fIF 950 − 2 150 GHz LO frequency fLO − 9.75 − GHz Supply Voltage High level of Control Voltage (LOsel, GSW) Low level of Control Voltage (LOsel, GSW) Operating Ambient Temperature ED Symbol IN U Parameter − 10.6 − − 10.75 − 18 22 26 kHz TONE control signal frequency fTONE TONE control signal voltage VTONE 0.4 0.6 0.8 Vp-p Polarity control voltageNote 2 VPOLA 13 − 18 V 0 − VDD V 5 10 18 mA Adjustment supply current for each FET ID VDD : Supply Voltage = VCCRF = VCCIF = VDDPLL See the evaluation (application) circuit. The detail connection of pin 20 (TonePol) is shown in the evaluation circuit. This pin cannot be directly connected to 13 V/18 V polarity control voltage. The polarity control voltage must be divided to a low voltage by the external resistors. SC O Notes: 1 2 VTP NT Input Voltage of pin 20 (TonePol) ELECTRICAL CHARACTERISTICS (TA = +25°C, VCCRF = VCCIF = VDDPLL = +3.3 V, ZS = ZL = 50 Ω, fxtal = 25 MHz, unless otherwise specified) Parameter Symbol MIN. TYP. MAX. Unit VPOLA > 7.0 V , Non-RF input, GSW = +3.3 V (without FETs bias supply current) 50 63 80 mA ICC2 VPOLA > 7.0 V , Non-RF input, GSW = 0 V (without FETs bias supply current) 48.5 61.5 78.5 mA ICC3 VPOLA = 0 V ( < 3.6V) Non-RF input (without FETs bias supply current) − 5 10 mA Total Supply Current 1 (VCCRF, VCCIF, VDDPLL) Normal mode (High Gain selected) ICC1 Total Supply Current 2Note (VCCRF, VCCIF, VDDPLL) Normal mode (Low Gain selected) Total Supply Current 3Note (VCCRF, VCCIF, VDDPLL) Power Save mode DI Note Note: Test Conditions See the evaluation (application) circuit. The detail connection of pin 20 (TonePol) is shown in the evaluation circuit. This pin cannot be directly connected to 13 V/18 V polarity control voltage. The polarity control voltage must be divided to a low voltage by the external resistors. R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 4 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L ELECTRICAL CHARACTERISTICS (TA = +25°C, VCCRF = VCCIF = VDDPLL = +3.3 V, GSW = +3.3 V, ZS = ZL = 50 Ω, fxtal = 25 MHz, unless otherwise specified) Parameter Symbol Test Conditions MIN. TYP. MAX. Unit Gconv1 fLO = 9.75 GHz, fIF = 1.5 GHz, Pin = −50 dBm 37 41 45 dB Conversion Gain 2Note 1 Gconv2 fLO = 10.6 GHz, fIF = 1.5 GHz, Pin = −50 dBm 37 41 45 dB Conversion Gain 3Note 1 Gconv3 fLO = 10.75 GHz, fIF = 1.5 GHz, Pin = −50 dBm POLA control Threshold Voltage 1Note 1 Vth_POLA1 POLA control Threshold Voltage 2Note 1 (Channel selection ) TONE control signal Threshold VoltageNote 1 (Channel selection) ED Conversion Gain 1Note 1 41 45 dB Power Save mode to Normal mode Dividing resistor : 8.2 kΩ/51 kΩ 3.6 − 7.0 V Vth_POLA2 Vertical mode to Horizontal mode Dividing resistor : 8.2 kΩ/51 kΩ 15.2 15.7 16.2 V Vth_TONE Low band to High band fTONE = 22 kHz, Duty Cycle = 50%, Pulse wave Divider capacitor : 0.1 μF/0.1 μF 0.1 0.15 0.35 Vp-p IN U 37 VDH VPOLA = 18 V, ID = 10 mA, Rcal = 22 kΩ 1.8 2.0 2.2 V Drain Voltage VNote 1, 2 VDV 1.8 2.0 2.2 V Drain Voltage 1Note 1, 2 VD1 VPOLA = 13 V, ID = 10 mA, Rcal = 22 kΩ ID = 10 mA, Rcal = 22 kΩ 1.8 2.0 2.2 V Drain Voltage 2Note 1, 2 VD2 ID = 10 mA, Rcal = 22 kΩ 1.8 2.0 2.2 V IDH VPOLA = 18 V, Rcal = 22 kΩ 8.5 10 11.5 mA IDV VPOLA = 13 V, Rcal = 22 kΩ 8.5 10 11.5 mA I D1 Rcal = 22 kΩ 8.5 10 11.5 mA I D2 Rcal = 22 kΩ 8.5 10 11.5 mA VGH VPOLA = 13 V −2.0 −2.5 −3.0 V −2.0 −2.5 −3.0 V Note 1, 2 Drain Current H Drain Current VNote 1, 2 Note 1, 2 Drain Current 1 Drain Current 2Note 1, 2 Note 1, 2 SC O Gate Voltage H of FET OFF mode NT Drain Voltage HNote 1, 2 Gate Voltage VNote 1, 2 of FET OFF mode Notes: 1 VPOLA = 18 V See the evaluation (application) circuit. The detail connection of pin 20 (TonePol) is shown in the evaluation circuit. This pin cannot be directly connected to 13 V/18 V polarity control voltage. The polarity control voltage must be divided to a low voltage by the external resistors. See the graph of “Rcal vs. IDFET, VDFET.” FET’s drain current can be adjusted by the external resisters (Rcal). DI 2 VGV R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 5 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L STANDARD CHARACTERISTICS FOR REFERENCE (TA = +25°C, VCCRF = VCCIF = VDDPLL = +3.3 V, GSW = +3.3V, ZS = ZL = 50 Ω, fxtal = 25 MHz, unless otherwise specified) Symbol Test Conditions Reference Value 2.5 Unit Conversion Gain Flatness 1 ΔGconv1 fLO = 9.75 GHz, fIF = 0.95 G to 1.95 GHz, Pin = −50 dBm Conversion Gain Flatness 2 ΔGconv2 fLO = 10.6 GHz, fIF = 1.1 G to 2.15 GHz, Pin = −50 dBm 2.0 dB Conversion Gain Flatness 3 ΔGconv3 2.0 dB 7.5 dB dB ED Parameter NF1 Noise Figure 2 NF2 fLO = 10.6 GHz, fIF = 1.5 GHz 7.5 dB Noise Figure 3 NF3 fLO = 10.75 GHz, fIF = 1.5 GHz 7.5 dB Gain 1 dB Compression Output Power 1 PO(1 dB)1 fLO = 9.75 GHz, fIF = 1.5 GHz 5 dBm Gain 1 dB Compression Output Power 2 PO (1 dB)2 fLO = 10.6 GHz, fIF = 1.5 GHz 5 dBm Gain 1 dB Compression Output Power 3 Output 3rd Order Intercept Point 1 PO(1 dB)3 fLO = 10.75 GHz, fIF = 1.5 GHz 5 dBm fLO = 9.75 GHz, fIF1 = 1 500 MHz, fIF2 = 1 501 MHz 16 dBm Output 3rd Order Intercept Point 2 OIP32 fLO = 10.6 GHz, fIF1 = 1 500 MHz, fIF2 = 1 501 MHz 16 dBm Output 3rd Order Intercept Point 3 OIP33 16 dBm RF Input Return Loss RLRF fLO = 10.75 GHz, fIF1 = 1 500 MHz, fIF2 = 1 501 MHz fRF = 10.7 G to 12.75 GHz 10 dB RLIF fRF = 950 M to 2 150 MHz 10 dB PN1 1 kHz offset −78 dBc/Hz PN2 10 kHz offset −80 dBc/Hz PN3 100 kHz offset −88 dBc/Hz PN4 1 MHz offset −108 dBc/Hz Phase Noise 1 Phase Noise 2 SC O Phase Noise 3 NT IF Output Return Loss OIP31 IN U Noise Figure 1 fLO = 10.75 GHz, fIF = 0.95 G to 2.0 GHz, Pin = −50 dBm fLO = 9.75 GHz, fIF = 1.5 GHz Phase Noise 4 Integrated phase noise density Φnλ (itg) 1.7 °RMS Lo_Leakage1 Integrated offset frequency 10 k to 15 MHz fLO = 9.75 GHz, Local to RFin Local signal Leakage 1 −58 dBm Local signal Leakage 2 Lo_Leakage2 fLO = 10.6 GHz, Local to RFin −58 dBm Local signal Leakage 3 Lo_Leakage3 fLO = 10.75GHz, Local to RFin −57 dBm 2ch FET bias supplied VPOLA > 7.0 V, Non-RF 3ch FET bias supplied VPOLA > 7.0 V, Non-RF 83 mA 93 mA ICC1 Total Circuit current 2 (Reference status 2 ) ICC2 DI Total Circuit current 1 (Reference status 1) Note: See the evaluation (application) circuit. R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 6 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L STANDARD CHARACTERISTICS FOR REFERENCE (TA = +25°C, VCCRF = VCCIF = VDDPLL = +3.3 V, GSW = 0 V, ZS = ZL = 50 Ω, fxtal = 25 MHz, unless otherwise specified) Parameter Symbol Test Conditions Reference Value 36 Unit 36 dB Gconv1 fLO = 9.75 GHz, fIF = 1.5 GHz, Pin = −50 dBm dB Conversion Gain 2 Gconv2 fLO = 10.6 GHz, fIF = 1.5 GHz, Pin = −50 dBm Conversion Gain 3 Gconv3 fLO = 10.75GHz, fIF = 1.5 GHz, Pin = −50 dBm 36 dB ED Conversion Gain 1 Conversion Gain Flatness 1 ΔGconv1 fLO = 9.75 GHz, fIF = 0.95 G to 1.95 GHz, Pin = −50 dBm 2.5 dB Conversion Gain Flatness 2 ΔGconv2 fLO = 10.6 GHz, fIF = 1.1 G to 2.15 GHz, Pin = −50 dBm 2.0 dB Conversion Gain Flatness 3 ΔGconv3 2.0 dB 7.5 dB NF1 Noise Figure 2 NF2 fLO = 10.6 GHz, fIF = 1.5 GHz 7.5 dB Noise Figure 3 NF3 fLO = 10.75 GHz, fIF = 1.5 GHz 7.5 dB Gain 1 dB Compression Output Power 1 PO(1 dB)1 fLO = 9.75 GHz, fIF = 1.5 GHz 2 dBm Gain 1 dB Compression Output Power 2 PO(1 dB)2 fLO = 10.6 GHz, fIF = 1.5 GHz 2 dBm fLO = 10.75 GHz, fIF = 1.5 GHz 2 dBm NT IN U Noise Figure 1 fLO = 10.75 GHz, fIF = 0.95 G to 2.0 GHz, Pin = −50 dBm fLO = 9.75 GHz, fIF = 1.5 GHz Gain 1 dB Compression Output Power 3 Output 3rd Order Intercept Point 1 PO(1 dB)3 OIP31 fLO = 9.75 GHz, fIF1 = 1 500 MHz, fIF2 = 1 501 MHz 12 dBm Output 3rd Order Intercept Point 2 OIP32 fLO = 10.6 GHz, fIF1 = 1 500 MHz, fIF2 = 1 501 MHz 12 dBm Output 3rd Order Intercept Point 3 OIP33 12 dBm 10 dB 10 dB RLRF IF Output Return Loss RLIF fRF = 950 M to 2 150 MHz SC O RF Input Return Loss fLO = 10.75 GHz, fIF1 = 1 500 MHz, fIF2 = 1 501 MHz fRF = 10.7 G to 12.75 GHz See the evaluation (application) circuit. DI Note: R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 7 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L TRUTH TABLE Local Oscillator frequency select pin function description (pin 24 (LOsel)) LOsel LOsel = Low (DVB-S mode) Tone signal = 0 kHz Tone signal = 22 kHz Local Oscillator frequency 10.6 GHz 10.75 GHz The relationships between the LOsel state and the pin connection are as follows. ED Note: 9.75 GHz LOsel = High (ABS-S mode) − By connecting this pin to GND line (0 V DC), LOsel becomes “Low” state. By connecting this pin to VDD line (VDD DC), LOsel becomes “High” state. The VDD described above means the power supply voltage. Its value is 3.3 V the same as VCCRF, VCCIF, and VDDPLL. FET’s DC bias control pin function description (pin 20 (TonePol), polarity control voltage) VPOLA Horizontal FET Vertical FET VGH VDH VGV Common FET 1 Common FET 2 VDV VG1 VD1 VG2 VD2 Controlled (≈ 2 V) IN U FETs Normal VPOLA C o n t rol l e d Controlled Disable Disable Controlled Controlled Controlled mode > 16.2 V (−2.5 V to +1 V) (≈ 2 V) (−2.5V) (0 V) (−2.5 V to +1 V) (≈ 2 V) (−2.5 V to +1 V) VPOLA Disable Disable Controlled Controlled Controlled Controlled Controlled < 15.2 V (−2.5 V) (0 V) (−2.5 V to +1 V) (≈ 2 V) (−2.5 V to +1 V) (≈ 2 V) (−2.5 V to +1 V) Controlled (≈ 2 V) Disable Controlled Controlled Controlled Controlled Controlled Controlled Note Power VPOLA Disable Save < 3.6 V (−2.5 V) mode (0 V) (−2.5 V to +1 V) (≈ 2 V) (−2.5 V to +1 V) (≈ 2 V) (−2.5 V to +1 V) (≈ 2 V) Dividing Resistor: 8.2 kΩ/51 kΩ See the evaluation (application) circuit. The detail connection of pin 20 (TonePol) is shown in the evaluation circuit. This pin cannot be directly connected to 13 V/18 V polarity control voltage. The polarity control voltage must be divided to a low voltage. DI SC O Note: Note NT Note R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 8 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L TYPICAL CHARACTERISTICS (TA = +25°C, unless otherwise specified) IF frequency vs. Conversion Gain 18 2.4 ID FET 16 2.3 14 2.2 VD FET 12 2.1 10 2.0 8 1.9 6 1.8 4 1.7 2 1.6 25 50 100 75 IF frequency vs. Conversion Gain High Gain mode Low Gain mode 30 LowBand_HighGain HighBand_HighGain ABS-S_HighGain LowBand_LowGain HighBand_LowGain ABS-S_LowGain 20 0 500 Conversion Gain Gconv (dB) LowBand_HighGain HighBand_HighGain ABS-S_HighGain LowBand_LowGain HighBand_LowGain ABS-S_LowGain 25 500 1 000 1 500 2 000 2 500 3 000 TA= +85°C 40 35 Low Gain mode LowBand_HighGain HighBand_HighGain ABS-S_HighGain LowBand_LowGain HighBand_LowGain ABS-S_LowGain 30 25 SC O 0 2 000 IF frequency vs. Conversion Gain Low Gain mode 30 1 500 High Gain mode 40 35 1 000 IF frequency fIF (MHz) NT Conversion Gain Gconv (dB) TA = +25°C 20 35 45 45 High Gain mode 40 25 1.5 125 Rcal (kΩ) Adjustment Resistor of Drain Current of Low Noise FET TA = −40°C IN U 0 45 ED 2.5 Conversion Gain Gconv (dB) 20 VD FET (V) Drain Voltage of Low Noise FET Drain Current of Low Noise FET ID FET (mA) Rcal vs. ID FET, VD FET 2 500 3 000 IF frequency fIF (MHz) 20 0 500 1 000 1 500 2 000 2 500 3 000 IF frequency fIF (MHz) DI Remark The graphs indicate nominal characteristics. R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 9 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L FREQUENCY VS. NOISE FIGURE FREQUENCY VS. NOISE FIGURE 15 15 TA = +25˚C 13 HighBand_HighGain 12 11 ABS-S_LowGain ABS-S_HighGain 9 8 ABS-S_LowGain 11 HighBand_LowGain 10 HighBand_HighGain 9 LowBand_HighGain LowBand_LowGain 8 7 7 LowBand_HighGain LowBand_LowGain 6 5 ABS-S_HighGain 12 6 5 0.0 0.5 1.0 2.0 1.5 2.5 3.0 3.5 0.0 FREQUENCY VS. NOISE FIGURE TA = +85˚C ABS-S_HighGain ABS-S_LowGain 12 HighBand_LowGain HighBand_HighGain 11 10 9 8 2.0 2.5 3.0 3.5 LowBand_HighGain LowBand_LowGain 7 6 5 1.5 NT Noise Figure NF (dB) 13 1.0 IF frequency fIF (GHz) 15 14 0.5 IN U IF frequency fIF (GHz) ED HighBand_LowGain Noise Figure NF (dB) Noise Figure NF (dB) 13 10 TA= −40˚C 14 14 0.0 0.5 1.0 1.5 2.0 2.5 3.0 3.5 SC O IF frequency fIF (GHz) DI Remark The graphs indicate nominal characteristics. R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 10 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L EVALUATION CIRCUIT For example, Polarity control voltage is VPOLA = +13 V and +18 V, VTP is divided to a low voltage, +1.8 V and +2.5 V, respectively, by the resistors (8.2 kΩ, 51 kΩ). Polar VCC (3.3 V) IFout Tone 8.2 kΩ 10 μF 0.1 μF VDDPLL TonePol IFOUT VCCIF VCCRF LOsel 1 pin 220 nF 18 CPout RFin 1 μF Vref GND (Top View) NC Rcal XO1 15 pF AT-41CD2 (fxtal = 25 MHz) XO2 15 pF 22 kΩ For example, Rcal = 22 kΩ, ID = 10 mA is set. VDH CVNeg 0.1 μF 1 nF 12 51 Ω 10 Ω 51 Ω 10 Ω 1 nF 0.1 μF 51 Ω 1 nF 10 Ω 1 μF 0.1 μF NT 51 Ω 10 Ω 7 GSW 13 VG2 VD2 VD1 VGV 6 VG1 0.1 μF 1 nF GSW VGH VDV 1 nF 220 Ω 390 pF IN U NC RFin VDDPLL (3.3 V) 19 24 1 ED 100 pF 47 Ω 0.1 μF 47 nH 1 μF 100 pF LOsel 51 kΩ Vertical FET Common FET1 1 μF 1 μF SC O 1 μF Horizontal FET Common FET2 DI Remark NC means Non-Connection. Heat sink (bottom side of the device) is connected to GND. Board material is RO4003C (Rogers, t = 0.508 mm). R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 11 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L APPLICATION CIRCUIT ED 100 pF TonePol 47 nH IN U 30 Ω VDDPLL 1 nF CVNeg XO2 XO1 VG2 VD2 GND (Top View) NT IFout Vref CPout 56 Ω 1 μF 390 pF 220 Ω 220 nF 10 μF 0.1 μF 1 μF 100 pF GSW 47 Ω 0.1 μF 8.2 kΩ 5V 51 kΩ OUT GND 78M05 IN IFout FOR SINGLE LNB (REFERENCE ONLY) VG1 VCCIF VD1 VCCRF VGV LOsel VDV VGH VDH Rcal NC 22 kΩ BPF SC O NC RFin 1 pin 1 nF 0.1 μF 0.1 μF 1 nF R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Horizontal 1 nF Vertical DI 0.1 μF Page 12 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L IFout1 IFout2 FOR TWIN LNB (DOUBLE SINGLE LNB) (REFERENCE ONLY) 220 Ω 1 nF 1 nF CVNeg VGV LOsel VDV 0.1 μF VGH VDH NC NC Rcal 1 pin BPF 0.1 μF 0.1 μF 1 nF 1 nF 100 Ω 100 Ω 0.1 μF 1 nF DI XO2 XO1 Vref CPout VCCRF 0.1 μF 1 nF 0.1 μF 0.1 μF 1 nF Horizontal 1 nF Vertical R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 GSW 1 nF 1 μF 220 nF 10 μF 390 pF VD1 VGH VDH Rcal NC 0.1 μF VG1 VCCIF 22 kΩ RFin SC O BPF 100 pF VD2 22 kΩ VDV 1 μF RFin VGV LOsel VG2 GND (Top View) IFout NT VCCRF NC VDDPLL 47 nH VG1 VD1 1 pin 0.1 μF TonePol VD2 GND (Top View) VCCIF 100 pF IN U TonePol IFout ED 47 Ω 51 kΩ 8.2 kΩ VG2 47 nH 1 μF 30 Ω GSW CVNeg XO1 XO2 1 nF 1 μF Vref CPout VDDPLL 0.1 μF 0.1 μF 220 Ω 390 pF 220 nF 10 μF 0.1 μF 8.2 kΩ 51 kΩ 100 pF IN OUT 5V 5V 30 Ω GND 78M05 100 pF OUT 47 Ω GND 78M05 IN 12 Ω 1 nF Page 13 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L MOUNTING PAD LAYOUT DIMENSIONS 24-PIN PLASTIC QFN (T7L) PACKAGE (4.0 × 4.0 × 0.6 mm) (UNIT : mm) 2.15 2.15 1.65 1.65 1.35 ED IN U 1.35 1.65 2.15 0.25 1.35 2.15 1.65 0.5 pitch 1.35 24-0.2 DI SC O NT 0.25 R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 14 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L PACKAGE DIMENSIONS 24-PIN PLASTIC QFN (T7L) PACKAGE (4.0 × 4.0 × 0.6 mm) (UNIT : mm) (Top View) (Side View) 4.0±0.1 NT IN U 4.0±0.1 ED 0.57+0.03 −0.05 (Bottom View) DI 0.35±0.075 0.08 MIN. A 2.7±0.1 2.7±0.1 (Dimensions of Each Pin Part) A SC O (C0.2) 0.2+0.07 −0.05 Pin1 Remark A > 0 0.5±0.1 R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 15 of 18 A Business Partner of Renesas Electronics Corporation. μPC3250T7L RECOMMENDED SOLDERING CONDITIONS This product should be soldered and mounted under the following recommended conditions. For soldering methods and conditions other than those recommended below, contact your nearby sales office. Soldering Method Soldering Conditions Condition Symbol Peak temperature (package surface temperature) Time at peak temperature Time at temperature of 220°C or higher Preheating time at 120 to 180°C Maximum number of reflow processes Maximum chlorine content of rosin flux (% mass) : 260°C or below : 10 seconds or less : 60 seconds or less : 120±30 seconds : 3 times : 0.2% (Wt.) or below IR260 Partial Heating Peak temperature (package surface temperature) : 350°C or below Soldering time (per side of device) : 3 seconds or less Maximum chlorine content of rosin flux (% mass) : 0.2% (Wt.) or below HS350 CAUTION ED Infrared Reflow DI SC O NT IN U Do not use different soldering methods together (except for partial heating). R09DS0052EJ0100 Rev.1.00 Oct 23, 2012 Page 16 of 18 μPC3250T7L Data Sheet Revision History Date 1.00 Oct 23, 2012 Page − Description Summary First edition issued DI SC O NT IN U ED Rev. All trademarks and registered trademarks are the property of their respective owners. C-1