Diode Details Physical Representation Abrupt junction between p

advertisement

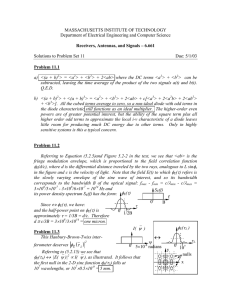

Diode Details Advanced VLSI Design CMPE 640 Physical Representation p n SiO2 acceptor (boron) holes donor (phosphorus) electrons Abrupt junction between p and n materials creates a concentration gradient among the carriers. Electrons diffuse from n to p while holes diffuse from p to n. The diffusion leaves behind bound charge in the lattice. The bound charge sets up an electric field that counteracts the diffusion. Electrons drift from p to n while holes drift from n to p. 1 Diode Details Advanced VLSI Design CMPE 640 Charge Distribution, Electric Field and Electrostatic Potential Hole diffusion Electron diffusion plate p neutral region p region more heavily doped, NA>ND - - + + + - - + + n neutral region Electron drift Hole drift + Distance Charge Density Electric Field Distance Distance plate φ0 Potential 2 Diode Details Advanced VLSI Design CMPE 640 Built-In Potential and I-V Characteristics Build-in potential: NA ND φ 0 = φ T ln ----------------2 ni kT where φ T = ------- = 26mV at 300K (Thermal V) q 10 3 n i = 1.5 ×10 carriers /cm For example: N A = 10 N D = 10 15 16 carriers /cm carriers /cm 3 3 15 16 10 10 φ 0 = 26 ln -------------------------- = 638mV 20 2.25 ×10 Forward bias Raising potential of the p w.r.t n causes current to flow from p to n. Lowers potential barrier and diffusion dominates drift. Minority carriers injected into neutral region and diffuse toward plates. Recombine with majority carrier causing a net flow of current. 3 Diode Details Advanced VLSI Design CMPE 640 I-V Characteristics Reverse bias Raising potential of the n w.r.t p causes current to flow from n to p. Drift dominates diffusion. However, current is small since the number of minority carriers (e.g., electrons in p neutral region) is small. 1.5 100 1.0 10-5 ID(A) ID(mA) For forward bias, the current is exponentially related to applied bias. 0.5 Small deviation due to recombination in depletion region. 10-10 0.5 VD 1.0 2.3φTV/decade 10-15 0.0 0.2 0.4 0.6 0.8 VD Linear scale Log scale Current increases by a factor of 10 for every 60mV (2.3fT) of forward bias. 4 Diode Details Advanced VLSI Design CMPE 640 Static Behavior Ideal diode equation: VD ⁄ φT ⎛ ID = IS e − 1⎞ ⎝ ⎠ where IS is a constant: saturation current. With VD << 0, ID ~= -IS = 10-17A/um2 (actual values are 103 higher) np(x) pn0 np0 -Wp p-region -W1 0 W2 n-region Wn Metal contact to n region pn(x) pn(W2) Metal contact to p region Forward Bias: Physical basis for ideal equation: Minority carrier concentration x 5 Diode Details Advanced VLSI Design CMPE 640 Static Behavior Reverse Bias Ideal diode equation predicts diode current approaches the saturation current as VD gets much smaller than the thermal voltage. I D → − I S for VD > φT pn0 np0 pn(x) np(x) -Wp p-region -W1 0 W2 n-region Wn Metal contact to n region Metal contact to p region Concentration of minority carriers at depletion-region approaches 0 under sufficient reverse bias. Minority carrier concentration x 6 Diode Details Advanced VLSI Design CMPE 640 Static Behavior Simple models of the diode. Left model based on ideal diode but is strongly non-linear and approximated by a simple model on the right. ID = IS ⎛ e ⎝ + VD ⁄ φT − 1⎞ ⎠ + VD VD First order approx. Ideal diode model - ID + - VDon For a fully conducting diode, voltage drop across diode is ~0.7V Example: Assume VS = 3V and RS = 10kW and IS = 0.5X10-16. ID VS + - RS VD Using non-linear model yields: VD =0.757V and ID =0.224mA Assuming VD =0.7V yields ID =0.23mA 7 Advanced VLSI Design Diode Details CMPE 640 Dynamic Behavior Dynamic behavior determines the maximum operational frequency. It is dependent on how fast charge can be moved around. Two capacitances Depletion and diffusion. Depletion region and Junction capacitance: Under the ideal model, the depletion region is void of mobile carriers. Its charge is determined by the immobile donor and acceptor ions. Intuitively: Forward bias: Potential barrier is reduced which means that less space charge is needed to produce the potential difference. This corresponds to a reduced depletion-region width. Reverse bias: Potential barrier increased, increase in space charge, wider depletion width. 8 Diode Details Advanced VLSI Design CMPE 640 Dynamic Behavior Expressions that convey this fact. Depletion region charge (VD is positive for forward bias): ⎛ NA ND ⎞ Q j = A D 2ε si q ⎜ -----------------------⎟ ( φ 0 − V D ) ⎝ N A + N D⎠ (1) Depletion-region width: Wj = W2 − W1 = ⎛ 2ε si N A + N D⎞ ⎜ ---------- -----------------------⎟ ( φ 0 − V D ) ⎝ q NA ND ⎠ (2) Maximum electric field: Ej = ⎛ 2q N A N D ⎞ ⎜ ------- -----------------------⎟ ( φ 0 − V D ) ⎝ ε si N A + N D⎠ where ε si = 11.7 × 1.053 ×10 − 12 F/cm The ratio of the n-side versus p-side depletion region width is determined by the doping level ratios: NA W2 ----------------- = -------ND − W1 9 Diode Details Advanced VLSI Design CMPE 640 Dynamic Behavior The model (for an abrupt junction): Imagine the depletion region as the dielectric of a capacitor with dielectric constant of silicon. And the n- and p-neutral regions act as the capacitor plates: plate p neutral region - - + + + - - + + n neutral region plate insulator Forward bias, cap increases Reverse bias, cap decreases A small change in the voltage applied to the junction (dVD) causes a change in the space charge (dQj). 10 Diode Details Advanced VLSI Design CMPE 640 Dynamic Behavior Depletion layer capacitance: Junction capacitance is easily computed by taking the derivative of equation (1) with respect to VD. For an abrupt junction: ε si q N A N D C j0 dQ j −1 = -------------------------------C j = ----------- = A D ---------- ----------------------- ( φ 0 − V D ) 2 NA + ND dV D 1 − VD ⁄ φ0 Cj0 is the capacitance under zero-bias conditions and is only a function of the physical parameters of the device: ε si q N A N D −1 C j0 = A D ---------- ----------------------- φ 0 2 NA + ND The same result can be obtained using the standard parallel-plate capacitor equation: ⎛ A D⎞ C j = ε si ⎜ --------⎟ ⎝ Wj ⎠ where Wj is given by equation (2). 11 Diode Details Advanced VLSI Design CMPE 640 Dynamic Behavior Junction capacitance plotted as a function of applied voltage bias: Cj (fF)/um2 2.0 1.5 Linear junction m = 0.33 1.0 0.5 0.0 Strongly non-linear Abrupt junction m = 0.5 Cj0 -2.0 0.0 VD Capacitance decreases with an increasing reverse bias. For -5V, the cap. is reduced by more than a factor of 2 over the zero bias case.: C j0 = -4.0 2 ×10 A D = 0.5 um φ 0 = 0.64V −3 2 F/m 2 then a reverse bias of -2.5V yields ⎛ 0.9 fF ⁄ um 2⎞ ⎛ 0.5 um 2⎞ = 0.45 fF ⎝ ⎠⎝ ⎠ 12 Diode Details Advanced VLSI Design CMPE 640 Dynamic Behavior For the general case: C j0 C j = ------------------------------------m ( 1 − VD ⁄ φ0 ) Where m is the grading coefficient. For an abrupt junction, m = 1/2. For a linearly graded junction, m = 1/3 (see previous figure). For digital circuits, operating voltages tend to move rapidly over wide ranges. In these cases, we can replace the voltage-dependent, nonlinear capacitance Cj with an equivalent, linear capacitance Ceq. Q j ( V high ) − Q j ( V low ) ∆Q j C eq = ------------ = ---------------------------------------------------------- = K eq C j0 ∆V D V high − V low m − φ0 K eq = --------------------------------------------------------------- ( φ 0 − V high ) ( V high − V low ) ( 1 − m ) 1−m − ( φ 0 − V low ) 1−m 13 Advanced VLSI Design Diode Details CMPE 640 Dynamic Behavior For example: Compute the average junction capacitance if this diode is switched between 0 and -5V. C j0 = 0.5fF ⁄ um 2 A D = 12um φ 0 = 0.64V 2 m = 0.5 1 − 0.5 1 − 0.5 − 0.64 0.5 ---------------------------------------------------( 0.64 − 0 ) − ( 0.64 − ( − 5 ) ) = 0.502 K eq = 0 − ( − 5 V ) ( 1 − 0.5 ) AverageC j = 0.502 × 0.5fF/um 2 fF = 0.25 ----------um 2 14 Diode Details Advanced VLSI Design CMPE 640 Secondary Effects Actual diode current is less than what is predicted by the ideal eq. Not all of the applied bias voltage falls across the junction, some falls across the neutral regions. However, the resistivity of the neutral regions is generally small (1 to 100 Ohms). This is usually modeled with a series resistance at the contacts. Avalanche breakdown (MOS and bipolar processes): Increased reverse bias increases electric field across the junction to Ecrit. Breakdown voltage ID(A) 0.1 -0.1 -25 Electron-hole pairs are created on collision with immobile silicon atoms. -15 -5 VD(V) 0 5 Non-destructive but increases power consumption 15 Advanced VLSI Design Diode Details CMPE 640 Secondary Effects Operating temperature effects The thermal voltage is linearly dependent upon temperature (increasing fT causes the current to drop). kT φ T = ------q VD ⁄ φT ⎛ − 1⎞ ID = IS e ⎝ ⎠ The thermal equilibrium carrier concentrations increase with increasing temperature causing IS to increase. Experimentally, the reverse current doubles every 8 degrees C. These have a dramatic effect on the operation of the circuit. Current levels can increase substantially (~2X every 12 degrees C). The increase in leakage current through reverse-biased diodes decreases isolation quality. 16 Diode Details Advanced VLSI Design CMPE 640 SPICE Models The preceding discussion presented a model for manual analysis. If second-order effects or more accuracy (better model) is desired, simulation is required. The standard SPICE model: VD ⁄ nφT ⎛ ID = IS e − 1⎞ ⎝ ⎠ RS + VD Extra parameter n is called the emission coefficient ID CD It is equal to 1 for most diodes. - RS models the series resistance of the neutral regions (reducing current). 17 Diode Details Advanced VLSI Design CMPE 640 SPICE Models The dynamic behavior is modeled by the nonlinear capacitance CD. Two different charge storage effects are combined in the diode: excess minority carrier charge (not discussed, forward bias only) depletion-region charge τ T I s V D ⁄ nφ C j0 T C D = ----------- e + --------------------------------------where: τ T = transit time φT m ( 1 − VD ⁄ φ0 ) Table 1: First-order SPICE diode model parameters Parameter name Saturation Current Emission Coefficient Series Resistance Transit Time Zero-bias Junction Cap Grading Coefficient Junction Potential Symbol IS n RS τT Cj0 m φ0 SPICE Name IS N RS TT CJ0 M VJ Units A Ω s F V Default Value 1.0E-14 1 0 0 0 0.5 1 18