Experiment 10 Arbitrary Waveform Generator

advertisement

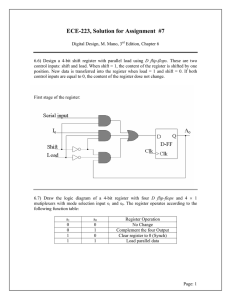

ESc 201A: Introduction to Electronics 2014-15 II Semester Department of Electrical Engineering Indian Institute of Technology Kanpur Experiment 10 Arbitrary Waveform Generator 1 Introduction In this experiment, we will design a staircase sawtooth and staircase triangular wave generators using a 3-bit counter. For this experiment, we will be using AND, OR, XOR gates and JK flip flops. Unlike experiment 9, here we will check the output of the counter on the oscilloscope instead of a 7-segment display. For this, we will use an R-2R ladder as digital-to-analog converter (DAC) that converts the digital output of the counter into an analog signal. Note: Through all stages of the experiment, remember to choose DC coupling for both scope channels. 1.1 R-2R ladder (DAC) The R-2R ladder is shown in Fig. 1a. In the figure, Q2Q1Q0 are the inputs (outputs of the counter) of DAC and vD is the output. As the count of the counter progresses through k = Q2Q1Q0, the DAC produces a correspondingly increasing analog voltage, given by vD = Where, is called the step size, and the 3-bit input k can take values 0, 1, ….., 7. As the count cycles through the 8 states repeatedly, this results in the typical staircase waveform shown in Fig. 1b. 2 Staircase sawtooth wave generator First, we will design a staircase sawtooth wave generator using a 3-bit counter with the help of J-K flip-flops. Figure 1 1. Connect the flip-flops as shown in the Fig. 2. Make the SET pins to logic 1 and CLEAR pin of all flip-flops to logic 0 initially. 2. Give 1 KHZ clock to the clk input of first flip-flop. 3. The XOR gate is used to invert the output Q of each flip-flop. When logic 0 (down) is selected, the XOR gives Q as the output, which acts as clock input to the next flip-flop and the counter acts as a down counter. Whereas, logic 1 (up) inverts the XOR output to Q and this makes the counter an UP counter. 4. After making the circuit, now switch the SET pin of all flip-flops to logic 0. 5. Connect the R-2R ladder at the output of the counter i.e. at Q2Q1Q0. 6. Connect the channel 1 of the CRO to the clock input at the first flip-flop and channel 2 to the output vD of the ladder and compare both waveforms (input and waveforms shown in Figs. 1b and 1c). 0 – DOWN 1 - UP 1 J SET Q J SET Q J K CLR Q K CLR Q K SET Q CLK CLR Q LSB Figure 2: 3-bit staircase sawtooth waveform generator 3 Staircase triangular waveform generator Figure 3: 3-bit staircase triangular waveform Connect the flip-flops as shown in the Fig. 4. Make the SET pins to logic 1 and CLEAR pins of all flip-flops to logic 0 initially. 2. Give 1 KHZ clock directly to the clk input of all the flip-flops except the first one. 3. After making the circuit, now switch the SET pin of all flip-flops to logic 0. 4. Connect the R-2R ladder at the output of the counter i.e. at Q2Q1Q0. 5. Connect the channel 1 of the CRO to the clock input at the first flip-flop and channel 2 to the output vD of the ladder and compare both waveforms (as shown in Fig. 3). 1. 2 CLK 1 1 J SET Q J SET Q J SET Q J SET Q K CLR Q K CLR Q K CLR Q K CLR Q MSB Figure 4: 3-bit staircase triangular waveform generator In the course, generating different kinds of sequences using a cascade of flip-flops has been taught. Taking that into account, you can generate any kind of sequence by using different kinds of logic gates. 3