Doherty`s Legacy

advertisement

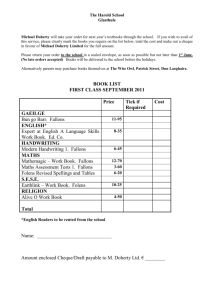

COV ER FE ATURE Doherty’s Legacy Raymond Pengelly, Christian Fager, and Mustafa Özen William H. Doherty W illiam H. Doherty was an American electrical engineer, best known for his invention of the Doherty amplifier. Born in Cambridge, Massachusetts, in 1907, Doherty attended Harvard University, where he received his bachelor’s degree in communication engineering (1927) and his master’s degree in engineering (1928). He then joined the American Telegraph and Telephone Company Long Lines Department in Boston. He remained there for a few image licensed by graphic stock Raymond Pengelly (raypengelly@gmail.com) is with Prism Consulting NC, Hillsborough, North Carolina, United States. Christian Fager (christian.fager@chalmers.se ) and Mustafa Özen (mustafa.ozen@chalmers.se) are with Chalmers University of Technology, Gothenburg, Sweden. Digital Object Identifier 10.1109/MMM.2015.2498081 Date of publication: 14 January 2016 February 2016 1527-3342/16©2016IEEE 41 In Doherty’s day, within the Western Electric product line, this “namesake” electronic device was operated as a linear amplifier with a driver that was modulated. months before joining the National Bureau of Standards, where he researched radio phenomena. Doherty joined Bell Telephone Laboratories (now Bell Labs) in 1929 and, while there, worked on the development of high power radio transmitters that were used for transoceanic radio telephones and broadcasting. The Doherty Approach and Its Evolution Doherty invented his unique amplifier approach in 1936. (“Doherty’s Invention in His Own Words” reproduces an excerpt from the original description of the device published by Bell Laboratories as “A New High-Efficiency Power Amplifier for Modulated Waves.”) This device, which greatly improved the efficiency of RF power amplifiers (PAs), was first used in a 500-kW transmitter that the Western Electric Company designed for WHAS, a radio station in Louisville, Kentucky. Western Electric went on to incorporate Doherty amplifiers into at least 35 commercial radio stations worldwide by 1940 and into many other stations, particularly in Europe and the Middle East, in the 1950s [1]. The Doherty amplifier is a modified class-B RF amplifier. In Doherty’s day, within the Western Electric product line, this namesake electronic device was operated as a linear amplifier with a driver that was modulated. In the 50-kW implementation, the driver was a complete 5-kW transmitter that could, if necessary, be operated independently of the Doherty amplifier; the Doherty amplifier was used to raise the 5-kW level to the required 50-kW level. The amplifier was usually configured as a groundedcathode, carrier-peak amplifier using two vacuum tubes in parallel connection, one as a class-B carrier tube and the other as a class-B peak tube (i.e., power transistors, in modern implementations). The tubes’ source (driver) and load (antenna) were split and combined through + and - 90° phase shifting networks. Alternate configurations included a grounded-grid carrier tube and a grounded-cathode peak tube, whereby the driver power was effectively passed through the carrier tube and was added to the resulting output power—but this benefit was more appropriate for the earlier and less efficient triode implementations rather than the later and more efficient tetrode implementations. As a successor to its Western Electric application for radio broadcast transmitters, the Doherty concept was considerably refined by Continental Electronics Manufacturing Company of Dallas, Texas. Early Con- 42 tinental Electronics designs, by JamesWeldon and others [2], retained most of the characteristics of Doherty’s amplifier but added medium-level screen-grid modulation of the driver. The ultimate refinement was the high-level screen-grid modulation scheme invented by Joseph Sainton [3]. Sainton’s transmitter consisted of a class-C carrier tube in a parallel connection with a class-C peak tube. The tubes’ source (driver) and load (antenna) were split and combined through + and - 90° phase-shifting networks, as in a Doherty amplifier. The unmodulated RF carrier was applied to the control grids of both tubes. Carrier modulation was applied to the screen grids of both tubes, but the screen grid bias points of the carrier and peak tubes were different and were established such that 1) the peak tube was cut off when modulation was absent and the amplifier was producing rated unmodulated carrier power and 2) both tubes were conducting and each tube was contributing twice the rated carrier power during 100% modulation (because four times the rated carrier power is required to achieve 100% modulation). As both tubes were operated in classC, a significant improvement in efficiency was achieved in the final stage. In addition, because the tetrode carrier and peak tubes required very little drive power, a significant improvement in efficiency within the driver was achieved as well. The commercial version of the Sainton amplifier employed a cathode-follower modulator, not the pushpull modulator disclosed in the patent, and the entire 50-kW transmitter was implemented using only nine total tubes of four tube types, all of these being generalpurpose—a remarkable achievement, given that the transmitter’s most significant competitor, from RCA, was implemented using 32 total tubes of nine tube types, nearly one-half of these being special-purpose. The approach was not only used by such leading companies as Continental but also Marconi [3], with functional installations up to the late 1970s. The Institute of Radio Engineers [4] recognized Doherty’s important contribution to the development of more efficient RF PAs with the 1937 Morris N. Liebmann Memorial Award [5]. The Basic Architecture Figure 1 shows the basic Doherty PA (DPA) architecture. Extensive descriptions of DPAs have been given by Cripps [6], so this article includes only a basic explanation. The Doherty block diagram (Figure 1) is notable for its elegance and simplicity and is specifically associated with modern solid-state transistor designs. What may not be apparent is that details of the design can result in large differences in performance. Operation is strongly influenced by the coupling factor of the input divider/coupler and by the biasing of the carrier and peaking amplifier stages. The “turn-on” of the peaking amplifier is dependent on February 2016 Doherty’s Invention in His Own Words “A new form of linear power amplifier has been developed which removes the limitation of low efficiency inherent in the conventional circuit, permitting efficiencies of 60 to 65 per cent to be realized, while retaining the principal advantages associated with low-level modulation systems and linear amplifiers, namely, the absence of any highpower audio equipment, the ease of adding linear amplifiers to existing equipment to increase its power output, and the adaptability of such systems to types of transmission other than the carrier-and-double-sideband transmission most common at present. “Under these conditions the plate efficiency is proportional to the amplitude of the radio-frequency plate voltage. It is possible to obtain large outputs from tubes with radio-frequency plate voltage amplitudes of 0.85 to 0.9 of the applied d-c potential, i.e., with the plate voltage swinging down to a minimum value as low as 10 to 15 per cent of the d-c potential. The corresponding plate efficiency for the tube and its tuned circuit is approximately 67 per cent. This condition, however, prevails only at the peak output of the amplifier, and since the amplitude of the plate voltage wave, in a transmitter capable of 100 per cent modulation, is only half as great for the unmodulated condition as for the peaks of modulation, the efficiency with zero modulation in the conventional amplifier does not exceed half this peak value, or about 33 per cent. “In order to improve this situation it is necessary to devise a system in which the amplitude of the alternating plate voltage wave is high for the unmodulated condition, and in which the increased output required for the positive swings of modulation is obtained in some other manner than by an increase in this voltage. “A simple and fundamental means is available for achieving this result. One embodiment of the scheme is illustrated in [Figure S1]. Each of the two tubes shown in this figure is designed to deliver a peak power of E 2 /R watts into an impedance of R ohms. The total peak output of the two tubes being 2E 2 /R watts, the tubes are suitable for use in an amplifier whose carrier output is one-fourth of this value, or E 2 /2R watts. If the tubes were to be connected in parallel in a conventional amplifier circuit the load impedance used would be R/2 ohms, and each tube would work effectively into R ohms by virtue of the both input power level and gate bias voltage, which in turn sets the low-power efficiency and peak-power capability of the configuration. The peaking amplifier allows the Doherty amplifier to respond to the February 2016 presence of the other tube. The same load impedance R/2 is used in the new circuit, but between the load and one of the tubes (Tube 1) there is interposed a network which simulates a quarter-wave transmission line at the frequency at which the amplifier is operated. “It is a well-known property of quarter-wave transmission lines and their equivalent networks that their input impedance is inversely proportional to the terminating impedance. The network of [Figure S1], in particular, presents to Tube 1 an impedance of R ohms when its effective terminating impedance is also R ohms, that is, when half of the power in the load is being furnished by Tube 2; but should Tube 2 be removed from the circuit, or prevented from contributing to the output, the terminating impedance of the network would be reduced to R/2 ohms, with a consequent increase in the impedance presented to Tube 1 from R to 2R ohms. Under this condition Tube 1 could deliver the carrier power E 2 /2R at its maximum alternating plate voltage E and consequently at high efficiency.” jR Tube 1 -j R -j R Tube 2 R 2 Figure S1. Form of high-efficiency circuit. high input levels of short duration by amplifying the signal peaks and dynamically changing the loading on the main amplifier. The specific class of operation (class-A/B, class-B, class-C, class-F, inverse class-F, 43 Table 1. Doherty-based AM transmitters 1937–1979. Carrier Amplifier (Class-A/B) Installation Year Hybrid Coupler Input 0° 90° Phase Shift Peaking Amplifier (Class C) Output AM, 30 kHz to 50 kW (500 3 MHz kW total) United States 1953 AM, 30 kHz to 500 kW (1 300 kHz MW total) Europe (Voice of America) 1956 AM, 30 kHz to 1 MW 300 kHz East Asia (Voice of America) 1978 AM, 300 kHz to 3 MHz 150 kW (5 MW total) United Kingdom (BBC) 1979 AM, 300 kHz to 3 MHz 2 MW (16 MW total) Middle East Figure 1. The basic Doherty amplifier configuration. etc.) of each amplifier is also important. The two basic considerations for each stage are the bias conditions (biased on, or pinched off, and to what degree) and the fundamental and harmonic impedance terminations presented to the transistors. Power Level Territory 1936–1940 90° Matching Section Frequency Early DPAs 44 Although it was invented in 1936, the first U.S. patent [7] for the DPA was not granted until 1940. The original application for the new high-efficiency configuration was for high-power amplitude-modulated (AM) radio transmitters. By adopting the Doherty architecture dcto-RF conversion efficiencies were increased by a factor of two to over 60% [8]. The DPA soon became a de facto standard for AM transmitters adopted by Western Electric, Continental, Marconi, and RCA (Figures 2 and 3). In subsequent years, DPAs continued to be used in a number of medium- and high-power, low-frequency (LF) and medium-frequency (MF) vacuum-tube AM transmitters [2], [9]. In late 1953, a 1-MW vacuum-tube transmitter operating in the long-wave band began regular operation in Europe where the outputs of the two 500-kW DPAs were joined in a bridge-type combiner. The DPAs had also been considered for use in solid-state MF and high-frequency (HF) systems, as well as in high-power ultrahigh-frequency (UHF) transmitters [10], [11]. The practical implementation of a classical triode-based Doherty scheme was restricted by its substantial non- linearity for both linear amplification of AM signals and grid-type signal modulation, which required complicated envelope correction and feedback linearization circuits. At the same time, the DPAs employing tetrode transmitting tubes could improve their overall performance when the modulation was applied to the screen grids of both the carrier and peaking tubes, while the control grids of both tubes were fed by an essentially constant level of RF excitation [12]. This resulted in the peaking tube being modulated upwards during the positive half of the modulating cycle and the carrier tube being modulated downwards during the negative half of the modulating cycle. Table 1 summarizes the significant AM transmitters built around the Doherty concept between 1936 and 1979. Some tube-based AM transmitters are still in use today. The DPA still remains in use in very high-power AM transmitters; for lower-power AM transmitters, however, vacuum-tube amplifiers were eclipsed in the 1980s by solid-state PAs due to the advantages they offered of smaller size and cost, lower operating voltages, higher Figure 2. The 1938 50-kW Doherty AM transmitter at WHAS in Kentucky. Figure 3. A 1978 150-kW Doherty AM transmitter at the BBC in the United Kingdom. February 2016 Different circuit design techniques have been proposed to improve the linearity of DPAs. to reduce DPA distortion. Recently, DPAs of different architectures have found widespread application in cellular base-station transmitters operating at gigahertz frequencies. Digital Radio and Television Broadcast Transmitters The main motivation for high-efficiency PAs for modern digital radio and television transmitters is to reduce operational costs [15]. Operational costs have always been a key issue for broadcasters, and a substantial part of these costs is due to the electricity required to run a transmission network, which can account for over 75% of the total electricity used by a broadcaster (Figure 4). Since higher efficiency PAs consume lower power and create less heat, they also provide overall reliability improvements. Further, increasing government legislation is forcing energy users into action to improve their environmental (“green”) credentials. Figure 4 shows the average electricity costs in the United Kingdom (assuming 12 pence per kWh) for 8-, 16-, 24-, and 32-kW Model MRF6VP3450 Doherty 60 55 Efficiency (%) reliability and greater physical ruggedness, insensitivity to mechanical shock and vibration, and the possibility of using fully automated manufacturing processes and high levels of integration. In addition, both bipolar and field-effect transistors are generally characterized by significant nonlinearities in their transfer characteristics and intrinsic capacitances that require complex linearization schemes. Those schemes could only be implemented using analog techniques in the 1980s, limiting the use of DPAs. Interest in DPAs was later revived, owing to significant progress in radio communication systems based on complex digital modulation schemes such as Worldwide Interoperability for Microwave Access (WiMAX), orthogonal frequency-division multiplexing (OFDM) systems, code-division multiple access (CDMA) 2000 and wideband CDMA (W-CDMA), and long-term evolution (LTE) enhancements to the Universal Mobile Telecommunications System wireless standard, where the sum of several constant-envelope signals creates an aggregate AM signal with high peak-to-average ratios (PARs). The complex digital modulation schemes used in these modern wireless communication standards require even higher levels of linearity. Different circuit design techniques have, therefore, been proposed to improve the linearity of DPAs, such as optimal biasing of carrier and peaking cells for intermodulation cancellation and optimized uneven power splitting for proper load modulation and thus higher linearity [13], [14]. Furthermore, it has been proven that the effect of nonlinear output capacitance on the load modulation is circumvented using simple offset line structures [14]. However, complex linearization schemes are still required to meet the stringent linearity requirements of modern wireless communication systems. Both digital pre-distortion and circuit design techniques have been very successfully applied 50 45 40 714 MHz 719 MHz 724 MHz 35 30 25 0 30 60 90 12 150 180 210 240 270 300 330 360 390 420 450 480 510 0 20 350 RF PA Electricity [Cost per Year (£k)] 300 250 Typical Efficiency Range of Current Products Total RF Power Output from Transmitter Pout(W) Figure 5. The efficiency of a Freescale LDMOSFET DVB Doherty amplifier as a function of backed-off power. 32 kW 200 24 kW 150 16 kW 100 8 kW 50 0% at 12 p/kWh 20% 40% PA Efficiency 60% Figure 4. Average electricity costs in the United Kingdom for DVB transmitters as a function of PA efficiency. February 2016 Figure 6. A 1-kW output power DVB DPA for 714–724 MHz. 45 (a) Pout (dBm) and Efficiency (%) 45 Doherty Module Performance 40 Third- and Fifth-Order IM (dBc) 0 -5 Pout 35 - 10 30 25 20 - 15 - 20 PAE - 25 IM3 15 10 - 30 - 35 IM5 5 0 -15 - 40 -5 - 10 (b) 0 - 45 Pin (dBm) transmitters as a function of overall PA efficiency [15]. For example, increasing efficiency from 20% to 40% reduces cost per year from £170,000 to £80,000. Significantly, both Freescale [15] and NXP [16] have demonstrated DPA reference designs configured into multikilowatt transmitters for digital video broadcast (DVB) applications where overall transmitter efficiencies have been doubled using silicon laterally diffused metal-oxidesemiconductor field-effect transistors (LDMOSFETs) compared with older tube-based designs (including inductive-output tubes). Suppliers such as Rohde and Schwarz [17] have used such solid-state technology to provide a range of VHF and UHF transmitters that are liquid-cooled. Figure 5 shows the efficiency of a DPA employing Freescale LDMOSFETs as a function of output power over 714–724 MHz. Efficiency is maintained at greater than 53% over a 3-dB back-off range. Figure 6 shows four DPAs combined in a prototype system offering over 1-kW output power with an overall improvement in efficiency by 40% compared with a conventional (non-DPA) system. Handset Transmitters DPAs are used in many digital radio and TV transmitters as well as in cellular base-station applications but have been less popular in handset applications where envelope-tracking (ET) techniques have recently begun to dominate [18]. However, the Doherty approach was used in L-band Iridium satellite handset PAs produced by Motorola in the mid-1990s. This approach was taken as a way to conserve battery life as well as to reduce heat dissipation [19], in particular because the transmitted power levels from the handsets were several watts (much more than required in a land-based cellular system). The two-way balanced DPAs used gallium arsenide (GaAs) pseudomorphic high-electron mobility transistor (pHEMT) technology incorporated into hybrid “chip-and-wire” circuits (Figure 7), achieving power-added efficiencies (PAEs) of 37% at output powers of approximately 2 W (approximately 5 dB backed off from peak power to achieve the required linearity). More recently, DPAs have been employed in a number of handset applications using 0.25- and Figure 7. (a) A two-way balanced DPA used in Motorola Iridium handsets. (b) The output power, PAE, and intermodulation (IM) products versus input power for a dual DPA. Figure 8. A photograph depicting an InGaP/GaAs HBT MMIC DPA for 1.6–2.1 GHz handset applications. 46 February 2016 0.15-μm GaAs pHEMT processes being deployed at 17 and 20 GHz, respectively, for digital satellite systems. Monolithic-microwave integrated-circuit (MMIC) DPAs using 0.13-μm RF complementary– metal-oxide-semiconductor (CMOS) processes have been deployed at 60 GHz for wireless personal network transceivers. However, MMIC DPAs for 900-, 1,800-, 2,140-MHz, and higher handset applications are more difficult to design because of the need for low-cost-requiring chip-size constraints. Moreover, another important requirement with handset PAs is multimode, multiband operation, which is challenging to achieve in DPA designs without using tunable components in the output and input networks [20]. The most popular processes being used are CMOS and heterojunction bipolar transistor (HBT) together with the use of lumped elements and novel circuit approaches to reduce size [21]. Novel circuit approaches used to produce small handset DPAs have been recently extended to provide solutions for LTE applications across bandwidths of 1.6–2.1 GHz. The MMICs use low-Q quarter-wave transformers, lumped-element phase compensation networks on the input, and transistor output capacitances into phase compensation networks on the output. The MMICs employed an indium gallium phosphide (InGaP)/GaAs 2-μm HBT process, and off-chip bond wires were used for critical inductors (Figure 8) [22]. The reported gain was greater than 28 dB at an average output power of 27.5 dBm (using a 10-MHz bandwidth LTE signal with a 7.5-dB PAR). Linearity was measured using the error vector magnitude method at 3.8%, with an accompanying adjacent channel power ratio (ACPR) of -32 dBc. In [23], a 1.85-GHz linearity improved dual-mode InGaP/GaAs MMIC handset DPA is presented. In this Doherty design, the gate bias voltages of the PA cells and the input power splitting ratio are optimized for a low level of third-order intermodulation products. The reported ACPR was -37 dBc with related PAE of 42% using a 10-MHz LTE signal with a 7.5-dB PAR. DPAs have become the de facto standard approach for achieving high-efficiency PAs in a mix of cellular infrastructure equipment ranging from “small-cell” to “macro-cell” applications. 43%. It uses a pair of NXP LDMOSFETs in a symmetric configuration. It can be seen that the input matching for the peaking PA is somewhat different than for the carrier PA because they are operating at different quiescent drain current levels. As instantaneous/video bandwidths increase, coupled with carrier aggregation for next-generation cellular systems, the intrinsic narrow-band nature of conventional DPAs becomes a challenge. However, a number of techniques that can extend the bandwidth of DPAs are available, as described in the following section. These techniques are particularly relevant to lower average power architectures such as “small-cells,” and it is likely that fifthgeneration (5G) and later systems will employ much higher numbers of such low-power “distributed” transmitters. Modern Trends DPAs are far from a past or “fading” high-efficiency PA approach. The attraction of DPAs is that, even with added complexities for the previously discussed application extensions, they are well proven and reliable approaches. Advances in solid-state technology and compact hybrid and MMIC approaches as well as recent low-cost analog and digital predistortion techniques have shown that DPAs will not disappear from the two main application areas in the near term: Cellular Infrastructure Transmitters DPAs have become the de facto standard approach for achieving high-efficiency PAs in a mix of cellular infrastructure equipment ranging from “small-cell” to “macro-cell” applications, where average transmitted powers are from a few watts to hundreds of watts respectively. The majority of those applications today employ silicon LDMOSFET transistors in the driver and output stages, but gallium nitride (GaN) HEMT transistors have become increasingly used for the latest base-station equipment owing to their higher gains, power densities, bandwidths, operating frequencies, and efficiencies [24]. One example of a DPA produced by Nokia is shown in Figure 9 which produces 60 W of average power at 2,100 MHz with an overall transmitter efficiency of February 2016 Figure 9. An example of a 2.1-GHz DPA, produced by Nokia, for base-station applications with an average power of 60 W. 47 Modern Trends for DPAs •A wealth of semiconductor technologies is being used (e.g., Figures S2–S5): RF CMOS, GaAs pHEMT, InGaP/GaAs HBT, silicon LDMOSFET, and GaN HEMT •A range of frequencies and power levels is being covered: UHF to 60 GHz, hundreds of milliwatts to multikilowatts •A variety of circuit techniques is being adopted: Classical, inverted, asymmetric; unequal power division to carrier and peaker, different sized transistors for carrier and peaker, and combinations of both N-way to increase backed-off (linear) power range for high efficiency Use of different classes of amplifiers in carrier and peaker • •Multiband (dual and triband), broadband •Reconfigurable using switched sections or varactor tuning • • • • (a) Four-Stage g DA Three-Stage g DA Two-Stage DA Efficiency fficiency (%) 80 60 40 20 0 -24 Class B PA -18 -12 Asymmetric Four-Way DA 0 -6 Back off Power Level (dB) (b) Figure S2. An example of a 2.11–2.14-GHz LDMOSFET asymmetric DPA from Freescale: carrier, 140 W; two peakers, 280 W; average power of 75 W at 8-dB back-off with 46% efficiency. Figure S3. An example of a 2.5–2.7-GHz GaN HEMT asymmetric DPA from Cree: carrier, 150 W; peaker, 300 W; average power of 80 W at 8-dB back-off with 49% efficiency. 48 Figure S4. (a) An example of a 2.14-GHz four-way DPA using 25-W GaN HEMTs and a W-CDMA signal with (b) 6.5-dB PAR and average power of 20 W with 61% drain efficiency (from Bell Labs, Alcatel, and Lucent). Figure S5. An example of a 1.9–2.6-GHz reconfigurable DPA using MEMS switches: average power of 2 W at 9-dB back-off with efficiencies of 60% at 1.9 GHz, 61% at 2.14 GH z, and 64% at 2.6 GHz [20]. February 2016 Vi Extended-EfficiencyRange DPAs The classical Doherty configuration provides efficiency enhancement for an output power dynamic range of 6 dB. Raab has, however, theoretically shown the possibility of extending the efficiency range of DPAs by making the peaking cell larger than the carrier cell [28]. Such a modification enables a higher modulation ratio and, thus, a higher backoff efficiency range to be achieved. This variant of DPAs is commonly referred as asymmetrical DPA and uses the same load network topology as the classical configuration but with different circuit element values. Iwamoto et al. [29] are February 2016 P1dB 60 Doherty Control 50 Efficiency (%) present and future digital radio/television transmission and cellular communications. As summarized in “Modern Trends for DPAs,” a wealth of semiconductor technologies is being used to implement new DPAs—including RF CMOS, GaAs pHEMT, InGaP/GaAs HBT, silicon LDMOSFET, and GaN HEMT—covering a wide range of frequencies from UHF to 60 GHz at power levels from hundreds of milliwatts to multi-kilowatts. Various new circuit techniques have also been adopted to further improve the performance of DPAs. One of the main research areas has been extending the efficiency range of DPAs for amplification of very high (8–12 dB) peak-to-average power ratio (PAPR) signals. There have been also significant efforts in recent years to improve the RF bandwidth for broadband applications. Further, reconfigurable DPAs for the realization of multiband, energy-efficient PAs have also been extensively studied. This section reviews the modern trends in DPA development, including references to representative research works. More comprehensive reviews are presented in [1] and [25]. It is not our intention to go into great detail regarding each DPA variant, but rather to provide an overview of recent research on DPAs. Design guidelines and in-depth mathematical analysis of different DPA variants can be found in [6], [26], and [27]. Our review will start with extended efficiency range (26 dB) DPAs, move on to broadband and reconfigurable PAs, and finally present an outZm look on the role of the DPA in next-generation communication Im Main systems operating at millimeClass B ter-wave frequencies. + 40 30 20 10 0 - 10 - 5 0 5 10 15 20 25 30 Pout (dBm) Figure 10. The collector efficiency of a 900-MHz InGaP/ GaAs asymmetrical DPA [29]. credited for realization of the first experimental demonstrator through a 950-MHz 27.5 dBm asymmetrical DPA, which was realized in an InGaP/GaAs process. As seen from Figure 10, the prototype exhibits a very distinct efficiency peak at 10-dB back-off power level, thereby fully proving the feasibility of the concept. Asymmetrical DPAs are well adopted by the industry and very commonly used as micro and macro base-station PAs. Currently, LDMOS is the preferred Za Lossy and Reciprocal P1 Two-Port (Z2P) Ia P2 Aux. Class C + Vm Va - - AVie-ji (a) Lossless and Reciprocal P1 P3 (Z2P- A) (Z2P- B) P2 R (b) Figure 11. (a) A schematic used for the derivation of the two-port combiner network parameters of a symmetrical DPA. Z m and Z a denote the fundamental tone impedances experienced by the transistors, where n is the harmonic index. Vm, Va and I m, I a denote the fundamental tone component of the drain voltage and current waveforms. (b) This intermediate network later converted to a three-port lossless network terminated with the load [38], [39]. 49 technology for realization of asymmetrical DPAs for base-station applications [30]–[32]. GaN HEMT asymmetrical DPAs are, however, also being studied for fuh 80 ture systems [33]–[35]. Among the best results, a drain PAE efficiency of 60% with 8.3 PAPR signals at 2.6 GHz 60 was shown in a 51-dBm GaN HEMT prototype [36]. 40 The measured PAE, however, was only 49% due to low gain, which is somewhat typical in asymmetrical 20 DPAs [35], [37]. The peaking amplifier is much larger 0 than the carrier amplifier in asymmetrical DPAs. The 31 33 35 37 39 41 43 45 overall gain is therefore dominated by the low gain of Output Power (dBm) the class-C biased peaking amplifier and, thus, lower (a) than in symmetrical DPAs. 0 The use of a very large class-C cell also causes prac- 10 tical limitations on realization of the analog input signal splitter [13]. - 20 Recently, there has been an interest in extending the - 30 efficiency range of symmetrical DPAs by modification - 40 of the combining network. Özen et al. [38], [39] have - 50 demonstrated the existence of a class of symmetrical - 60 DPAs having efficiency peaks also for back-off levels 3.3 3.35 3.4 3.45 3.5 3.55 3.6 3.65 3.7 larger than 6 dB while maintaining full voltage and Frequency (GHz) current swings of both the carrier and peaking tran(b) sistors. The design technique is based on an analytical derivation of the combiner network parameters from Figure 12. (a) The measured static PAE and drain efficiency the desired boundary conditions required for high effiresults of an extended-efficiency-range symmetrical DPA at ciency operation, and its practical realization is derived 3.5 GHz. (b) The modulated measurement results without from the desired boundary conditions required for (blue) and with (green) digital predistortion (DPD) using carrier-aggregated 100-MHz OFDM signals [38]. high-efficiency operation. The derived combiner, therefore, integrates the matching networks, offset lines, and impedance inverter. A schematic used for the deriva100 tions is shown in Figure 11. 80 This new symmetrical DPA has the advantages of increased gain and cost reduction due to the use 60 of symmetrical devices. Furthermore, design and 40 realization of the input power splitter are simplified due to less uneven power splitting compared to the 20 conventional asymmetrical DPA case. These distinct 0 advantages enabled a 100-MHz instantaneous band-30 -25 - 20 - 15 - 10 -5 0 width 3.5-.GHz symmetrical DPA which provides a Normalized Output Power (dB) record high PAE of 52% with 9-dB PAPR LTE signals. Static and modulated measurement results are shown Figure 13. The efficiency of asymmetrical (blue) and threein Figure 12. way DPAs (red) versus normalized output power. The N-way DPA approach is another way of extending the efficiency range. In this configuration Main Upconverter the number of efficiency peaks xm RF PA DAC LPF is equal to number of branches. The main advantage of N-way RF Upconverter DPAs compared to asymmetrical yd DSP xp Output RF PA DAC LPF DPAs is that, theoretically, less efUnit ficiency drop occurs between the Downconverter Peaking efficiency peaks. This is illustraty DAC LPF ed in Figure 13 for the three-way Doherty case. However, in such realizations the signal distribution Figure 14. A block diagram of a dual-input DPA transmitter architecture. DSP: and combining networks become digital signal processor; LPF: lowpass filter. Efficiency (%) Power Spectral Density (dB/Hz) Efficiency, PAE (%) 100 50 February 2016 DPAs with Individual RF Input Signal Control The conventional, analog-splitter-based DPA has a great advantage in its simplicity and as a direct class-A/B PA replacement. However, significant improvements achieved in energy consumption of digital-to-analog converters (DACs) and digital circuits with aggressive CMOS scaling over the last decade are making DPAs with individually controlled carrier and peaking amplifier input signals interesting, particularly for base-station applications [46], [47]. A block diagram of a dual-input Doherty transmitter architecture is shown in Figure 14. In contrast to a conventional class-B/C Doherty system, no power is wasted in dual-input DPAs when the carrier cell is turned off, which improves the gain and PAE. Furthermore, in [48] the authors proposed to dynamically vary the phaseoffset between the branches to enhance the load modulation in dual-input DPAs. Experimental results show that a significant PAE enhancement can be achieved between the efficiency peaks (see Figure 15). It should also mentioned that, very interestingly, individual control of the input signals also provides important possibilities for bandwidth enhancement [49], [50] and for frequency reconfigurable PAs, as described in later sections. Interest in DPAs was later revived, owing to significant progress in radio communication systems based on complex digital modulation schemes. Pelk et al. [51] proposed a three-way Doherty with individual control of each branch signal in the digital domain to overcome the implementation issues faced in the analog realization. A GaN HEMT demonstrator was built for experimental verification, which provided a record high PAE of 64% at 12-dB back-off (see Figure 16). However, very high complexity and the high cost of such approach is, unfortunately, hampering its widespread adoption by the industry. An interesting research topic related to multi-input DPA architectures is how to find optimal signal designs that maximize high efficiency and linearity. A common approach is to characterize the PA with continuous wave signals to identify optimal signal combinations for the best efficiency versus back-off. In this way a static inverse model of the PA is constructed and used for constellation mapping 70 60 50 PAE (%) significantly more complex compared to conventional DPAs. Due to these complications, practical N-way DPAs often do not meet the expected theoretical performance [40]–[45]. It should also be mentioned that, so far, the focus in this field has been limited mainly to realization of three-way DPAs due to practical issues. 40 30 20 Adaptive Phase Alignment On (PAE) Adaptive Phase Alignment Off (PAE) 0 - 20 80 70 PAE (%) Three-Way GaN Doherty, Profile 1 Three-Way GaN Doherty, Profile 2 Single Class-B GaN Amplifier -15 -10 -5 0 Pout (dB Relative to Pmax) 10 Figure 16. The measured single-tone PAE of a three-way DPA versus the output power back-off for different drive profiles [51]. 60 50 Static Splitter 40 ydesired 30 18 20 22 24 26 Input Power (dBm) 28 30 Figure 15. The efficiency of a dual-input DPA with and without adaptive phase alignment [48]. February 2016 DPD a y fm fp Main PA xm xp y Peaking PA Figure 17. The conventional scheme used for linearization of a dual-input DPA. 51 Efficiency- and Output-PowerReconfigurable DPAs Efficiency (%) So far we have reviewed DPAs that are optimized for a certain output power level and for a signal with Harmonic Tuning fixed statistics (i.e., PAPR). VGS Main However, base stations and, Main Input in particular, handset PAs Network One Switch are not always operated at full power. The RF output RF Out Output power can be reduced when Network Two the data traffic is low or Switches when the distance between Aux In the mobile terminal and the Ground MEMS base station is short. AccuSwitch rate output power control is VGS Aux Control Lines also necessary in the handfor Different Settings P sets to maximize the system VGS in-avg Variable throughput and battery Auxillary lifetime. In such cases, it is Gate Bias highly desirable to have a DPA with a reconfigurable (a) output power level to mainPout = 21 dBm tain efficient operation. Mohamed et al. [20] have Pout = 16 dBm hD 80 shown that it is possible to rePAE Pout = 11 dBm configure the output power 70 level of DPAs by incorporating microelectromechanical 60 systems (MEMS) switches 50 in the load network. A photo of the fabricated 2.6-GHz 40 GaN HEMT demonstrator and the measurement re30 sults of the prototype are 20 shown in Figure 18. Further, the authors showed the 10 feasibility of reconfiguring the efficiency range using 0 18 20 22 24 26 28 30 32 34 36 38 40 MEMS switches in the load network [53]. Output Power (dBm) Gustafsson et al. [50], (b) [54] have proposed a modified DPA targeting wideFigure 18. (a) A photo of the fabricated MEMS-based reconfigurable peak power GaN HEMT band applications (see the DPA demonstrator. (b) The measured efficiency results versus the output power for three next section) but have also different power modes [20]. shown that the back-off efficiency range can be reconfigured by varying the of branch signals according to the desired output supply voltage of the carrier cell and the current prosignal. Thereafter, residual nonlinearities and memfile (gate bias) of the peaking cell. Such an approach ory effect are corrected with a DPD block before the is favorable, especially when there are no good tunstatic inverse model, as shown in Figure 17. On the able components available in the semiconductor proother hand, more advanced signal design algorithms cess used. are also being developed to achieve even better efIn [55], a 1.95-GHz GaN HEMT output power reficiency–linearity compromise in multi-input PA arconfigurable DPA is presented, where the power chitectures [52]. 52 February 2016 adaptation is achieved by changing the drain and gate bias voltages. Carrier m/4 PA Wideband DPAs 70.7 X 100 X m/4 P (a) 60 40 0 PAEavg Pout,avg - 10 NMSE ACPR - 20 30 - 30 20 - 40 10 - 50 50 0 5.5 6 6.5 7 7.5 8 8.5 Frequency (GHz) 9 - 60 9.5 NMSE (dB) and ACPR (dBc) PAEavg (%) and Pout,avg (dBm) Output Power (dBm) and Efficiency (%) out Pin With an increasing number of frequency bands Peaking 50 X allocated for wireless communication, there 50 X 70.7 X PA has been intense research targeting wideband m/4 m/4 DPAs. It has been recognized that the m/4 im100 X 50 X pedance inverter of the original Doherty to(a) pology is limiting the theoretical efficiency enhancement bandwidth to roughly 30%, but 90 Saturated Output Power the bandwidth is, in practice, further limited Efficiency at Saturated Output Power by the device parasitics. Qureshi et al. have ex80 Efficiency at 6 dB of Power Back-Off plored the possibility of absorbing the carrier 70 and peaking device output capacitances into the impedance inverter for a wideband LDMOS 60 based DPA [56]. Guolin and Jansen presented a 50 more generic approach in [57], where a simplified real-frequency technique is applied with a 40 comprehensive optimization scheme to derive carrier, peaking, and load matching networks 30 that together approximate the optimum load20 pull based carrier and peaking transistor im1,000 1,200 1,400 1,600 1,800 2,000 2,200 2,400 2,600 pedances across a wide bandwidth. Frequency (MHz) Recently, several researchers have recog(b) nized that the bandwidth of the DPA can be increased significantly by augmenting the Figure 19. (a) A DPA topology with the combiner modified for network connected to the peaking transis- improved bandwidth [62]. (b) The measured drain efficiency and tor output [58]–[63]. Abadi et al. introduced a output power for a 1.2–2.6-GHz wideband GaN DPA based on the resonant-shunt LC network at the peaking PA topology in (a) [58]. output that simultaneously offers convenient fre et al. used the same technique to achieve a record biasing, linearity, and harmonic tuning efficiency 1.0–2.6-GHz bandwidth DPA with 6-dB back-off effi[59]. By instead adding a two-section impedance ciency 235% across the band [58] [see Figure 19(b)]. transformer to the peaking device, a more wideband The approach is also suited for wideband high-power back-off efficiency characteristic is obtained. This commercial applications, as recently demonstrated by technique, which is shown in Figure 19(a), was origiFreescale [61] and NXP [60]. The wideband DPA in [60] nally explored in a dual-band class-E DPA [62]. Gio- (b) Figure 20. (a) A fully integrated 5.8–8.8-GHz GaN MMIC DPA (2.9 mm by 2.9 mm) based on a modification of the impedance-inverter impedance for improved bandwidth and efficiency reconfigurability [54]. (b) The measured average efficiency (PAEavg) and output power (Pout,avg) for a 20-MHz 256-QAM signal. A vector-switched digital predistortion algorithm [87] enabled excellent linearity, characterized by the normalized mean square error and ACPR. February 2016 53 nals. The modified DPA architecture has been demonstrated by a fully integrated 5.8–8.8-GHz GaN MMIC targeting point-to-point radio links [see Figure 20(a)] [54]. As shown in Figure 20(b), an excellent average PAE of 32%–41% and linearity are obtained across the band when tested with a 20-MHz, 8.5-dB PAR 256 [20] quadrature amplitude modulation (QAM) signal. As described previously, the back-off efficiency can also be reconfigured in this topology, which means that a wide range of wireless standards in a wide frequency range can be amplified efficiently with the same circuit. Quad-Band Biasing Network Input Impedance Matching Network Output Load Transformation Network Quad-Band IIN Broadband IPS Input Impedance Matching Network Quad-Band Phase Compensation Network Broadband Impedance Transformer Output Load Transformation Network Quad-Band Biasing Network Figure 21. A quad-band (950/1500/2140/2650 MHz) DPA [69]. IPS: input phase splitter; IIN: impedance inverter network. has also been used by He et al. as the basis for realizing a wideband push-pull DPA in [64]. The push-pull operation enables, in theory, an independent control of the fundamental and second-harmonic impedances and thereby improved efficiency. The performance is, in practice, limited by the balun performance and, in particular its common mode parasitic coupling to ground [65]. Gustafsson et al. [50] and Wu and Boumaiza [66] have, independently, proposed a modified DPA in which the impedance of the m/4 impedance inverter is set to match the PA load impedance. In contrast to conventional DPAs, this eliminates any band limiting impedance transformation at back-off and, thus, a significantly larger efficiency bandwidth for realistic modulated sig- Multiband DPAs For cost and complexity reasons, it is highly desirable that the same PA be able to cover as many frequency bands as possible. Unfortunately, the wideband approaches presented previously present an inevitable performance degradation as the bandwidth increases to cover more bands. This has motivated significant research on multiband DPAs that utilize the fact that the commonly used frequency bands are typically widely separated. Optimized DPA designs targeting specific bands, rather Phase-Shifting Preamplifier IAux Input Output ZMain Clock Auxiliary Amplifier IMain VDD RLoad VMain L = m/4 Z0 = 2·RLoad Main Amplifier Carrier Control Bits (a) .. . m/4 Delay Peaking Control Bits VDD .. . Measurement Simulation 30 PAE DE 20 10 0 Figure 22. The schematic for an RF-DAC based DPA. 54 DE, PAE (%) 40 4 6 8 10 12 Pout (dBm) 14 16 18 (b) Figure 23. (a) A block diagram of an active phase-shift DPA. (b) The measured efficiency of a 45-nm SOI CMOS active phase-shift DPA at 45 GHz [79]. February 2016 than a generic wide-frequency coverage, are therefore expected to perform better. Saad et al. [67] have described the design of a dualband GaN-based DPA, operating at 1.8 and 2.4 GHz. The DPA utilizes a dual-band design technique for the power splitter, phase shifter, matching networks, and impedance inverter [68]. When tested at 1.8 GHz with 7.5 dB PAR LTE signals and at 2.4 GHz with 8.5 dB PAR WiMAX signals, the manufactured PA demonstrates an average PAE of 54% and 45%, respectively. Ngiem et al. [69] have presented tri- and even quad-band DPA designs covering 950, 1,500, 2,140, and 2,650 MHz (see Figure 21). A clear Doherty efficiency behavior is reported in each band with PAE at 6-dB output power back-off ranging from 43% at the lower band but decreasing to 26% at 2.65 GHz. The circuit complexity and size increase rapidly with the number of bands covered, and the advantage of a multiband versus a broadband design approach diminishes in practice. Special care needs to be taken when transmitting concurrent signals in multiple bands. In particular, the linearity in each band is degraded. Dedicated concurrent dual- and triple-band DPD algorithms have been proposed in [59] and [70], [72]. Gustafsson et al. have shown that the fundamental DPA load modulation is affected by the concurrent multiband operation and that the behavior of the impedance inverter, also at interband mixing frequencies (i.e., f2 - f1 and f1 + f2 ), will degrade the efficiency enhancement if not properly handled [73]. Multiple frequency bands can also be covered by using reconfigurable elements in the DPA architecture. In [74], Mohamed et al. presented a tri-band 1900/2140/2600-MHz DPA that was implemented using MEMS switches in the combiner and input matching networks. Based on the same principle, the authors also presented a combined multimode, multiband DPA in [75]. Andersson et al. have demonstrated a continuously reconfigurable 1–3-GHz transmitter [49]. A fixed hardware is used, but a continuum between outphasing and DPA solutions is used as a basis to show that a digital reconfiguration of the control schemes to the two RF inputs can be used to enhance the back-off efficiency across a record wide frequency range. It should be stressed that these reconfigurable DPAs do not support concurrent transmission in multiple bands. RF-DAC Based DPAs A very active research field in the wireless industry is digitally intense transmitters for further integration and performance improvement. In digital transmitters, the signal generation and modulation are done using digital only blocks in CMOS and eventually completely integrated with the baseband processor. One digital technique studied for amplitude modulation is to oper- February 2016 Advances in solid-state technology and compact hybrid and MMIC approaches as well as recent low-cost analog and digital predistortion techniques have shown that DPAs will not disappear in the near term. ate the PA as a multibit DAC. The output amplitude controlled by regulating the number of active transistors in the PAs. In conventional RF-DAC circuits, however, the transistor cells load-pull each other in an undesired way, causing severe efficiency degradation at back-off. However, by combining the output of two RF-DACs with a Doherty combiner network, proper load modulation may be enabled. A generalized schematic of an RF-DAC based DPA is shown in Figure 22. In [76], Gaber et al. demonstrated a 2.4-GHz, 25-dBm RF-DAC–based DPA in 90-nm CMOS technology. Tuning capacitors at the output were also utilized to further improve the load modulation. Song et al. have demonstrated a 3.7-GHz, 27-dBm RF-DAC DPA in 65-nm CMOS, using transformer-based passives for the input power divider and output combiner networks to minimize losses in the passives [77]. The RF-DAC–based DPA architecture enables individual control of the current profiles of the carrier and peaking PAs. In [78], Song et al. explored this for antenna mismatch correction. It was shown that the high-efficiency Doherty operation can be maintained for a wide range of load impedances by reconfiguring the digital control bits. Millimeter-Wave DPAs for 5G The wireless industry is planning to exploit millimeter bands in 5G systems to augment the currently saturated 700-MHz–3.5-GHz radio spectrum bands. Interest in millimeter-wave, high-efficiency transmitter architectures is, therefore, rapidly growing [79], [80]. There are, however, a number of challenges ahead that Main Amplifier (Class AB) M 2 Lp 2 COut Input Auxiliary Amplifier (Class C) M 2 COut Ls RL Lp 2 COut Figure 24. The schematic illustration of a voltagecombined DPA [86]. 55 Recent developments of the Doherty concept make it one of the most attractive candidates for realizing energy-efficient wireless systems into the future. have to be solved for successful realization of millimeter-wave DPAs: •• At millimeter wave frequencies, the devices typically provide very low gain for class-C operation. This fact may severely limit the PAE of millimeter-wave DPAs. •• Metallic losses become more prominent at high frequencies. Low-loss realization of the quarterwavelength inverter and phase shifter networks has to be studied. •• Due to low output power levels, digital predistortion is not feasible for millimeter-wave applications. Millimeter-wave DPAs should therefore provide a good analog linearity for successful realization 5G base-station transmitters. Some of these problems have already been addressed in recent publications. In [79], Agah et al. have realized a 45-GHz active phase-shift DPA in 45-nm silicon-on-insulator (SOI) CMOS. The authors proposed to replace the quarter-wavelength input phase shifter with an extra predriver amplifier to improve the PAE. A block diagram of the concept is shown in Figure 23. The prototype presents peak and 6-dB back-off efficiencies of 20% and 21%, respectively. Further, the authors also studied the use of slow-wave coplanar waveguides (CPWs) for realization of the impedance inverter to minimize the metallic losses. It was shown that the slow-wave CPW structure yields 42% more PAE at 6-dB back-off compared to the conventional CPW structure. In [81], Kaymaksut et al. proposed the voltage-combined DPA concept, which enables compact integrated realizations. The idea originates from the principle of distributed active transformer PAs [82]. In this topology, the voltages of the differential carrier and peaking PA cells are summed using transformers (see Figure 24). Neither a quarter-wavelength inverter nor an input phase shifter is needed in such an approach, which makes it very suitable for handset and millimeter-wave base-stations applications. In fact the topology is already studied in various publications for realizing S-band handset DPAs [83]–[85]. The first millimeter-wave realization, however, was presented in [86]. A 77-GHz, 21-dBm voltage-combined DPA was implemented in a 40-nm CMOS process. An on-chip envelope detector was also implemented for dynamic biasing of the peaking cell. In this way the carrier device can be biased in class-A/B operation at peak power and below the gate threshold for lower signal envelopes. The class-C 56 operation mode and its associated low gain are thereby avoided. The PAE at peak power and 6-dB back-off is 13.6% and 7%, respectively. Finally, it should also be mentioned that the network synthesis methodology in [38] and [39] enables the functionality of the matching networks, offset lines, and impedance inverter to be realized with a network that consists of only five reactive components. Such a high level of integration may create new opportunities for research and development of integrated handset and millimeter-wave DPAs with high performance. Conclusions Eighty years ago, William Doherty invented a PA architecture that has played—and will continue to play—an important role in the development of energy-efficient radio transmitters for a variety of wireless communication applications. Although the original concept is still equally valid, the development of new semiconductor processes and digital signal processing techniques has served as a basis for an evolution of the DPA topology into the 21st century. The need for energy-efficient power amplification will be further emphasized in future wireless systems (5G and beyond) through the projected exploration of dense-antenna arrays and millimeter-wave frequencies. Recent developments of the Doherty concept make it one of the most attractive candidates for realizing energy-efficient wireless systems into the future. References [1] B. A. Grebennikov and S. Bulja, “High-efficiency Doherty power amplifiers: Historical aspect and modern trends,” Proc. IEEE, vol. 100, no. 12, pp. 3190–3219, 2012. [2] C. E. Smith, J. R. Hall, and J. O. Weldon, “Very high-power longwave broadcasting station,” Proc. IRE, vol. 42, no. 8, pp. 1222– 1235, 1954. [3] “AM transmitters,” 2010. [Online]. Available: http://www.oldradio.com/archives/hardware/CE/316.htm.ed [4] “IRE Medal of Honor winners,” 2015. [Online]. Available: http:// www.ieeeghn.org/wiki/index.php/IRE_History_1912-1963.ed [5] “William H. Doherty, Recipient, Morris Liebmann Memorial Prize, 1937,” Proc. IRE, vol. 25, no. 8, p. 922, 1937. [6] S. C. Cripps, Advanced Techniques in RF Power Amplifier Design. Norwood, MA: Artech House, 2002. [7] W. H. Doherty, “Amplifier,” U.S. Patent 2 210 028, Aug. 6, 1940. [8] W. Doherty and O. Towner, “A 50-kilowatt broadcast station utilizing the Doherty amplifier and designed for expansion to 500 kilowatts,” Proc. IRE, vol. 27, no. 9, pp. 531–534, 1939. [9] J. Sainton, A 500 Kilowatt Medium Frequency Standard Broadcast Transmitter, ed., Machlett. Springdale, CT: Cathode Press, 1965. [10] J. Wood, History of International Broadcasting, (IET, no. 19), 1994. [11] V. Rozov and V. Kuzmin, “Use of Doherty circuit in SSB transmitters,” Telecommun. Radio Eng. USSR, p. 11, Feb. 1971. [12] A. Mina and F. Parry, “Broadcasting with megawatts of power: the modern era of efficient powerful transmitters in the Middle East,” IEEE Trans. Broadcast., vol. 35, no. 2, pp. 121–130, 1989. [13] K. Jangheon, C. Jeonghyeon, K. Ildu, and B. Kim, “Optimum operation of asymmetrical-cells-based linear Doherty power Amplifiers-uneven power drive and power matching,” IEEE Trans. Microwave Theory Tech., vol. 53, no. 5, pp. 1802–1809, 2005. February 2016 [14] B. Kim, K. Jangheon, K. Ildu, and C. Jeonghyeon, “The Doherty power amplifier,” IEEE Microwave Mag., vol. 7, no. 5, pp. 42–50, 2006. [15] T. Shi, 50 V LDMOS Products For Broadcast Applications, ed. Austin, TX: Freescale Semiconductor, Aug. 2010. [16] “UHF Power LDMOS transistor optimized for Doherty solutions,” 2015. [Online]. Available: http://www.nxp.com/products/ rf/transistors/power_transistors/broadcast/470_860_mhz_uhf_ broadcast/BLF888B.html. [17] “R&S THU9 UHF Transmitter Family for TV,” 2015. [Online]. Available: http://www.rohde-schwarz.com/us/product/thu9productstartpage_63493-11260.html [18] B. Kim, “Advanced linear PA architectures for handset applications”, Proc. 2013 IEEE Int’l Wireless Symp., Apr. 2013. [19] M. Gaynor, former Motorola engineer, private communications. [20] A. M. M. Mohamed, S. Boumaiza, and R. R. Mansour, “Doherty power amplifier with enhanced efficiency at extended operating average power levels,” IEEE Trans. Microwave Theory Tech., vol. 61, no. 12, pp. 4179–4187, 2013. [21] J. Kang, D. Yu, K. Min, and B. Kim, “A ultra-high PAE Doherty amplifier basedon 0.13-um CMOS process,” IEEE Microwave Wireless Compon. Lett., vol. 16, no. 9, pp. 505–507, 2006. [22] D. Kang, K. Dongsu, Y. Cho, P. Byungjoon, J. Kim, and B. Kim, “Design of bandwidth-enhanced Doherty power amplifiers for handset applications,” IEEE Trans. Microwave Theory Tech., vol. 59, no. 12, pp. 3474–3483, 2011. [23] C. Yunsung, K. Daehyun, K. Jooseung, M. Kyunghoon, P. Byungjoon, and K. Bumman, “Linear Doherty power amplifier with an enhanced back-off efficiency mode for handset applications,” IEEE Trans. Microwave Theory Tech., vol. 62, no. 3, pp. 567–578, 2014. [24] R. S. Pengelly, S. M. Wood, J. W. Milligan, S. T. Sheppard, and W. L. Pribble, “A review of GaN on SiC high electron-mobility power transistors and MMICs,” IEEE Trans. Microwave Theory Tech., vol. 60, no. 6, pp. 1764–1783, 2012. [25] V. Camarchia, M. Pirola, R. Quaglia, J. Seunghoon, C. Yunsung, and K. Bumman, “The Doherty power amplifier: Review of recent solutions and trends,” IEEE Trans. Microwave Theory Tech., vol. 63, no. 2, pp. 559–571, 2015. [26] A. Grebennikov, RF and Microwave Power Amplifier Design, 2nd ed. New York: McGraw-Hill, 2015. [27] J. Mietzner, P. Colantonio, F. Giannini, R. Giofrè, and L. Piazzon, “The AB-C Doherty power amplifier. Part I: Theory,” Int. J. RF Microwave Comp. Aided Eng., vol. 19, no. 3, pp. 293–306, Nov. 2009. [28] F. H. Raab, “Efficiency of Doherty RF power-amplifier systems,” IEEE Trans. Broadcast., vol. BC-33, no. 3, pp. 77–83, 1987. [29] M. Iwamoto, A. Williams, C. Pin-Fan, A. Metzger, L. E. Larson, and P. M. Asbeck, “An extended Doherty amplifier with high efficiency over a wide power range,” IEEE Trans. Microwave Theory Tech., vol. 49, no. 12, pp. 2472–2479, 2001. [30] R. S. Embar, W. Lu, K. Jangheon, C. Dragon, and G. Tucker, “A 400 W 2-way asymmetrical Doherty PA with 50% efficiency based on second-generation Airfast LDMOS technology,” in Proc. IEEE Topical Conf. Power Amplifiers Wireless Radio Applications, 2015, pp. 1–3. [31] K. Jangheon, B. Fehri, S. Boumaiza, and J. Wood, “Power efficiency and linearity enhancement using optimized asymmetrical Doherty power amplifiers,” IEEE Trans. Microwave Theory Tech., vol. 59, no. 2, pp. 425–434, 2011. [32] Y. Youngoo, C. Jeonghyeon, S. Bumjae, and B. Kim, “A fully matched N-way Doherty amplifier with optimized linearity,” IEEE Trans. Microwave Theory Tech., vol. 51, no. 3, pp. 986–993, 2003. [33] L. Yong-Sub, L. Mun-Woo, K. Sang-Ho, and J. Yoon-Ha, “Highly linear and efficient asymmetrical Doherty power amplifiers with adaptively bias-controlled predistortion drivers,” in IEEE MTT-S Int. Microwave Symp. Digest, 2009, pp. 1393–1396. [34] T. Kitahara, T. Yamamoto, and S. Hiura, “Asymmetrical Doherty amplifier using GaN HEMTs for high-power applications,” in Proc. IEEE Topical Conf. Power Amplifiers Wireless Radio Applications, 2012, pp. 57–60. February 2016 [35] X. Jing, Y. Mengsu, and Z. Xiaowei, “Linearized asymmetrical GaN Doherty power amplifier with 100 MHz instantaneous bandwidth at 3.5GHz,” in Proc. IEEE MTT-S Int. Microwave Workshop Series RF Wireless Technologies Biomedical Healthcare Applications, 2013, pp. 1–3. [36] S. Junghwan, K. Ildu, M. Junghwan, L. Juyeon, and B. Kim, “A highly efficient asymmetric Doherty Power Amplifier with a new output combining circuit,” in Proc. IEEE Int. Conf. Microwaves, Communications, Antennas Electronics Systems, 2011, pp. 1–4. [37] C. Ma, W. Pan, and Y.-X. Tang, “Design of asymmetrical Doherty power amplifier with reduced memory effects and enhanced backoff efficiency,” Prog. Electromagn. Res. C, vol. 56, Mar., pp. 195–203, 2015. [38] M. Özen and C. Fager, “Symmetrical doherty amplifier with high efficiency over large output power dynamic range,” in Proc. IEEE MTT-S Int. Microwave Symp., 2014, pp. 1–4. [39] M. Özen, K. Andersson, and C. Fager, “Symmetrical Doherty power amplifier with extended efficiency range,” IEEE Trans. Microwave Theory Tech., submitted for publication. [40] K. Ildu, C. Jeonghyeon, S. Hong, K. Bumman, Y. W. Young, S. P. Cheon, and K. Bumman, “Highly linear three-way Doherty amplifier with uneven power drive for repeater system,” IEEE Microwave Wireless Compon. Lett., vol. 16, no. 4, pp. 176–178, 2006. [41] K. J. Cho, W. J. Kim, S. P. Stapleton, J.-H. Kim, B. Lee, and J. J. Choi, “Design of N-way distributed Doherty amplifier for WCDMA and OFDM applications,” Electron. Lett., vol. 43, no. 10, pp. 577–578, 2007. [42] J. Moon, J. Kim, I. Kim, J. Kim, and B. Kim, “Highly efficient three-way saturated Doherty amplifier with digital feedback predistortion,” IEEE Microwave Wireless Compon. Lett., vol. 18, no. 8, pp. 539–541, 2008. [43] H. Golestaneh, F. A. Malekzadeh, and S. Boumaiza, “An extended-bandwidth three-way Doherty power amplifier,” IEEE Trans. Microwave Theory Tech., vol. 61, no. 9, pp. 3318–3328, 2013. [44] N. X. Anh, G. Junqing, and R. Negra, “Design of a broadband three-way sequential Doherty power amplifier for modern wireless communications,” in Proc. IEEE MTT-S Int. Microwave Symp., 2014, pp. 1–4. [45] A. Grebennikov, “A high-efficiency 100-W four-stage Doherty GaN HEMT power amplifier module for WCDMA systems,” in IEEE MTT-S Int. Microwave Symp. Digest, 2011, pp. 1–4. [46] R. A. Beltran and F. H. Raab, “VHF Doherty amplifier with GaN FETs and independent drive-signal control,” in IEEE MTT-S Int. Microwave Symp. Digest, 2011, pp. 1–3. [47] R. Darraji and F. M. Ghannouchi, “Digital Doherty amplifier with enhanced efficiency and extended range,” IEEE Trans. Microwave Theory Tech., vol. 59, no. 11, pp. 2898–2909, 2011. [48] R. Darraji, F. M. Ghannouchi, and O. Hammi, “A dual-input digitally driven Doherty amplifier architecture for performance enhancement of Doherty transmitters,” IEEE Trans. Microwave Theory Tech., vol. 59, no. 5, pp. 1284–1293, 2011. [49] C. M. Andersson, D. Gustafsson, J. C. Cahuana, R. Hellberg, and C. Fager, “A 1–3-GHz digitally controlled dual-rf input poweramplifier design based on a Doherty-outphasing continuum analysis,” IEEE Trans. Microwave Theory Tech., vol. 61, no. 10, pp. 3743–3752, 2013. [50] D. Gustafsson, C. M. Andersson, and C. Fager, “A modified Doherty power amplifier with extended bandwidth and reconfigurable efficiency,” IEEE Trans. Microwave Theory Tech., vol. 61, no. 1, pp. 533–542, 2013. [51] M. J. Pelk, W. C. Neo, J. R. Gajadharsing, R. S. Pengelly, and L. C. N. de Vreede, “A high-efficiency 100-W GaN three-way Doherty amplifier for base-station applications,” IEEE Trans. Microwave Theory Tech., vol. 56, no. 7, pp. 1582–1591, 2008. [52] J. C. Cahuana, P. N. Landin, D. Gustafsson, C. Fager, and T. Eriksson, “Linearization of dual-input Doherty power amplifiers,” in Proc. Int. Workshop Integrated Nonlinear Microwave Millimetre-wave Circuits, 2014, pp. 1–3. [53] A. M. M. Mohamed, S. Boumaiza, and R. Mansour, “Reconfigurable Doherty amplifier for efficient amplification of signals with variable PAPR,” in IEEE MTT-S Int. Microwave Symp. Digest, 2013, pp. 1–3. 57 [54] D. Gustafsson, J. C. Cahuana, D. Kuylenstierna, I. Angelov, and C. Fager, “A GaN MMIC modified Doherty PA with large bandwidth and reconfigurable efficiency,” IEEE Trans. Microwave Theory Tech., vol. 62, no. 12, pp. 3006–3016, 2014. [55] P. Yunsik, L. Juyeon, K. Seokhyeon, M. Donggyu, and K. Bumman, “Analysis of average power tracking Doherty power amplifier,” IEEE Microwave Wireless Compon. Lett., vol. 25, no. 7, pp. 481–483, 2015. [56] J. Qureshi, N. Li, W. C. E. Neo, F. van Rijs, I. Blednov, and L. C. N. de Vreede, “A wide-band 20W LMOS Doherty power amplifier,” in IEEE MTT-S Int. Microwave Symp. Digest, 2010, pp. 1504–1507. [57] S. Guolin and R. H. Jansen, “Broadband Doherty power amplifier via real frequency technique,” IEEE Trans. Microwave Theory Tech., vol. 60, no. 1, pp. 99–111, 2012. [58] R. Giofre, L. Piazzon, P. Colantonio, and F. Giannini, “A distributed matching/combining network suitable for Doherty power amplifiers covering more than an octave frequency band,” in Proc. IEEE MTT-S Int. Microwave Symp., 2014, pp. 1–3. [59] M. N. A. Abadi, H. Golestaneh, H. Sarbishaei, and S. Boumaiza, “An extended bandwidth Doherty power amplifier using a novel output combiner,” in Proc. IEEE MTT-S Int. Microwave Symp., 2014, pp. 1–4. [60] J. H. Qureshi, W. Sneijers, R. Keenan, L. C .N. de Vreede, and F. van Rijs, “A 700-W peak ultra-wideband broadcast Doherty amplifier,” in IEEE MTT-S Int. Microwave Symp. Digest, 2014, pp. 1–4. [61] D. Y. T. Wu, J. Annes, M. Bokatius, P. Hart, E. Krvavac, and G. Tucker, “A 350 W, 790 to 960 MHz wideband LDMOS doherty amplifier using a modified combining scheme,” in Proc. IEEE MTT-S Int. Microwave Symp., 2014, pp. 1–4. [62] A. Grebennikov and J. Wong, “A dual-band parallel Doherty power amplifier for wireless applications,” IEEE Trans. Microwave Theory Tech., vol. 60, no. 10, pp. 3214–3222, 2012. [63] R. Giofre, L. Piazzon, P. Colantonio, and F. Giannini, “A closed-form design technique for ultra-wideband Doherty power amplifiers,” IEEE Trans. Microwave Theory Tech., vol. 62, no. 12 pp. 3414–3424, 2014. [64] J. He, J. H. Qureshi, W. Sneijers, D. A. Calvillo-Cortes, and L. C. N. de Vreede, “A wideband 700W push-pull Doherty amplifier,” presented at the IEEE MTT-S Int. Microwave Symp., Phoneix, 2015. [65] R. Smith, J. Lees, P. J. Tasker, J. Benedikt, and S. C. Cripps, “A 40W push-pull power amplifier for high efficiency, decade bandwidth applications at microwave frequencies,” in IEEE MTT-S Int. Microwave Symp. Digest, 2012, pp. 1–3. [66] D. Y. T. Wu and S. Boumaiza, “A modified Doherty configuration for broadband amplification using symmetrical devices,” IEEE Trans. Microwave Theory Tech., vol. 60, no. 10, pp. 3201–3213, 2012. [67] P. Saad, P. Colantonio, L. Piazzon, F. Giannini, K. Andersson, and C. Fager, “Design of a concurrent dual-band 1.8–2.4-GHz GaNHEMT Doherty power amplifier,” IEEE Trans. Microwave Theory Tech., vol. 60, no. 6, pp. 1840–1849, 2012. [68] P. Colantonio, F. Giannini, R. Giofre, and L. Piazzon, “A design technique for concurrent dual-band harmonic tuned power amplifier,” IEEE Trans. Microwave Theory Tech., vol. 56, no. 11, pp. 2545–2555, 2008. [69] X. A. Nghiem, G. Junqing, T. Hone, and R. Negra, “Design of concurrent multiband Doherty power amplifiers for wireless applications,” IEEE Trans. Microwave Theory Tech., vol. 61, no. 12, pp. 4559–4568, 2013. [70] M. Younes, A. Kwan, M. Rawat, and F. M. Ghannouchi, “Linearization of concurrent tri-band transmitters using 3-D phasealigned pruned Volterra model,” IEEE Trans. Microwave Theory Tech., vol. 61, no. 12, pp. 4569–4578, 2013. [71] L. Ding, Y. Zigang, and H. Gandhi, “Concurrent dual-band digital predistortion,” in IEEE MTT-S Int. Microwave Symp. Digest, 2012, pp. 1–3. 58 [72] S. A. Bassam, C. Wenhua, M. Helaoui, F. M. Ghannouchi, and F. Zhenghe, “Linearization of concurrent dual-band power amplifier based on 2D-DPD technique,” IEEE Microwave Wireless Compon. Lett., vol. 21, no. 12, pp. 685–687, 2011. [73] D. Gustafsson, C. M. Andersson, and C. Fager, “An analysis of the suitability of using CW-theory when designing Doherty PAs for wideband or concurrent multi-band operation,” in Proc. European Microwave Conf., 2013, pp. 287–290. [74] A. M. M. Mohamed, S. Boumaiza, and R. R. Mansour, “Reconfigurable Doherty power amplifier for multifrequency wireless radio systems,” IEEE Trans. Microwave Theory Tech., vol. 61, no. 4, pp. 1588–1598, 2013. [75] A. M. M. Mohamed, S. Boumaiza, and R. R. Mansour, “Electronically tunable Doherty power amplifier for multi-mode multi-band base stations,” IEEE Trans. Circuits Syst. I: Reg. Papers, vol. 61, no. 4, pp. 1229–1240, 2014. [76] W. M. Gaber, P. Wambacq, J. Craninckx, and M. Ingels, “A CMOS IQ Digital Doherty Transmitter using modulated tuning capacitors,” in Proc. European Solid-State Circuits Conf., 2012, pp. 341–344. [77] H. Song, S. Kousai, S. P. Jong, O. L. Chlieh, and W. Hua, “Design of a transformer-based reconfigurable digital polar Doherty power amplifier fully integrated in bulk CMOS,” IEEE J. Solid-State Circuits, vol. 50, no. 5, pp. 1094–1106, 2015. [78] H. Song, S. Kousai, and W. Hua, “Antenna impedance variation compensation by exploiting a digital Doherty power amplifier architecture,” IEEE Trans. Microwave Theory Tech., vol. 63, no. 2, pp. 580–597, 2015. [79] A. Agah, H.-T. Dabag, B. Hanafi, P. M. Asbeck, J. F. Buckwalter, and L. E. Larson, “Active millimeter-wave phase-shift Doherty power amplifier in 45-nm SOI CMOS,” IEEE J. Solid-State Circuits, vol. 48, no. 10, pp. 2338–2350, 2013. [80] C. F. Campbell, K. Tran, M.-Y. Kao, and S. Nayak, “A K-Band 5W Doherty amplifier MMIC utilizing 0.15μm GaN on SiC HEMT technology,” in Proc. IEEE Compound Semiconductor Integrated Circuit Symp., 2012, pp. 1–4. [81] E. Kaymaksut and P. Reynaert, “Transformer-based uneven Doherty power amplifier in 90 nm CMOS for WLAN applications,” IEEE J. Solid-State Circuits, vol. 47, no. 7, pp. 1659–1671, 2012. [82] I. Aoki, S. D. Kee, D. B. Rutledge, and A. Hajimiri, “Fully integrated CMOS power amplifier design using the distributed active-transformer architecture,” IEEE J. Solid-State Circuits, vol. 37, no. 3, pp. 371–383, 2002. [83] E. Kaymaksut and P. Reynaert, “3.4 A dual-mode transformerbased doherty LTE power amplifier in 40nm CMOS,” in IEEE Int. Solid-State Circuits Conf. Digest Technical Papers, 2014, pp. 64–65. [84] E. Kaymaksut and P. Reynaert, “A 2.4 GHz fully integrated Doherty power amplifier using series combining transformer,” in Proc. European Solid-State Circuits Conf., 2010, pp. 302–305. [85] Z. Chenxi, P. Byungjoon, and K. Bumman, “Complementary metal-oxide semiconductor doherty power amplifier based on voltage combining method,” IET Microwaves, Antennas Propagat., vol. 8, no. 3, pp. 131–136, 2014. [86] E. Kaymaksut, Z. Dixian, and P. Reynaert, “Transformer-based Doherty power amplifiers for mm-wave applications in 40-nm CMOS,” IEEE Trans. Microwave Theory Tech., vol. 63, no. 4, pp. 1186– 1192, 2015. [87] S. Afsardoost, T. Eriksson, and C. Fager, “Digital predistortion using a vector-switched model,” IEEE Trans. Microwave Theory Tech., vol. 60, pp. 1166–1174, 2012. February 2016