Structured LNA Design for Next Generation Mobile Communication

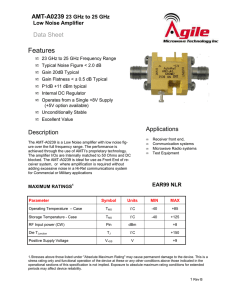

advertisement