MOSFET Amplifiers and High

advertisement

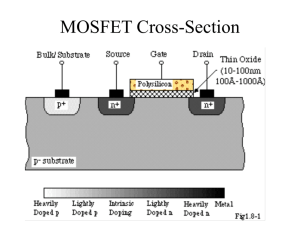

MOSFET Amplifiers and High-Frequency Performance ■ In many applications, MOSFET is used as a linear (small-signal) amplifier ■ A small signal equivalent circuit for MOSFET is needed to analyze the MOSFET frequency performance. Small-Signal equivalent circuit: ■ The equivalent circuit is constructed from the basic MOSFET geometry ■ Resistance and capacitances are incorporated Input and output signals are assumed small as compared to the steady-state DC current and voltage (operating point) Operating point is based on the MOSFET I-Vs and circuit conditions 1 MOSFET amplifier: low operating frequencies Simple FET amplifier circuit: Δ VL = Δ I × RL Voltage gain KV = Δ VL / Δ VG = (Δ I × RL) / Δ VG KV = (Δ I / Δ VG) × RL = gm × RL The larger the transconductance gm = ΔI / ΔVG, the higher is the voltage gain KV gm is maximal in the saturation regime, i.e. for VD > VD sat ΔIS ΔI1 In the amplifier circuits, FETs usually work in the saturation regime, In this regime, current DOES NOT depend on drain voltage. Current is the function of the GATE VOLTAGE ONLY. 2 MOSFET operating point: Effect of Load Resistance on the output Current amplitude 10 9 8 VG = 4 V 7 RL 3V ID, mA 10V 6 5 VG = 3 V 4 3 VG = 2 V 2 Consider the circuit with the drain bias VDD= 10 V and the gate bias VGG = 3 V ; VG = 1 V 1 0 0 2 4 6 8 10 VD, V 1. Load resistance RL = 5 kOhm Op. point: VD ≈ 1.2 V; ID ≈ 1.8 mA; gm1 ≈ (2-1.5)mA/(4-2)V ≈ 0.25 mA/V; 2. Load resistance RL = 0.6 kOhm Op. point: VD ≈ 6.8 V; ID ≈ 4.5 mA; gm2 ≈ (7-2.4)mA/(4-2)V ≈ 2.3 mA/V; 3 In MOSFET amplifiers, the operating point is normally in the saturation region MOSFET Transfer Characteristics In saturation regime, the drain current does not depend on the drain voltage 10 Saturation current, mA 9 8 VG = 4 V 7 ID, mA 6 5 VG = 3 V 4 3 2 VG = 2 V 1 VG = 1 V 0 0 2 4 6 8 10 10 9 8 7 6 5 4 3 2 1 0 -1 VD > 7 V 0 1 VD, V 2 VG, V 3 4 The dependence IDsat (VG) is called the TRANSFER CHARACTERISTIC of MOSFET 4 MOSFET amplifier: high operating frequencies S D G Cgd Cgs rs rd gmVgs ΔIS ΔI1 Gate to drain capacitance G D Cgd rd Drain series Cgs Gate to source capacitance Input signal S resistance gmVgs gds rs Source series resistance Slope of ID vs Vds Output signal 5 G D Cgd rd Cgs gds gmVgs rs S Simplified equivalent circuit diagram Cgd + + + vi – v gs – g C gs ds vo Assuming rd, rs=0 gm v gs – 6 MOSFET Gain • voltage gain Cgd Id I(Cgd) + + + vi – Input voltage vi = vgs Output voltage vo = voltage across gds v gs – g C gs ds vo gm v gs – vo can be found using superposition. 1) Assume vi = 0. The output voltage component is v01 The output current id = i(gds)+i(Cgd) i(gds) = v01 ×gds; i(Cgd) = v01 ×jωCgd From this, id = v01 ×(gds +jωCgd); On the other hand, id = - gmvgs Substituting id , we obtain: - gmvgs = v01 ×(gds + jωCgd); − gm v01 = vgs g ds + jωCgd 7 MOSFET Gain 2) Now, turn off the current gmvgs • voltage gain The output voltage component is v02 The voltage across gds = 1/rds: Cgd + + vi v gs – – g C gs ds + v02 = vi × rds/(rds + 1/jωCgd) = vo vi × rdsjωCgd/(jωCgdrds + 1) = vi × jωCgd/(jωCgd + 1/rds) = gm v gs – vi × jωCgd/(jωCgd + gds); v02 = jωCgd g ds + jωCgd vgs The total output voltage, v0 = v01 + v02: − gm v01 = vgs g ds + jωCgd v0 = − g m + jωCgd g ds + jωCgd vgs 8 MOSFET Gain • voltage gain The voltage gain: Cgd + + + vi – v gs – g ds C gs vo gm v gs – v0 − g m + jωCgd Av = = vgs g ds + jωCgd The gate - drain capacitance is very low in the saturation region. Hence, v0 −gm Av = ≈ vgs g ds + jωCgd The voltage gain decreases with frequency when Corresponding characteristic frequency: At frequencies f > fv −gm Av ≈ jωCgd fv ≈ ωCgd ≈ g ds ; g ds 2π Cgd 9 MOSFET Gain • short circuit current gain Output current, iL = i0 = - gmvgs Cgd + + + vi – g v gs vo ds C gs – gm v gs – Input current, ii = i (Cgs)+ i(Cgs) = = vi × jω Cgs + vi × jω Cgd = = vi × jω (Cgs + Cgd); Also note that vi = vgs; Therefore: ii = vi × jω (Cgs + Cgd); Cgd + vi – + v gs – The current gain: Ai = i0/ii = iL/ii gm v gs Cgs iL iL − gm Ai = = ii jω Cgs + Cgd ( ) 10 MOSFET current cutoff frequency fT fT is the frequency at which the modulus of the short circuit current gain is unity From: iL − gm Ai = = ii jω Cgs + Cgd ( ) fT = ( gm 2π C gs + Cgd ) fT estimation Assume that Cgs + Cgd ~ Ci where Ci = εiWL/di is the gate oxide capacitance. Transconductance, gm Consider short-gate MOSFETs at high drain voltage. In short-gate devices, the electron velocity is saturated: Id = q nsvsW The transconductance: gm = dId/dVg ∂I d ∂ns gm = =q vsW ∂Vg ∂Vg 11 MOSFET current cutoff frequency fT Induced sheet carrier density in MOSFETs (see lecture #18): ci Ci ns = (VGS − VT ) = (VGS − VT ) q qWL where W is the MOSFET width and L is the gate length From this, ⎧ Ci ⎫ ∂I d ∂ns gm = vsW = q ⎨ =q ⎬ vsW ∂Vg ∂Vg ⎩ qWL ⎭ Ci vs gm = L The cutoff frequency becomes: fT = gm Ci vs v = = s 2π ( Cgs + Cgd ) 2π LCi 2π L 12 gm Ci vs vs fT = = = 2π ( Cgs + Cgd ) 2π LCi 2π L Note that, L/vs = ttr , the electron transit time under the gate Using this, fT = 1/ 2πttr Practical cut-off frequency must also include the parasitic and fringing capacitances, Cp, which add to the gate capacitance: fT = ( gm 2π C gs + Cgd + C p ) 13 Maximum oscillation frequency, fmax The cutoff frequency fT is a characteristic of the intrinsic transistor (without parasitic series resistances). fmax is the characteristic of the extrinsic device (which includes series source, drain, input, and gate resistances, Rs, Rd, Ri, and Rg fmax is defined as the frequency at which the power gain of the transistor is equal to unity under optimum matching conditions for the input and output impedances. Simplified expression for fmax is given by: fmax ≈ fT r + fT τ where In MOSFETs with small parasitic resistances, RS, Ri and Rd ≈ 0 R R d C gd g + Gate v gs – g C Drain ds gs gm v gs R i R s Source r = gds (Rs + Ri + Rd ) f max ≈ τ = 2π RgCgd. fT fT = 2π Rg Cgd f Tτ 14