Programmable Cellular Logic Arrays by Richard G. Shoup Computer

advertisement

Programmable

Cellular

Logic

Arrays

by

Richard

G.

Shoup

Computer

Science

Department

Carnegie-Mellon

University

Pittsburgh,

Pennsylvania

March,

1970

Submitted

in partial

for the

to Carnegie-Mellon

fulfillment

of the

_egree

of Doctor

of

University

requirements

Philosophy

This

work

was supported

by the Advanced

Research

Projects

of

the Office

of the Secretary

of Defense

(F_620-&7-C-0058)

is monitored

by the Air

Force

Office

of Scientific

Research.

document

has been approved

for public

release

and sale;

its

bution

is unlimited.

Ageacy

and

This

distri-

-il-

Carnegie-Mellon

Programmable

University

Cellular

Richard

Logic

G.

Arrays

Shoup

Abstract

In

recent

designer

years,

of

computing

batch-fabricate

large

semiconductor

of

:ident ical

cells.

and

customizing

more

to

the

may

number

perform.

presence

is

numerous

have

logic

manufacture.

range

of

presented

shown

to

for

manufacturing

and

be

creating

the

arrays

arrays

by

a

physical

advantages

manufacture,

to

their

they

generality,

are

designed

different

examples

analyzed.

One,

effective

shift

defects.

of

tolerance.

which

more

of

by parameter

aften

according

tasks

a single

cellular

Potential

failure

the

using

than

variability

enhanced

on

to

investigated

by

rather

the

ability

determined

cell,

cla_sified

are

techniques

of

are

the

the

considers

significantly

arrays

array,

conventional

be

Two

low-generality

register

and

and

digital

functional

testing,

Arrays

in

during

include

efficient

of

provided

components

researchers

functions

gates

operation

logic

dissertation

cell

logic

technique

i.e.,

kinds

This

individual

flip-flops

this

various

with

of

Numerous

have

advances

hardware

numbers

slice.

synthesis

whose

technological

registers

a

of

shift

than

some

in

the

-iii-

new

important

cell

in

schema

synthesis

for

are

presented

design

the

target

of

central

programmable

using

control

is

a pp roach.

processoc

logic

detail

introduced

the

Techniques

and

is

these

compared

class

of

tasks.

control

logic

A

to

a

the

As

is

small

techniques.

more

exhibits

properties

high-generality

improving

of

array.

which

This

match

an

functions.

between

example,

the

approached

computer

method

conventional

in

is

an

array

problem

terms

of

implemented

of

synthesizing

microprogramming

a

in

-iv-

_C know ledge

I

and

many

wish

guidance

the

also

this

important

help

personal

this

work.

in

support

were

indebted

topic

early

Finally,

her

Professor

suggestions

am

suggested

thank

during

helpful

I

to

to

and

special

typing

during

C.

His

of

this

Bell

enthusiastic

Dr.

T.

Jesse

the

Quatse,

guidance

his

and

who

advice

and

his

originally

direction

during

work.

are

due

proofreading

long

for

interest

appreciated.

thanks

and

Gordon

sincerely

provided

phases

me n ts

effort.

to

my

and

wife,

for

Nancy,

her

for

continuing

--V--

Table

of

Contents

A b s tract

ii

Acknowledgements

i v

Table

List

of

of

Table

I.

Contents

v

Tables

of

vi

Figures

vii

Introduction

1

I. I Background

2.

and

1.2

programmable

1.3

The

1.4

Overview

logic

n-space

of

of

Rssumptions

3.

S.

2.3

Failure

3. I

The

3.2

A shift

and

logic

problem

7

arrays

18

the

standard

logic

of

testing,

33

system

35

defects

and

42

diagnosability

50

arrays

register

High-generality

56

arrays

58

array

82

arrays

4. I

A previous

PL

4.2

High

properties

4.3

Connection

4.4

Cell

R ef er en ce s

LSI

topics

arithmetic/parity

array

array

102

and

a generic

cell

type

107

114

functions

122

application

and

101

functions

nucleus

Conclusions

the

29

distribution

modes,

Low-generality

a. 5 An

5.

and

12

work

preliminary

2. I Evaluations

Yields

and

cellular

this

and

2.2

definitions

and

further

analysis

research

138

169

176

-vi-

List

3.1

Evaluation

4.1

The

4.2

Three-variable

4.3

Overlapped

_.4

Inbus

4.5

States

of

equivalence

and

of

At

arrays

c.l_ss

of

function

microco_e

outbus

the

for

signals

.Rosin

of

Tables

A2

76

AAL_^C

127

classes

129

and

Rosin

for

machine

machine

the

Rosin

156

machine

159

160

-vii-

Table

1.1

Idealized

1.2

Lewel

1.3

Several

fabrication

of

of

integration

vs.

interconnection

2. I Standard

set

of

2.2

Examples

of

cell

2.3

Representatiwe

2.4

Experimental

2.5

Cluster

2.6

A special

3.1

Array

3.2

Complete

3.3

Primary

3.4

Secondary

3.5

control

3.6

Functional

3.7

Complete

3.8

Primary

3.g

Secondary

Figures

logic

blocks

number

of

4

unique

parts

structures

logic

36

complexity

cell

defects

form

yield

on

of

39

Petritz

vs.

cell

data

size

a hypothetical

cell

9

24

elements

slice

case

of

45

46

slice

failure

49

53

AI

61

cell

AI

62

functions

of

functions

logic

of

of

AI

cell

array

diagrams

cell

cell

64

AI

65

kl

of

66

array

A2

69

A2

functions

70

of

functions

of

42

of

array

71

A2

72

3.10

Control

logic

3.11

Minimal

synthesis

of

the

primary

3.12

Minimal

synthesis

of

the

secondary

3.13

Functional

3. lq,

Cell

3.15

Example

of

3.16

Control

logic

diagram

of

A2

73

array

S1

$I

functions

functions

77

78

83

84

array

of

$1

array

85

SI

87

-viii-

3.17

Shift

register

4.1

Four

cells

4.2

Complete

4.3

_

flip-flop

4.4

A

high-g

4.5

Adjacent

4.6

Parity

of

4.7

Busing

schemes

4.8

Functions

4.9

Cell

array

in the

Wahlstrom

Wahlstrom

in

PL

cell

array

103

104

Wahlstrom

array

106

schema

112

1-outpl, t cells

116

]-input

of

g]

cell

the

paths

examples

in

arraTs

118

120

3 variables

function

126

FI

131

4. 10

Cell

function

F2

131

4.11

Cell

function

F3

132

4.12

Cell

function

F4

132

4.13

Cost

vs.

number

4.14

Data

and

control

_.15

Control

4.]6

Functional

4.17

C section

of

cell

GI

147

4.18

F section

of

cell

GI

I_8

4.19

Control

_.20

Detail

of

control

parameters

4.21

Timing

of

typical

GI

_.22

Block

4.23

Flowchart

a.2.

PL control

of

functions

for

example

cells

submachines

139

machines

diagram

parameter

diagram

and

of

141

of

cell

section

logic

Rosin

for

G]

of

146

G1

cell

of

cell

I_8

GI

150

chain

153

machine

instruction

array

134

Rosin

set

155

for

machine

Rosin

machine

157

161

--I--

1

Chapter

Introduction

1 . Introduction.

The

design

rules

are

times,

advanced

that

constantly

real

race

to

make

LSI

structure

a

can

design

in

remainder

appropriate

to

and

of

section

this

throughout

of

relate

thi rd

to

to

summarizes

study.

this

the

ThroL1gh

study

arrays,

this

set

the

Related

manner

in

far

the

between

and

what

of

a type

our

of

dissertation

some

define

all

work

work

the

important

of

concept

aspects

to

cellular

which

will

be

of

programmable

circuitry

attempts

of

at

large-scale

thus

supply

integrated

chapter.

of

Realization

section

has,

neglected

gap

chapter

systems.

ground

gap.

this

it

whose

devious

advent

can

that

large-scale

structure

of

narrowing

a

been

largest

logic

task

:in such

The

use.

sections

a

Technology

often

the

programmable

two

The

interrelating

last

opened

computing

terms

has

effectively

logic

of

it

and

capabilities

contributes

first

pace

developments.

has

is

changing.

rapid

of

new

called

discussed.

The

of

programmable

logic

such

hardware

rapidly

manufacturing

The

the

use

techniques

hopefully

of

and

circuitry

our

design

at

computing

understanding

integrated

what

of

is

impart

logic

also

some

arrays.

follows

in

the

cited

whenever

-12-

I. I Background

In

strong

resulting

or

density

on

from

integrated

gates

the

have

a

had,

and

square

are

years

one

It

is

million

ago,

all

to

and

with

etc.

densities

further

of

believed

per

on

machines

resistors,

gates

the

continue

designer

available

inch.

in

fabrication

will

systems

few

made

batch

transistors,

chips

than

been

and

logical

discrete

per

more

has

only

circuit

more

of

trend

hardware,

constructed

10,000

a

effect

advances

miniaturization

This

computing

Today,

large

with

components.

a

w ere

years,

associated

logic

have,

definitions.

recent

technology

of

and

that

square

inch

decrease

in

is

possible.

For

relative

this

the

cost

would

If

were

(including

with

benefits

can

various

feasible.

in

logic

elements

has

only

all

applications

of

zero

Examples

terminals

central

such

as

lower

in

line

and

cost

buffering

In

not

and

pre-editing

vast

of

be

places

been

and

logic

reductions

of

system

a

few

carries

particular,

caches

Use

the

cost

various

have

cost

computer

only

circuitry

scratchpads,

permit

of

the

itself,

overall

would

at

by

present-day

total

logic

would

can

a

support)

system

processors.

these

in

the

potential.

the

which

Taken

in

the

and

muclh greater

are

occurred.

decrease

cost,

, this

included

significant

circuitry

software,

organizations

in

small

logic

at

However

be

remote

memories

a

the

hardware,

lower.

logic

a

available

percent

it

reasons,

mean

computing.

system

of

same

more

and

in

previously

facilities

associative

circuitry

in costs

in

of

-3-

software

and

efficiency

maintenance,

at

the

same

However,

technology

•fabrication

resulted

Figure

fabricating

a

a

silicon

good

packages

wafer.

are

are

in

gives

of

and

cost

back-plane

of

to

Therefore,

some

at

least

into

testing

the

thrust

and

build

computing

the

sort

are

tested

and

retested.

a

printed

of

the

upon

is

in

of

many

(ICs),

fabricated

diced

into

Later,

on

chips.

the

board

assuming

to

good

form

a

large-volume

costs:

of

$0.002

/ circuit

$0.27

/ circuit

$0.73

/ circuit

>$2.00

/ circuit

accumulated

machine.

not

and

burden

the

used

are

circuit

assembly

final

test

are

cost

process

circuits

and

[20]{0}

the

of

testing,

1000

a

of

integrated

following

after

etc.

levels

IC after

packaging

device

test

wired

and

is

the

other

flip-flops,

breakdown

of IC after

onto

module,

proportion

benefit)

cost

of IC

dicing,

cost

a factor

or

circuits

with

design

of initial

fabrication

IC on the

slice

cost

system

fabrication

idealization

Identical

onto

production

cost

boosting

micrologic

mismatch

of

packaged

A

1968

an

gates

soldere_

in

to

module

All

chips

packaging

shows

several

module.

is

a severe

computers.

functional

Thus

progress

necessary

logic

representing

Tihe

in

1.1(a)

third-generation

each

rapid

techniques

hardware.

significantly

time.

this

has

while

Clearly,

(and

will

even

costs

not

density

of

the

(as

as

much

system

well

designer.

before

It

of

be)

IC

processing,

decreasing

ICs

of

the

in

themselves.

the

behooves

resulting

him

now

-4.-

--5--

%0

organize

his

large-scale

are

using

is

to

1.2.

logic

cellular

arrays

in

slice.

The

array.

is

determine

the

shown[24]

cell

e tc.

:is

the

particular

inputs

and

that

it

in

to

Tihere

cells

is

logic

which

reasonable

the

perform

no

function

possible

need

for

by

set

it

that

slice

dicing,

cells

the

is

are

silicon

called

a

logic

8innick[23].

of

parameters

performs

in

active.

any

packaging

array

has

been

functions

and

required

function

which

the

It

cell

Therefore,

desired

of

circuits

microcellular

choose

so

array.

the

of

on

use

process

method,

the

are

to

ways

on

survey

a

the

duplicate

pattern

area

given

outputs

by

the

excellent

later

the

conventional

set

in

the

levels

fabrication

of

to

allow

various

inherent

regular

of

time,

the

idealized

the

themselves

same

between

Each

in

an

is

synthesized

parameterized

intact.

in

the

chosen

Research

interconnections

be

some

entire

summarized

Each

an

Unlike

lend

problems

approach.

a cell.

connected

or

shows

at

match

in

a cellular

wafer

better

Section

which

and,

Some

I. I (b)

called

ways

techniques.

discussed

already

can

a

Figure

now

and

(LSl)

provide

fabrication

LSI

in

integration

technology

of

systems

the

function

array

and

and

can

then

be

used

reassembly,

-6-

The

of

parameters

ways.

The

parameterizing

within

of

each

control

the

state

by

cell.

lines

other

to

methods

programmable

date.

Institute)

will

of

outside

the

array

the

(by

discussed

logic

(PL)

presented

Wahlstrom

[ 44]

detail

in

at

4.

number

by

the

several

one

truly

literature

Stanford

Chapter

a

control

Only

the

to

enabled

I. 2 describes

in

number

memory)

via

and

parameters.)

been

a

refers

gates

function

(Section

these

loaded

Logic

cell

in

(parameter

are

array.

the

in

supplied

flip-flops

cell.

has

be

flip-flops

supplying

array

be

state

state

from

of

may

means

_etermine

logic

This

cell

programmable

from

and

each

term

These

flip-flops

connections

to

Hesearch

to

-7-

1.2

Programmable

logic

and

the

LSI

problem.

,

Efficient

hardware

requires

significant

of

raised

with

and

This

section

LSI.

respect

I. 2. I The

circuit

cost

of

of

these

testing,

etc.

circuit

is

is

due

permits

divided

among

Specialized

in

its

perform

of

16

are

4 inputs,

number

is

in

number

to

of

theoretical

partitioning

manufacturing

excess

of

the

with

and

constraints

the

major

PL

concept

some

design

current

is

issues

discussed

approaches.

to

The

associated

function.

different

functions

on

increase

plane

decrease

in

wiring,

cost

per

components

with

the

as

a

the

slice.

as

more

A device

having

101_different

back-

an

Gf

the

functions

and

decrease

densities

slice,

are

continued

packaging,

increasing

circuits

a

themselves

components.

single

of

show

components

dicing,

the

a

65,536

of

manufacturing

costs

all

onto

any

in

largely

the

absorbed

i

computing

problem.

the

total

to

a

both

functional

several

along

cost

the

be

issue

trends

in

as

applicability

each

of

of

relate

as

well

presents

Current

the

which

as

customizing

in

such

ion

in

repeatability.

The

to

problems

design,

yield

integration

considerat

These

organization,

by

large-scale

careful

machine

processor

as

of

problems.

aspects

such

usage

of

those

possible.

functions.

slice

But

slice

2

becomes

binary

inputs.

With

The

whole

to

logic

more

inputs

If

can

there

6 inputs,

more

complex

the

a

-8-

device

becomes,

given

machine.

(components

per

required

Each

for

as

inventory

affects

represents

and

the

or

costly

failures

exist,

customizing

array{2}.

A

organizing

number

and

of

could

number

Another

problem

of

process

yields

of

centimeter

distributed

different

be

done

as

quite

defect

improved

a

pattern{4}.

by

a

form

by

an

per

as

called

fact

LSI

connections

are

studying

so

are

percentages

If

this

did

not

outside

the

as

that

chip

package)

by

to

the

problem

of

minimize

the

connections[20]{3}.

issue

during

at

component

of

LSI

defect

Yields

at

manufacturing

higher

levels

make

high

customization

an

of

10

of

entire

consider

these

each

the

the

currently

densities

fashion,

concerns

can

Since

of

the

manufacture.

leads

satisfactory.

quasi-random

costs

is

significant

problem

faulty

and

sizes[l}.

design

to

after

occurring

_anufacturers

a

devices

tradeoff

customizing

serious

one

This

designs

the

percent

in

machine

of

20

various

outputs

researchers

form

because

faulty.

be

intra-part

more

of

initial

within

integration

(CPUs)

200

and

a

device

to

Defects

of

different

compounded

and

parts

yield.

are

integration

of

level

of

for

150

partitioning

unique

is

responsible

about

used

problem.

and

during

be

number

costs.

problem

occurring

to

the

significant

part-number

are

(currently

how

units

inputs

and

likely

the

replacement

the

is

shows

processing

supplying

limitation

may

device)

customization

connections

it

1.2

customization

relatively

times

Figure

part

This

of

fewer

central

unique

well

the

the

per

chip

square

failures

slice

will

integration

which

are

have

a

levels

avoids

or

-9-

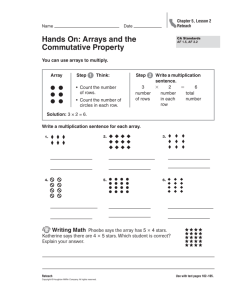

1000"

05 circuit

CPU

100

Number of

unique

parts

104 circuit

10

CPU

0 3 circuit

1

CPU

10

100

1000

Level of integration

(circuits/part)

Figure 1.2. Level of integration

vs. number of unique parts

-10-

eliminates

the

defective

One

defec

such

technique

t-av oidance

can

discretionary

control

probing

probes.

which

are

w il I

function.

cells

plotter

and

proper

metalization

repeated

for

for

every

production

fairly

is

the

low-volume

proposed

by

method

uses

appropriate

the

tested

points

which

a set

of

cells

are

good

pattern

cells

present

which

is

slice.

The

therefore

photomasks

a

is

form

is

then

drawn

used

above

fast,

to

has

desired

a CRT

produce

sequence

been

or

the

must

inexpensive

To

and

compensate

on

to

fine

which

the

essential.

production

computer

with

to

pattern

called

under

together

are

and

is

a connection

This

made

LSI

technique,

Minnick

for

points

fuses

on

the

damage

larger-than-normal

are

of

commercial

cutpoint

be

method

date,

only

feasible

These

using

currents

has

arrays[22][21].

in

fuses

surrounding

LSI

logic,

cellular

(cutpoints)

chip.

to

slightly

actual

called

customizing

small

(without

known

of

customizing

wiring.

Another

blown

rows

slice,

of

discretionary

cells

on

is

test

generates

ones[41].

photomask

slice

determines

then

or

which

s i multa neously

various

good

defective

a

at

It

only

Extra

the

done

computer

faulty.

by

Each

it

The

connect

for

be

wiring[33].

by

wire

cells.

signal

may

circuits)

through

production

them.

which

be

been

This

paths

at

selectively

by

passing

No

examples

uses

cutpoint

1 og ic.

Both

of

the

above

approaches

are

attempts

to

minimi_e

-11-

customization

stage

in

third

costs

the

by

physically

manufacturing

approach

process.

to

thi s

int erconnec

tions

in

an

flip-flops

which,

in

turn,

state

flip-flops

advantages

of

I)

are

PL

No

discretionary

turn-around

some

mask.

P L,

2)

a

done

procedure

slow-write

hold

the

virtually

a

the

fault

these:

are

required

in

These

the

as

of

to

be

can

with

cost

and

wiring

application

avoidance

setting

Briefly,

are

need

and

cells.

savings

currents

and

the

discretionary

during

unusual

can

be

function

at

corresponding

problem

The

disturbance

mechanism

allows

yield

array

different

customizing

I)

masks

a

often

the

final

present

take

and

place

at

speeds.

The

The

be

in

no

or

by

array.

customizing

addition,

customization

element

perform

In

loss

With

functional

logic

This

time.

involves

to

the

late

functions

within

outside

a

provides

determined

gates

alterations

wiring.

be

at

logic

Cell

can

from

slice

Programmable

control

respect

physical

the

problem.

array

loaded

with

customizing

for

some

reloading

reprogrammed

to

time.

of

operation

power

the

"program

like

the

used

with

pre sen t- da y

stored-charge

is

might

much

eliminated,

later

be

PL

with

respect

to

the

are:

electrical

parameter

and

disadvantages

customizing

of

altered

initial

type

of

is

permanent.

occasionally

into

an

machines.

memory

commonly

done,

or

necessitate

This

program

a

could

loading

_ Iternatively,

element

Power

_ loss

array.

supervisor

information.

as

U

not

sight

failures

by

the

use

a

be

used

to

can

also

be

of

back-up

-12-

power

sources.

circuitry

can

remain,

some

of

2)

extra

logic

10

up

each

1

transistor

per

which

The

each

extension

small

on-site

monitored

shipping

and

be

power

required

controlled.

loading

propagation

must

of

a programmed

program

extra

is

be

slower

into

signal

LSI

problems

In

probably

often

by

Some

device.

will

introduced

gates,

significant

in

5 to

in

amount

general,

desirable.

because

paths

of

to

the

control

tions.

3)

up

small

easily

Signal

gates

i nt erconnec

of

be

however,

form

use

The

amounts

cell

or

more.

of

the

logic

can,

of

in

flip-flops,

area

some

on

the

cases,

control

lines,

slice.

be

The

increased

should

be

noted

that

this

current

trend

of

using

more

transistors

element.

gate

commonly

Many

and

use

second-generation

4

or

5

gates

5 transistors

per

a

gate

and

can

be

is

to

used

flip-flop.

of

factor

increase

maclhines

per

etc.

amount

by

It

per

ICs

state

an

make

only

Today's

6 to

8 gates

flip-flop.

In

during

addition,

run-time

would

permit

given

task.

possible

concept

a

perform

computer

Greatly

over

is

to

however,

today's

unfortunately

PL

arrays

different

to

alter

increased

beyond

functions.

:its own

efficiency

fixed-structure

the

reprogrammed

This

structure

is

machines.

scope

of

to

suit

theoretically

This

this

ability

work.

interesting

a

-13-

1.2.2

Testing.

Effective

utilization

of

distinct

LSI.

input

exhaustiwel

tested

This

is

a

gross

pads

silicon

area.

tend

A

high

the

is

make

number

of

of

of

be

best,

as

component

The

great

probing

less

researchers[1_][40]

I/3

and

and

[I]

the

the

number

of

in

order

to

current

mentioned

area

as

densities

in

Nost

technique

however.

sometimes

concern

applied

astronomical.

probing

internal

serious

integration,

must

becomes

at

Increased

to

levels

internal

method

alone

a problem

which

a slice

using

testing

At

is

patterns

T test

are

layers

testing

taken

of

more

less

are

above.

Qp

the

ICs

by

the

available

metalization

attractive.

presently

involved

....

with

the

testing

problem.

pessimistic

results

connections

only

assumed

defect

other

fixed

to

cells

concerning

at

the

structure

obscure

in

Tammacu[40]

the

some

array.

testing

edges

of

other

has

of

these

the

arrays,

faults

or

of

given

some

regular

array.

it

prevent

relatively

arrays

Because

is

using

of

possible

testing

the

for

of

some

a

-14-

Programmable

with

respect

I)

designed

in

PL

effect,

variability

and

bypass

2)

and

physical

to

logic

the

testing

Efficient

arrays.

to

allows

them

Edge

and

is

probing

of

to

possible

state

recommend

sequences

test

slice.

the

to

with

parameters

connections

permits

the

is

because

break

thoroughly

testing

advantages

it

problem:

testing

to

several

edge-testing

This

make

has

in

the

can

properly

be

circait.

disconnect

used,

This

faulty

cells

array.

elimination

of

testing

pad

area

-15-

1.2.3

Alterations

As

design

software

systems

not

a state

debugging

more

by

continual

changes

metalization

severe

on

at

higher

time

of

IC

the

be

complex,

Not

a

piece

service{5}.

point

is

much

changed

again.

_Iterations

and

difficult

with

Thus

debugging

changed

more

of

Large

where

exists.

cannot.

of

in

system

course,

chip

levels

the

often

can

more

difficult.

useful

reached

the

wiring

an

and

discovered

of

debugging

are,

Back-plane

is

years

already

complete

of

hardware.

error

given

have

more

increasingly

obscure

has

really

becomes

becomes

an

which

but

hardware

validation

hardware

Thus

repairability.

computing

infrequently,

is

and

some

the

in

difficulty

problem

becomes

integration.

•

One

assurance

approach

of

hardware.

can

to

the

circuital

are

circuits

a

crucial

Programmable

to

the

most

has

hardware

is

factor

logic

in

it

is

is

or

far

times

those

a

maximum

committed

by

not

design

building

been

shown

parallel

at

not

practical

on

models

on

laboratory

along

to

highly

Breadboard

on

propagation

thus

usually

approximating

achieve

provide

automated

simulation,

computers.

lengths

impossible

high-speed

often

wire

serial

to

before

Simulation

simulation

in

is

employing

extensive

level,

limited

that

by

Since

essentially

are

done

task.

today's

chip

be

"breadboards".

adequate

problem

correctness

including

laboratory

this

design's

This

techniques,

the

a

to

the

are

actual

bench.

these

very

IC

For

connections

design.

can

provide

the

ability

to

easily

-16-

alter

hardware

capability

greatly

problem

more

functions

and

--

and

discretionary

entire

etc.,

unit.

can

be

reliability

([41],

In

existing

levels

can

circuits,

to

this

redundancy

and

summary,

will

then,

has

the

of

be

in

to

with

be

integration

terms

make

of

failure

necessitate

replacement

majority

voting

somewhat.

been

much

potential

both

in

a

of

techniques,

Enhancement

discussed

explicitly

made

run-time

transistor

problem

not

comes

problem

single

correctness

additions

Higher

array

lessen

and

design

This

elsewhere

considered

advantages

of

here.

of

PL

over

are:

Electronic,

rather

than

physical,

customizing

and

enhancement.

2)

3)

design

A

manufacture.

the

bonus

Redundant

example)

methods

I)

yield

used

of

important

serious

cutpoint

through

for

more

repair.

or

after

improvements

more

a

time

severity

repairability.

failures

diagnosis

the

a

any

the

allows

But

variability

run-time

reduces

also

easily.

at

8ore

efficient

Functional

correction,

fault

edge-testing

variability

repairing

and

after

and

fault

diagnosis.

manufacture,

machine

including

restructuring.

-17-

The

discussed

following

disadvantages

are

inherent

to

PL

here:

I)

Significantly

increased

amounts

2)

Propagation

delays

are

])

Customizinq

is

physically

of

logic

are

sometimes

r eq uired.

not

increased

5y

added

permanent.

gates.

as

-18-

I. 3 The

n-space

We

arrays

has

by

have

on

these

points

In

efforts

be

of

only

be

the

choice

thelr

Thus

the

an

uncharted

section

described

of

in

any

of

abstract

will

be

discussions

characteristic

properties

the

unless

cellular

cases,

logic

emphasis

uniqueness

has

such

a

which

been

of

the

given

to

comparison

exist

are

is

mainly

attempt

to

relate

hypot[hetical

A

some

few

rough

What

is

to

serve

space

of

of

some

of

these

dimensions

these

of

dimensions

measure,

but

at

as

dimensions,

the

can

most

really

issue

an

can

here

is

not

precision.

axes

the

will

by

characteristics

these

attention

designs

arrays.

qualitatively.

quantitative

in

we

of

space.

several

logic

of

and

other

array

number

most

little

each

quantitatively

meaningful

a

in

cellular

As

noted

Usually

describing

grasped

In

a

capabilities

to

this

by

n-space

the

arrays.

referenced

arrays

unavoidable{6}.

isolated

far

question.

relating

logic

researchers.

placed

in

cellular

thus

previous

been

array

of

the

ca n

array.

orthogonal.

which

be

follow.

examined

this

Many

kind,

not

dependencies

Indeed,

it

independent

is

ly

all

will

seldom

of

the

be

that

other

-19-

].3. ] Generality.

This

work.

the

primary

Generality

variety

given

one

is

of

functions

various

sets

level

sense,

array

we

a

choose

to

characteristics

strong

customization

of

problem

of

the

generality

no

variability

the

array

of

inputs

and

for

of

generality

to

dimension

the

t hese

devices

is

any

and

strongly

range,

the

is

various

all

(i.e.,

any

tlhe other

exists

a

range

of

part-number

At

fixed

extreme

one

or

extreme

function

are

with

arrays

efficiently.

the

In

with

the

1.2.1.

simple

to

states.

there

the

and

performing,

all

addition,

functions

related

of

associated

and

this

number,

pervades

other

orient

control

strongly

the

the

we

capable

Section

have

At

to

generality

in

we

which

In

between

discussed

around

property

here.

all.

perform

is

This

scale,

at

refers

which

mentioned

a pp lica bill ty )

this

array

create.

relationship

attempt

an

of

dimension

which

Clearly,

programmability

of

the

array.

In

t he

attempting

real-world

usefulness

course,

of

a

units

have

power

to

however,

certain

the

in

is

which

functions

general

the

high

a

measure

costs

highly

efficiently

to

we

parallel

generate.

but

it

can

sense.

The

generality

in

they

structures.

that

computer.

efficient

on

the

few

IV[3]

are

each

The

aggregate

a class

of

neglect

machine

perform

ILLIAC

cannot

efficiency

A Turing

real-world

really

we

represent

machine

general-purpose

only

generality,

and

is,

of

functions

processing

equivalent

problems

:in

machine,

having

-20-

It

speak

of

have

a very

the

by

also

means

of

other

hand,

the

a

of

this

of

any

of

the

connected

in

One

a

of

as

from

which

the

device

the

cell

real

in

cost

how

have

are

reflected

many

in

a

Chapter

4 which,

depending

their

inputs

and

upon

outputs,

being

and

cases,

goals

array

to

is

cells

grid.

the

range

of

about

as

capable

The

Increased

at

the

generality

to

the

generality

functions

the

as

functions

array

important

area,

arrays

design.

can

serve

designed

unneeded

can

the

fixed

perform.

low-generality

the

is

wide

semiconductor

design

a rectangular

required

fundamental

In

on

knowledge

to

generality

several

specific

specific

required

money,

very

goals

be

for

obtained

a

variables.

definition.

needs

be

with

match

may

structure.

cascade

device

array

ion

in

fewer

may

generality

might

the

we

high

arrays[18]

2 or

the

attain

cascade

process

task

of

designs.

time,

discuss

the

of

level

array

of

An

function

cell

of

design

lack

degrees

resulting

will

any

will

cell

that

machine.

generality

configuration

specific

a

of

Each

example

interconnect

Maitra

functions

by

from

The

The

a

yet

flexible

level

IV

in

and

general

fiKed

required

result,

at

same

power)

well

we

16

functional

may

very

approach.

goal

generality

a

ILLIAC

levels

function

structure.

example

the

various

fairly

an

one

from

cell

by

interconnection

(or

at

specific

combining

are

clear

generality

overall

On

is

be

effects

etc.

In

and

attempt

Cells

synthesize

and

and

on

generality

realized

permutations

level

the

has

Chapter

to

how

a

3,

show

these

are

presented

in

and

negations

of

many

different

-21-

functions.

I. 3.2

Size

(logical).

The

of

the

size

array

description

an

a cell

extreme,

the

large

I. 3.3

in

thr_

possible

are

IV

are

components)

obvious

general,

complex

computer

only

a regular

and

hexagon),

of

the

arrays.

more

of

can

we

are

be

and

the

parameters

can

its

say

in

that

the

functions.

thought

of

as

ways

arrange

size

the

more

At

an

one

array

o:f

geometry.

cells

where

unique

on

a plane.

by

each

its

Also,

geometries

approach

(not

regular

vertex

affects

way.

three

pattern

coverings

array

interesting

cells)

In

the

ILLIAC

(number

of

array.

is,

There

certain

cell

cells.

Array

analogous

the

(number

of

complex

very

of

These

polygons

represents

a

necessa['ily

pattern

functions

identical

correspond

to

(triangle,

cell.

interconnection

certain

to

to

The

square

geometry

possibilities

are

symmetric).

transformations

better

See

using

the

in

suited

[10]

for

hexagonal

an

to

an

-22-

1. 3.4

Cell

function.

Several

affect

be

the

properties

capabilities

possible

to

interconnection

binary

given

can

of

is

of

also

an

of

array

n-bit

full

in

each

then

be

This

be

the

complexity.

in

the

large

interacts

while

cell

number

of

For

any

which

a

cell

array.

example,

of

the

has

very

few

of

the

16

all

On

the

additions

strongly

structure.

structure

cell

number

the

functions

a flip-flop.

The

by

nearly

parallel

from

not

other

might

hand,

have

components

per

variability

of

an

cell

the

zero.

interconnect:ion

interconnection

var iables

cell.

essentiall_

dimension

also

for

fairly

of

may

a function.

the

for

function

cells it

ordered

of

of

cell

function

forms

variety

measure

and

adder

would

cell

synthesis

strictly

function

be

or

some

cell

celi[22],

designed

could

the

permits

2 variables

nucleus

including

the

useful

nucleus

(In

may

the

cutpoint

but

cell

array.

Cells

which

a

the

separate

variables,

Minnick's

functions

the

control.)

number

components

of

entirely

variables

perform

of

varies

function

with

Usually,

directly

and

in

with

several

the

the

proportion

others

density

of

number

of

to

its

-23-

1.3.5

Interconnection

Arrays

may

int erconnection

structure

any

paths

strong

through

be

that

used

in

up

as

to

and

The

and

This

a

passing

it

signal

flexibility

in

symmetry

any

the

in

(east)

and

south

last

exists

in

down

their

of

this

paths

from

and

this

direction.

Interconnection

by

Lines

wire

column,

never

which

Notice

can

left

compass

allows

only

(west)

points

by

to

neighbor

a

Figure

move"

neighbor

alternative

connections

bus.

propagating

shows

but

buses.

no

line

in

to

or

Much

1.3(c)

Each

east

nearest-neighbor

an

variables

width.

propagation

a "knight's

connections

path

Several

signals

the

via

for

Example

nearest-neighbor

use

provides

column

array

or

these

1.3.{7}

continuous

row

called

of

array.

Figure

south

by

cell

entire

the

1.3(a)

1.3(b)

west

to

a

be

grid.

connection

cell

of

will

geometry

(so_th),

to

Figure

and

and

its

Figure

a rectangular

west

--

direct

array

in

in

continue

buses,

an

bus

cell

cell

in

from

:in the

shown

a

each

The

properties

are

shall

on

along

other

among

2)

by

right

on

connection.

to

properties

direction

indicate

structure

connections

passing

on

input

We

cells

number,

graphs

directions

south

basic

complexity.

nearby

outpoint

the

The

than

other

a cell

(north).

indicate

path

effects

an

the

propagate

or

to

connection

passing

according

interest:

connections.

possible

can

of

cell

have

delineated

Three

Interconnection

given

neighbor

be

structures.

are

1)

structure.

to

more

south

complete

Figure

1.3

-24-

I

(a)

_

_"

;

dr

dr

_r

q'

_

_P

(b)

(Minnick's

T

(C)

(Minnick's cutpoint cell)

_

I

LT

_

.

I_

_

i_

IN'I

cobweb cell)

T

(complete nearest-

neighbor connections)

Figure 1.3. Several interconnection structures

-25-

may

represent

simple

one

connection

transmit

many

3)

may

permit

and

outputs

way,

bits

set

of

of

its

a

parallel

at

simply

and

Chapter

3,

register.

The

4

of

paths

to

a

the

shift

nearest-neighbor

arrays

which

simultaneously

It

should

throQgh

be

clear

a

at

the

which

whose

of

a

is

larger

cell

and

nucleus

outputs{8}.

a small

taken

Chapter

this

the

cell

and

be

forming

In

Kautz[15]

no

nucleus

In

inputs

from

of

have

may

cell,

through

inputs

register

a cell

cell.

nucleus

inputs

array

capable

might

within

the

networks

cells.

are

to

of

its

arrays

cell

with

function

control

inputs

cell

between

present

input

The

sorting

as

array

cells.

to

other

An

cell

outputs

inputs

The

thought

we

and

route

parallel.

complex

between

the

and

form

in

between

nucleus,

choose

be

data

variability.

outputs.

can

patlhs

and

inputs

to

several

paths

cell

might

cell

the

of

connections

the

Batcher[4]

of

bits

in

various

directly

all

more

Interconnection

a cell

In

or

4,

shift

from

we

several

any

I

describe

different

cell.

this

point

that

the

interconnection

•

structure

is

mentioned

here.

(COF)

to

as

the

used

arrays.

as

the

number

an

heavily

In

to

particular,

ratio

in

related

of

the

indicator

the

we

total

define

number

nucleus

or

of

design

cell

most

cell

of

the

of

the

other

cel_____l

overhead

components

function.

efficiency

dimensions

in

The

for

COF

some

factor

the

cell

will

be

types

of

-26-

1.3.6

Degree

It

and

type

of

is

of

also

On

array

cells,

no

which

forming

arrays

register

bits

memory,

lit

generally

degree

called

of

parallel

bit

Kautz[16].

by

their

each

group

The

-scratchpads,

of

Words

with

bits.

at

highest

the

In

Although

data.

arrays

form.

time

degree

are

of

],

have

any

most

of

The

etc.

is

number

of

shift

cell

where

a

higher

basically

sorting

can

be

with

array

ordered

retrieved

the

no

be

arrays

included

later

simply

--

are

may

of

yet

the

array

and

of

shift

class

logic

writing

capable

of

represents

memory

cutpoint

class

each

processing

memory

memories,

a

of

combinatorial

are

arrays

this

of

the

and

point

Minnick's

is

amount

particularly

this

but

example

the

endpoints

These

such

a

from

serially.

into

the

can

some

is

is

Chapter

which

One

written

scale

Nearby

well.

to

well-defined

combinatorial

cellular

associative

on

all.

This

discussed

memory

cell.

but

magnitudes

sequence.

be

accessible

in

according

cell.

its

"logic-in-memory"

memory,

or

the

presented

only

memory

of

performed

in

each

can

at

as

is

is

of

arrays

of

basically

flip-flops

register

each

end

memory

are

in

arrays

low

having

order

because

existing

the

to

contained

dimension

many

view.

useful

memory

interesting

because

memory.

memory

function

in

array

is

-27-

1.3.7

Defect

density.

Cellular

perform

useful

defects

may

is

required

3,

we

will

errors

designed

level

tradeoff

is

lower

discussed

in

detail

by

the

of

yield

a

requires

interconnections

cells

more

errors

and

such

communication

rows

are

outputs

a

size

may

order

of

expected

to

the

that

have

the

to

near

may

long

buses

be

done

be

via

Arrays

zero

may

of

raised

of

cell

to

any

those

This

to

is

a considerable

expected

(a

during

greater

its

number

path-building

around

in

edges

of

possible.

are

be

3.

necessary

array

between

testing.

yield

the

view

intitial

signals

be

of

percentage

influenced

route

Chapter

discarding

which

may

point

yield

In

simply

Chapter

cell

These

percent

array.

elaborate

to

cells

the

to

operation.

difference

by

is

lower

more

in

or

array

100

artificially

percent)

environment

Clearly,

defects)

Spare

an

defects.

certain

be

in

of

actual

From

a

ability

intolerable.

per

at

their

that

large

may

is

manufacture.

of

yield

yield

design

is

obviate

100

The

such

a

by

during

expected

(including

whose

or

arrays.

is

errors

course,

presence

failure

such

to

ranked

designed

there

more

be

the

cell

several

or

Of

be

one

specifically

desired

inputs

may

even

one

failures.

extent

manufacture

designer

and

arrays

during

present

array

also

in

arrays

and

may

functions

occur

Some

the

arrays

faulty

some

the

If

failure-

neighbor

and

cells.

arrays.

array,

the

_rone,

connections.

of

If

fewer

array

is

most

-28-

I. 3.8

Degree

By

program

among

of

commutativity,

itself

arrays

In

for

cell

outside

each

cell

various

the

fed

in from

step-wise

fashion

successor

until

array

the

of

future

research.

itself

it

its

must

cell

control

will

themselves

be

simply

by

bits

of

one

program

the

Each

was

and

cell

in

allowing

more

of

its

according

to

in

instruct

The

Chapter

be

solel_

propagated

would

programmed.

discussed

or

itself

array

some

lines.

might

done

to

common

have

than

of

array

not

rather

array.

Wahlstrom[44],

a

its

_rogrammable

4,

possesses

ability.

Another

self-healing

processor

within

edge

is

array

cells,

might

the

entire

and

an

other

state

one

across

for

of

which

connections

This

array

ability

property

paths

by

the

the

a

program

and

times

to

Then

parameters

to

data

array.

access

neighbors.

array

its

is

the

promise

functions

at

from

this

an

mean

This

holds

between

controlled

logic

which

order

some

we

internally.

but

connections

Thus

co mmutativif.y.

possible

within

might

itself

Capabilities

of

be

an

use

of

array.

capable

A

of

and

re programming

this

kind

are

commutativity

beyond

is

sufficientl_

detecting

around

the

some

complex

failures

the

scope

•form

which

offending

of

this

work.

of

array

occur

parts.

-29-

I._

Overview

It

should

this

be

is

array

will

is

of

is

this

a

major

contention

tailored

to

that

effort

any

the

misdirected.

attempt

to

accomplished

assumptions

PL

2

plus

assigned

examples.

modes

this

objective

task

to

a

design

some

in

set.

that

An

any

the

which

of

cellular

following

this

design

implication

highest-generality

in

ways

thesis

chapters

tailoring

we

may

be

arrays.

presents

a

set

relative

Distributions

failure

of

Therefore,

show

with

Chapter

their

work.

are

also

some

of

preliminary

logic

costs,

of

definitions

elements

which,

will

used

be

manufacturing

discussed

in

and

together

in

the

defects,

relation

following

yields

to

with

the

and

testing

problem.

Low-generality

Properties

related

significantly

detail.

of

the

to

different

Comparisons

same

arrays

functions.

are

are

considered

low-generality

examples

made

with

are

are

more

in

discussed

presented

conventional

and

Chapter

3.

and

two

analyzed

realizations

in

-30-

Chapter

arrays.

Severa

s tructure

and

example,

in

the

Characteristics

discussed.

terms

_ addresses

cell

control

of

a

PL

detail

m icroprogra

new

function

logic

and

for

Control

comparisons

of

to

approaches

for

a

are

synthesis

the

interconnec

are

is

machine

made

with

PL

are

presented.

processors

small

in

array

to

problems

central

high-generality

tion

As

approached

is

an

in

implemented

conventional

mined control.

Chapter

r es ea rc h.

important

I

array.

problem

5

gives

conclusions

and

suggestions

for

further

- 31 -

Foot no tes

0)

in

the

Numbers

including

This

[32]

2)

commonly

ind:icate

shift

the

n replaced

references

cited

(Fairchild

actual

to

logic

several

origin

the

to

not

known.

microprogramming

by

and

concept

gating

controlled

arrays

publications,

is

Register

centrally

goal:

in

and

commands

various

from

microprogramming

regularize

unstructured

a

have

control

_.5.

we

n-bit

register

shift

would

lines

can

on

leads

register

cequire

the

Section

trade

for

at

only

the

programming

edge

one

input

a discussion

of

of

and

the

speed

slice.

would

drive

slice.

2.2

for

the

distribution

defects.

5)

LSI

are

crucial

See

its

today.

Cellular

an

appeared

similarity

Furthermore,

including

_)

but

machines

Section

This

an

in

one

See

these

the

memory.

common

has

[29],

operations

3)

of

and

Note

data

logic.

by

diagram

used

read-only

in

brackets

bibliography.

I)

other

in square

At

this

device

3751

writing,

produced

12-bi%

a

for

A

to

bug

some

has