Design of Wideband Distributed VCOs

advertisement

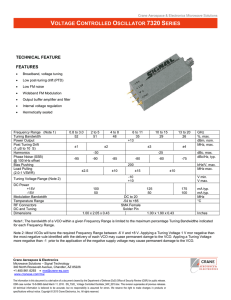

Advances in Circuits, Systems, Signal Processing and Telecommunications Design of Wideband Distributed VCOs F. CANNONE, G. AVITABILE, G. COVIELLO Dipartimento di Ingegneria Elettrica e dell’Informazione Politecnico di Bari Via Orabona 4 – 70125 Bari ITALY f.cannone@poliba.it http:// etlclab.poliba.it Abstract: - The paper describes a multi-band Distributed VCO topology suitable for multi-standard transceivers. This topology gives an optimum trade off among the multi-band capability and phase noise requirements. After a brief presentation of the DVCO operations a detailed analysis of the oscillation conditions for the topology is presented leading to general expressions for the amplitude and frequency of oscillation. A prototype with a measured 21.2% tuning range validates the theory. Key-Words: - Switched circuits, Microwave circuits, Voltage-controlled oscillators travelling wave VCOs and standing-wave VCOs [12]. Theoretically, the DVCO could benefit of the wide bandwidth of the amplifier and it allows to design fully integrated VCOs which operate at higher frequencies compared with the integrated LC-VCOs for a given technology. The literature proposes several examples of DVCOs operating in the forward gain mode [4]-[11], but none of these solutions exploits completely the potentiality of such class of oscillators in terms of wide tuning range. The key feature that offers the DA is the possibility to take advantage of its wide band to design a multi-band VCO operating on different bands for different wireless standards. The topologies proposed in [13] is a solutions striving to this purpose. The approach proposed in [13] separates the amplification from the phase shifting. In this way, the DA can play the role of a “loop-gain tank”. Thus, the amplifier can potentially sustain the oscillations over a very wide bandwidth and jointly provide uniform performances in terms of phase noise, output power and harmonics suppression. The way in which the phase shift is implemented is critical to correctly achieve the scope. Section 2 reports a detailed analysis of the oscillation condition for the topology presented in [13], leading to general expressions for the amplitude and frequency of oscillation while in section 3 the tuning technique is described. Using these equations a DVCO has been designed, and the measurements results are reported in section 4. 1 Introduction Modern telecommunication units commonly integrate different standards with their everincreasing bandwidth associated to each of them. This circumstance relates to the concurrent need for mobility and fast data rates of the customers. Consequently, frequency sources with multi-band characteristics, joint to low-power consumption and stringent phase noise performances represent strategic component in such applications. The burden of such requirements transfers to the VCOs, which represent the core of the PLLs, as the indirect frequency synthesis is the almost universal solution adopted in TLC units. Thus, the VCOs have to deal with the difficult trade-off among wide tuning bandwidth and phase noise. The state-of-the-art offers different design techniques for wideband VCOs implementation, such as frequency translation (division, multiplication, injection locking), multiple VCOs, switched inductors based VCOs, multiple inductors based VCOs, transformer based VCOs, inductor reuse based VCOs and magnetic tuning based VCOs [3]. Distributed VCOs (DVCOs) obtain a wide tuning range and good phase noise differently from ring oscillators, which usually provide wide tuning range and poor phase noise, and LC-VCOs, which provide better phase noise but over smaller bands. The core of a DVCO is the distributed amplifier (DA) operating in the reverse gain mode, or in the forward gain mode [4]. DVCOs are also known as travelling wave VCOs which belong to the class of wavebased oscillators wherein there are the rotary- ISBN: 978-1-61804-271-2 26 Advances in Circuits, Systems, Signal Processing and Telecommunications sum at each tap point on the drain (collector) line of the DA, allowing a greater variation without the switching-off of the oscillation. A suitable choice of SL cell topology gives an additional degree of freedom. The proposed approach gives several advantages. First, the characteristic impedance, Z0 , of the DA is almost constant all over the tuning band. In addition, a flat response is ensured over the entire tuning band by the DA and, assuming that this latter has an optimum noise figure at its center band, better phase noise performances are obtained. The uniformity of the performances in terms of output power, phase noise and harmonics suppression into the overall wide tuning range, achievable by using the proposed solution, is a relevant feature for advanced transceivers. 2 Theory of the Distributed VCO The straightforward application of the Barkahusen criterion to a DA brings to a structure that concurrently governs phase and amplitude of the signal along the path by interconnecting the gate (base) and drain (collector) lines. Assuming equal propagation properties for both transmission lines into the DA, the oscillation frequency, fo , is [4]: √ (1) where vphase is the phase velocity along the transmission lines, l is the electrical length of the single cell, n is the number of transistors, L and C are the inductance and the capacitance per unit length and fC is the cut-off frequency of the loaded transmission lines. The oscillation frequency in (1) can be tuned either changing the phase velocity and/or the effective length of the transmission lines. The losses in the DA limit, in practical implementations, the number of transistors to 3-4. Therefore, the DA operates at a frequency close to fC and this condition implies that the characteristic impedance of transmission lines strongly varies with frequency, the attenuation of the transmission lines due to impedance mismatch increases and the noise figure of the DA increases as well. These issues are circumvented when the DVCO is divided into two blocks, the DA followed by a Synthetic Line (SL) (Fig. 1) [13]. The resulting DVCO shows a wide tuning range joint to small variations of the output power, reduced phase noise and low harmonic generation over the entire tuning bandwidth [14]. It is critical to such arrangement that the DA gives enough inverting gain to sustain the oscillation over the required bandwidth, according to its distributed nature, regardless of the required phase shift. Therefore the transmissions line cut-off frequency in the amplifier, fC,amp, must be set far enough from the tuning band upper limit. The phase shift required for the oscillation, 180°- α, is controlled by the second block, where α is a small phase shift introduced by the DA that can be variable if the inherent varactor tuning technique is used. The SL, in its basic version, is an m-cells periodic structure, wherein each cell provides the phase shift equal to (180°- α)/m. The electrical behavior of the SL depends on the topology of its basic cell. Since the tuning is achieved by varying the electrical parameters of the second block, it does not affect the in phase power- ISBN: 978-1-61804-271-2 Fig. 1. DVCO topology. 2.1 General conditions of oscillation The evaluation of the conditions of oscillation requires to break the feedback loop, as in Fig.2. The DVCO becomes the cascade of the DA and the SL and the open loop gain is the product of the gain of each stage. The DA contains n transistors and two transmission lines. In the forthcoming paragraph we assume a MOS implementation but similar consideration can be made for the bipolar case. The transistors amplify the forward wave traveling on the gate line which is absorbed by the termination matched to characteristics impedance of the gate line, Zg. If the incident wave traveling on the drain line travels with the same phase velocity, then at each tap of the drain line the corresponding gain stage gives an in-phase power contribution to the signal. The backward wave on the drain line is absorbed by the termination matched to characteristics impedance of the drain line, Zd. Assuming that the spacing between the transistors is smaller than half wavelength then their input and output impedances can be considered distributed 27 Advances in Circuits, Systems, Signal Processing and Telecommunications ( and added to the parameters per unit length of the transmission lines. The DA gain can be calculated starting from the circuit presented in Fig. 3. ( ) ( ) (5). ) By substituting in (5), (3) and (4), it is possible to achieve the following expression: ( ( ) ) (6). Summing all the contributions, vo is expressed by: ( ( ∑ ) ) (7). Using the identity, an - bn = (a-b)(an-1+an2b+..+bn-1), the previous equation becomes: Fig.2. DVCO open-loop. ( ( ) ) (8). Finally, the DA gain is expressed by: ( The impedance, Zk, seen at kth tap of the drain line is Zd//ZSLK, where Zd is the characteristics impedance of the drain line and ZSLK is the input impedance of the SL transformed along the path to the kth tap point along the drain transmission line: ( ) ) ( where ΓSL is the reflection coefficient at the input of the SL and γd is the complex propagation constant of the loaded drain line. The voltage at the kth tap point is: ( ) (3) where Gm is the large-signal transconductance of each transistor. The voltage at the kth tap point of the gate line is related to the gate line segment, lg, and to the complex propagation constant of the loaded gate line, γg : ( ) ( ) ( ( ) (10). ) ) ( (11) ) where ΓL is the reflection coefficient at the output section of the SL while γsl is the complex propagation constant of the SL; the expression of γsl depends on the type of cell into the SL. The open loop gain is equal to ADA*ASL. In the case of γglg = γdld = γl , the open loop gain is: (4) where vin is the voltage at the input node of the DA. The voltage, vo , across the load ZSL can be determined by using the superposition method. The contribute to vo due to the kth transistor is: ISBN: 978-1-61804-271-2 (9). In the previous equations it has been considered the case of a matched load Zd connected to the drain line which absorbs the reflected wave. By using the previous approach, it is easy to generalize the expression of the DA gain when a generic load impedance is connected to the drain line. The gain of the second stage is the ratio between the voltage, vo , calculated before, and vr (Fig.2). The SL is a cascade of m identical cells, and can be modeled as a transmission line. By using the relation between the values of voltages along a transmission line, it is possible to express as follows the gain of the second stage: ) (2) ( ) In the case of γglg = γdld = γl , the voltage gain is equal to: Fig.3. Equivalent circuit of the drain line. ( ( ) ( 28 ) ( ) ( ) ( ) (12). Advances in Circuits, Systems, Signal Processing and Telecommunications Finally the general condition of oscillation is expressed by the following equation: ( ) ( ) ( ( ) ) specs using the amplifier resource. This novel point of view offers the possibility to implement new tuning schemes thanks to the weak interaction between the tuning controlled by the SL and the operation of the DA [15]-[16]. Switched-capacitors banks are commonly used in LC-VCOs design to achieve coarse jumps of the capacitance C which fixes the oscillation frequency. This variation, ΔC, is usually controlled by exploiting a digital tuning scheme. The insertion of a switched-capacitors bank, similarly, gives to the SL of the DVCO the capability of introducing a discrete variation in the phase velocity along the transmission line (Fig.4). The obtained variation operates a discrete change in the band of synthesis. With this approach, the whole tuning range is subdivided in a set of sub-tuning ranges. (13). This expression sets both the amplitude and the frequency of oscillation. In the case of γglg = γdld = γl , the previous equation becomes: ( ) ( ) ( ) ( ) (14). The relation derived from the analysis presented provides a good approximation of the oscillation condition. This relation has been used to design the DVCO presented in the next sections. 3 The tuning techniques The most common tuning techniques used for DVCO use the inherent-varactor control and delaybalanced current steering [4]. Other techniques are the delay variation by positive feedback tuning technique [6] and the current starving method [11]. The inherent-varactor tuning permits to vary the oscillating frequency by modifying the phase velocities along the gate (base) and drain (collector) lines in the DA. The DC voltage bias controls the active components in the two lines and its variation in turn varies the capacitances along the lines, thus inducing the desired phase-shift variation. This solution is well suited for integration, because it does not require external components. On the other hand, the variations induced in the transistors bias point are unacceptable when a wide tuning range is required, because they usually bring to the damping of the oscillation. Moreover, the capacitances in the two SLs do not vary with the same rate when the DC voltage varies, thus, generating a difference in phase velocity which degrade the in-phase sum of the contributions along the gain line. This condition results in strong amplitude variations of the oscillation in the tuning band. The delay-balanced current steering tuning technique varies the effective basic cell line length basing its operation on the current-steering tuning technique. Usually this solution is used for the fine tuning because it offers less tuning span than the inherent-varactor technique. 3.1 Fig. 4 Basic cell of the Synthetic Line. The single cell of the synthetic line contributes by a given phase shift, φSC , to achieve the required oscillation frequency. When the banks of switchedcapacitors are added to the cells of the SL, they participate to set the oscillation frequency, since the cut-off frequency, fC,s.line , of the SL and, φSC depend on the capacitances inserted by the banks, √ ) ( ) (15) In particular, for a Π or T low pass cells φ SC is: ( ) ( ) (16). In (15), C(Vfine) is the capacitance provided by the varactor in each cell, b0C1+b1C2+…+bk-1Ck is the capacitance provided by each switched-capacitors bank controlled by the digital tuning scheme (b i is the i-th bit of the digital tuning signal VCOARSE). According to the previous equations, VCOARSE controls the band of operation while the oscillation frequency within each sub-band is tuned by controlling the varactors inserted in Alternative tuning techniques Thanks to the separation between the amplification and the phase shifting, the amplifier acts as a “loopgain tank” ensuring a wide bandwidth oscillation capability. Thus, the SL design aims to meet the ISBN: 978-1-61804-271-2 ( 29 Advances in Circuits, Systems, Signal Processing and Telecommunications the cells of the SL. This tuning solution aims to produce a variation in the phase velocity along the transmission lines of the DVCO. The theory introduced in the paper give good performances in terms of wide tuning range, phase noise, and harmonics suppression. The concurrent availability of a wideband gain-tank and versatile tuning techniques, like the switched capacitors bank, represents an optimum starting point for the design of multi-band DVCOs. 4 Prototype, measurements and results The simplified prototype based on switched-capacitors banks has a two-cells DA designed to ensure the required loop-gain taking also into account the variation of the input impedance of the SL due to the switching of the capacitors banks. Each bank has one capacitor and provides two different values of capacitance. Two different bands, thus, are digitally selectable. The measured DVCO measurements in Fig.5 feature more than 360 MHz tuning span, from 1.52GHz to 1.88GHz. The designed DVCO provides, at the same time, reduced phase noise and a suitable filtering action of the harmonics, assuring a good spectral purity. The subcharacteristics of tuning partially overlap to ensure the complete frequency synthesis over the tuning range. The prototype absorbs 8.5 mA from a 3.3V supply voltage. References: [1] J.Mitola,”The Software Radio Architecture,” IEEE Communications Magazine, vol.33, no. 5, pp. 26-38, May 1995. [2] F. Cannone, G. Avitabile, G. Coviello, “A 11-bit track and hold amplifier in 0.25 um SiGe BiCMOS for sampling receivers,” in Proc. of the 56th MWSCAS, pp. 792-795, Aug. 2013. [3] F. Cannone, “Novel multi-band VCO and new phased array transmitter suitable for the SDR technology and advanced microwave and mm-wave transceivers,” PhD Dissertation, Politecnico di Bari october 2009. [4] Hui Wu and A. Hajimiri,”Silicon-based distributed voltage-controlled oscillators, ” IEEE J. of solid-state circuits, vol. 36, no. 3, pp. 493-502, Mar. 2001. [5] B. Kleveland, C. H. Diaz, D. Dieter, L. Madden, T. H. Lee, and S. S. Wong,“Monolithic CMOS distributed amplifier and oscillator,” in Proc. IEEE ISSCC Dig. Tech. Papers, 1999, pp. 70–71. [6] P Bilionis, A.N. Birbas and M.K. Birbas,”Fully integrated differential distributed VCO in 0.35-μm SiGe BiCMOS Technology,“ IEEE Trans. on Microwave Theory Tech., vol.. 55, no. 1, pp. 13-22, Jan. 2007. [7] N.Seller, A. Cathelin, H.Lapuyade, J.B. Begueret, E. Chataigner and D. Belot,“A 10GHz Distributed Voltage Controlled Oscillator for WLAN Application in a VLSI 65nm CMOS Process,” in Proc. IEEE RFIC Symposium, pp.115-118, 2007. [8] K.Bhattacharyya and T.H. Szymanski,“Performance of a 12GHz monolithic microwave distributed oscillator in 1,2V 0.18um CMOS with a new simple design technique for frequency changing,” in Proc. IEEE WAMICON, 2005, pp. 174177. [9] K.F. Tsang and C.M.Yuen,”A 2.7V, 5.2 GHz Frequency synthesizer with 1/2subharmonically injection-locked (a) (b) Fig. 5 Measured tuning range: (a) 1.52GHz to1.78 GHz. (b) 1.69GHz to 1.88GHz As expected from the theory, the prototype shows uniform performances over the whole tuning range. Comparing the results achieved by the DVCOs reported in literature, summarized in Table I, with the results provided by the proposed DVCO, summarized in Table II, it is possible to note as this latter overcomes the other DVCOs in terms of relative tuning range, demonstrating the validity of the proposed technique. 5 Conclusion ISBN: 978-1-61804-271-2 30 Advances in Circuits, Systems, Signal Processing and Telecommunications distributed voltage controlled oscillator,” IEEE Transaction on Consumer Electronics, vol. 50, no. 4, pp. 1237-1243, Nov. 2004. [10] E.-C. Park and E. Yoon,“A 13 GHz CMOS distributed oscillator using MEMS coupled transmission lines for low phase noise,” in Proc. IEEE ISSCC Dig. Tech. Papers, 2004, pp. 300-309. [11] D. Guckenberger and K. T. Kornegay,“Design of a differential distributed amplifier and oscillator using close-packed interleaved transmission lines,” IEEE Journal of Solid-State Circuits, vol. 40, no. 10, pp. 1997–2007, Oct. 2005. [12] J.C. Chien and L.-H. Lu,“Design of wide-tuning-range millimeter-wave CMOS VCO with a astanding-wave architecture,” IEEE Journal of Solid State Circuits, vol. 42, no. 9, pp. 1942–1952, Sep. 2007. [13] G.Avitabile, F.Cannone, M.Capodiferro, L.Carella and N. Lofù,“A coarse-fine, wideband distributed voltage controlled oscillator for wireless applications,“ Electr. Letters, vol. 42. no. 5, pp. 285-286, Mar. 2006. [14] F. Cannone, G.Avitabile and N.Lofù,”New wideband distributed voltage controlled oscillator with a coarse-fine tuning,” in Proc. 9th European. Conf. on Wireless Tech., 2006, pp. 302-305. [15] F. Cannone and G. Avitabile,“Multi-Band VCO Based On Distributed VCO And Switched-Capacitors Banks” in Proc. 17th MIKON, Wroclaw, 2008, pp. 1-4. [16] F. Cannone, G. Avitabile and D. Cascella,“Multi-standard/multi-band Distributed VCO based on the ”Switchedcells Tuning Technique” for SDR Applications,” in Proc. Int. Symp. on Circuits and Systems, Paris, 2010, pp. 19911994. ISBN: 978-1-61804-271-2 31