Non-ideal Operational Amplifier

advertisement

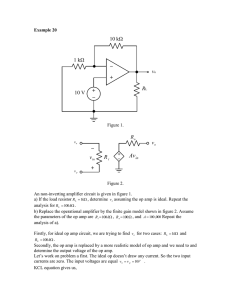

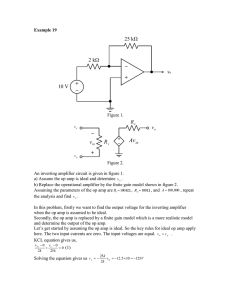

Lecture 11 Non-ideal Operational Amplifiers (op amp) Objectives Study non-ideal op amp behavior. Demonstrate circuit analysis techniques for non-ideal op amps. At the end of this class you should be able to: * Analyze op amp circuits assuming finite gain, non-ideal input and output resistance * Understand the effects of common mode gain and input resistance * Ideal op amp has following assumptions: Infinite common-mode rejection, power supply rejection, open-loop gain, bandwidth, output voltage range, output current capability Zero output resistance, input-bias currents and offset current, input-offset voltage. *Various error terms arise in practical operational amplifiers due to non-ideal behavior. The non-idealities can be classified as follows: I. Small signal errors: 1. Finite gain, input and output resistances 2. Common mode gain and input resistance II. Frequency Limitation 1. Finite bandwidth III. Large signal limitations: 1. Slew rate 2. Output voltage and currents limits IV. DC imperfections 1. Offset voltage 2. Biasing and offset currents 3. PSSR * In this class we will concentrate on the small signal non-idealities. Whereas, other limitations will be discussed in the following lectures. To simplify non-ideal analysis, each imperfection can be considered separately. * Finite Open-loop Gain Practical op amps have finite gains with typical values in the range of 80 to 100dB. Finite gain results in error between the ideal and actual gain. Example 1: Investigate the effect of finite op amp gain on the non-inverting amplifier performance. Solution: Replace the op amp with its simple model as shown in Fig. 1. Then, write KCL equation at v1 as follows: is + vid vs vo Avid R2 i Feedback network v1 R1 Fig. 1: Circuit for analyzing non-inverting amplifier with finite op amp gain v1 v1 − vo + = 0 (1) R1 R2 Note that for finite A, v − ≠ v + But vo = A(v+ − v − ) = A(v s − v1 ) Solving for v1: v v1 = − o + v s (2) A Substituting (2) in (1) and solving for vo yielding: vo 1 + R2 / R1 = Anon −ideal = 1 vs 1 + (1 + R2 / R1 ) A R2 R1 Following this procedure for analyzing the inverting amplifier, it can be shown that: − R2 (3) Anon −ideal = 1 R1 + ( R1 + R2 ) A You can see that as A → ∞, Anon −ideal → Aideal = 1 + Example 2: Consider an inverting amplifier with R1= 1kΩ, R2=100kΩ and vs=+0.1 V. Calculate the non-ideal gain, error, and v- for different op amp gains of: A = 10 3 , A = 10 4 and A = 105 . Solution: 1. The non-ideal gain can be calculated from equation (3) A − Anon −ideal 2. The percentage error is defended by Ε = ideal × 100 Aideal vo as v+=0 A Using these results, the following table can be developed: 3. Since vo = A(v + − v− ) ⇒ v − = − A 10 3 10 4 10 5 Anon-ideal -90.80V/V -99.00V/V -99.90V/V Ε 9.2% 1.0% 0.1% v-9.1mV -1.0mV -0.1mV It can be seen that as A increases, the non-ideal gain and v- approach their ideal values of –100V/V and 0V, respectively. Also, it is evidence that as the gain of the op amp increases, the error is decreased. * Finite Differential Input Resistance: For an ideal op amp, the input resistance is infinity forcing i-=i+=0. However, practical op amp particularly those based on BJT have finite input resistance (in the range of view mega ohms). This finite differential input resistance will introduce errors in both the closed loop gain and the input resistance of amplifiers. Example 3: Consider the inverting amplifier. Calculate its input resistance if the op amp has finite input resistance Rid. Solution: 1. Replace the op amp with its model with finite Rid as shown in Fig. 2. R2 is vs R1 v vid + v+ Rid vo Avid Fig. 2: Inverting amplifier model with finite Rid. 2. By definition: v x i x R1 + v − v = = R1 + − (4) ix ix ix v − vo v v v + Av− = − + − But i x = i− + i2 = − + − Rid R2 Rid R2 ix 1 1 1+ A = = + v − R Rid R2 This means v R2 (5) R = − = Rid ix 1+ A Substituting equation (5) in (4) yields: R2 R Rin = R1 + Rid ≈ R1 + 2 1+ A 1+ A Rin = For large A, Rin= R1 Example 4: Consider the non-inverting amplifier. Calculate its input resistance if the op amp has finite input resistance Rid. Solution: 1. Replace the op amp with its model with finite Rid as shown in Fig. 3. 2. By definition: vx ix Test voltage source vx is applied to input and current ix is calculated. Rin = ix = vx − v 1 R id v =i R ≅i R 1 1 1 2 1 Assuming i -<<i2 implies i1 = i2 Fig. 3. The non-inverting Amplifier with finite Rid. R 1 v = βv v ≅ o 1 R +R o 1 2 = β ( Av ) = Aβ (v x − v ) 1 id Aβ v = v 1 1+ Aβ x Aβ vx − vx vx 1 + β A ∴i x = = (1+ Aβ )R R id id R = R (1+ Aβ ) in id * Nonzero Output Resistance For an ideal op amp, the output resistance is zero. However, practical op amps have small output resistance Ro (about view tens of ohms). This output resistance will introduce errors in both the closed loop gain and the output resistance of amplifiers. Example 5: Consider the non-inverting amplifier. Calculate its input resistance if the op amp has nonzero output resistance Ro. Solution: 1. Replace the op amp with its model with Ro as shown in Fig. 4. Fig. 4. The non-inverting Amplifier with finite Ro. 2. Output terminal is driven by test source vx and current ix is calculated to determine output resistance (all independent sources are turned off). By definition: v Rout = x ix i x = io + i io = 2 v x - Av id Ro vx i = 2 R +R 1 2 Also, vid= -v1 and R 1 v = βv v = x 1 R +R x 1 2 i 1+ Aβ 1 1 ∴ = x = + vx Ro R +R R out 1 2 ∴Rout = Ro ⎛ ⎞ ⎜R + R ⎟ ⎜ ⎟ 1+ Aβ ⎝ 1 2 ⎠ Since, Ro/(1+Ab)<<(R1+R2), R Rout ≅ o 1+ Aβ If A is infinite, Rout=0 * Note that the equivalent circuit when calculating the output resistance with vs=0 is the same for both inverting and non-inverting amplifiers as shown in Fig. 5. Fig. 5: Circuits for calculating output resistances of inverting and non-inverting amplifiers Finite Common-Mode Rejection Ratio (CMRR) A real amplifier responds to signal common to both inputs, called common-mode input voltage. In general, A,Acm v1 + vo v2 Fig. 6: Common mode gain model v + v ⎞⎟ vo = A(v − v ) + Acm 1 2 ⎟ 1 2 2 ⎟⎟⎠ = A(v ) + Acm(v ) ic id ⎛ ⎜ ⎜ ⎜⎜ ⎝ where: A(or Adm)= differential-mode gain Acm = common-mode gain vid = differential-mode input voltage vic = common-mode input voltage The two inputs can be also expressed as: v v = v + id 1 ic 2 v v = v − id 2 ic 2 Ideal amplifier has Acm = 0, but for a real amplifier, ⎛ A v ⎞⎟ ⎛ v ⎞ ⎜ vo = A⎜⎜ v + cm ic ⎟⎟ = A⎜⎜ v + ic ⎟⎟ A ⎟⎠ ⎜⎝ id CMRR ⎟⎠ ⎜ id ⎝ CMRR = A Acm Example 6: Find voltage follower gain error due to CMRR v = vs − vo id ⎛ (v + v ) ⎞ vo = A⎜⎜ (vs − vo )+ s o ⎟⎟ 2CMRR ⎠ ⎝ ⎞ 1 ⎟ ⎟ vo ⎜ ⎟ Av = = ⎝ 2CMRR ⎠ ⎞ 1 vs 1+ A⎛⎜1− ⎟ ⎜ ⎟ ⎜ 2CMRR ⎟⎠ ⎝ ⎛ A⎜⎜1+ Ideal gain for voltage follower is unity. Hence the gain error is given by: A 1− 2 CMRR GE = 1 − A v = ⎛ ⎞ 1 ⎟ 1 + A ⎜⎜ 1 − ⎟ ⎜ ⎟ 2 CMRR ⎝ ⎠ Since, both A and CMRR are normally >>1, GE ≅ 1 1 − A CMRR First term is due to finite amplifier gain, second term shows that CMRR may introduce an even larger error. Common-mode Input Resistance: Fig. 7: Model for common mode input resistance *When a pure common-mode signal vic is applied to amplifier input (vid =0), total resistance presented to source is Ric or common-mode input resistance. Normally, Ric >> Rid. Whereas, for a purely differential-mode input signal, input resistance is Rid.