switched capacitor circuits

advertisement

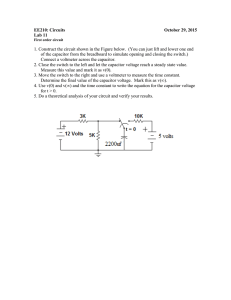

Switched Capacitor Circuits (10/11/00) SWITCHED CAPACITOR CIRCUITS INTRODUCTION Objective The objective of these notes is to provide an elementary background about switched capacitor circuits. Outline • Introduction • Resistance emulation • Switches • Amplifiers • Integrators • First-order circuits • Summary ECE4430 Analog Integrated Circuit Design Page 1 Switched Capacitor Circuits (10/11/00) Page 2 RESISTORS RESISTOR EMULATION Switched Capacitors are Not New James Clerk Maxwell used switches and a capacitor to measure the equivalent resistance of a galvanometer in the 1860’s. Parallel Switched Capacitor Equivalent Resistor: i1(t) v1(t) 1 vC (t) C i1(t) i2 (t) 2 v2 (t) R v1(t) i2 (t) v2 (t) (b.) (a.) Figure 9.1-1 (a.) Parallel switched capacitor equivalent resistor. (b.) Continuous time resistor of value R. Two-Phase, Nonoverlapping Clock: 1 1 t 0 2 1 t 0 0 T/2 T 3T/2 2T Figure 9.1-2 - Waveforms of a typical two-phase, nonoverlapping clock scheme. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 3 EQUIVALENT RESISTANCE OF A SWITCHED CAPACITOR CIRCUIT Assume that v1(t) and v2(t) are changing slowly with respect to the clock period. The average current is, T T/2 1 ⌠ 1 i1(average) = T ⌡ i1(t)dt = T ⌠ ⌡i1(t)dt 0 0 Charge and current are related as, dq (t) i1(t) = 1 dt Substituting this in the above gives, i1(t) v1(t) 1 vC (t) i2 (t) 2 C v2 (t) T/2 1 q (T/2)-q1(0) CvC(T/2)-CvC(0) ⌡dq1(t) = 1 = i1(average) = T ⌠ T T 0 However, vC(T/2) = v1(T/2) and vC(0) = v2(0). Therefore, C [v1(T/2)-v2(0)] C [V 1-V 2] ≈ i1(average) = T T For the continuous time circuit: i1(t) i2 (t) R V -V T ⇒ i1(average) = 1R 2 ∴ R ≈ C v1(t) v2 (t) For v1(t) ≈ V1 and v2(t) ≈ V2, the signal frequency must be much less than fc. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 4 EXAMPLE 9.1 - DESIGN OF A PARALLEL SWITCHED CAPACITOR RESISTOR EMULATION If the clock frequency of parallel switched capacitor equivalent resistor is 100kHz, find the value of the capacitor C that will emulate a 1MΩ resistor. Solution The period of a 100kHz clock waveform is 10µsec. Therefore, using the previous relationship, we get that T 10-5 C = R = 106 = 10pF We know from previous considerations that the area required for 10pF capacitor is much less than for a 1MΩ resistor when implemented in CMOS technology. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 5 POWER DISSIPATION IN THE RESISTANCE EMULATION If the switched capacitor circuit is an equivalent resistance, how is the power dissipated? i1(t) v1(t) 1 vC (t) 2 C i1(t) i2 (t) v2 (t) i2 (t) R v1(t) v2 (t) (b.) (a.) Figure 9.1-1 (a.) Parallel switched capacitor equivalent resistor. (b.) Continuous time resistor of value R. Continuous Time Resistor: (V 1 - V 2 ) 2 Power = R Discrete Time Resistor Emulation: Assume the switches have an ON resistance of Ron. The power dissipated per clock cycle is, T (V 1 -V 2) ⌠e -t/(RonC)dt ⌡ Power = i1(aver.)(V 1-V 2) where i1 (aver.) = R onT 0 T (V 1-V 2)2 (V1-V2)2 (V 1 -V 2 )2 ⌠ -t/(R C) -T /(R C ) on dt = on ⌡e ∴ Power = TR + 1] ≈ (T/C) if T >> R onC (T/C) [ -e on 0 Thus, if R = T/C, then the power dissipation is identical in the continuous time and discrete time realizations. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 6 OTHER SWITCHED CAPACITOR EQUIVALENT RESISTANCE CIRCUITS i1(t) v1(t) 1 2 S1 S2 C vC (t) i1(t) i2 (t) 1 C1 v1(t) v2 (t) S1 vC1 (t) 1 i2 (t) 2 i1(t) S2 v2 (t) vC2(t) C2 Series-Parallel 2 v1(t) Series Series-Parallel: The current, i1(t), that flows during both the φ1 and φ2 clocks is: 2 S1 C S2 i2 (t) vC (t) S1 1 S2 v2 (t) Bilinear 1⌠ 1 ⌠ q1(T/2)-q1(0) q 1(T)-q 1(T/2) ⌠ i1(average) = ⌡ ⌡ i (t)dt = i (t)dt + ⌡ i (t)dt + 1 1 1 = T 0 T 0 T T T/2 T T/2 T Therefore, i1(average) can be written as, C [v (T/2)-vC2(0)] C1 [vC1(T)-vC1(T/2)] + i1(average) = 2 C2 T T The sequence of switches cause,vC2(0) = V2, vC2(T/2) = V1, vC1(T/2) = 0, and vC1(T) = V1 - V2. Applying these results gives C [V -V ] C [V -V - 0] (C1+C2)(V1-V2) i1(average) = 2 1 2 + 1 1 2 = T T T T Equating the average current to the continuous time circuit gives: R = C +C 1 2 ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 7 EXAMPLE 9.1-2 - DESIGN OF A SERIES-PARALLEL SWITCHED CAPACITOR RESISTOR EMULATION If C1 = C2 = C, find the value of C that will emulate a 1MΩ resistor if the clock frequency is 250kHz. Solution The period of the clock waveform is 4µsec. Using above relationship we find that C is given as, T 4x10-6 2C = R = = 4pF 106 Therefore, C1 = C2 = C = 2pF. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 8 SUMMARY OF THE FOUR SWITCHED CAPACITOR RESISTANCE CIRCUITS Switched Capacitor Resistor Emulation Circuit Schematic 1 Parallel 2 v1(t) C v2 (t) 1 Series v1(t) v1(t) Bilinear ECE4430 Analog Integrated Circuit Design v2 (t) T C v2 (t) T C1Ê+ÊC2 2 C1 C2 1 2 C v1(t) T C 2 C 1 Series-Parallel Equivalent Resistance 2 1 v2 (t) T 4C Switched Capacitor Circuits (10/11/00) Page 9 ACCURACY OF SWITCHED CAPACITOR CIRCUITS Consider the following continuous time, first-order, low pass circuit: R1 v1 C2 v2 The transfer function of this simple circuit is, V (jω ) 1 1 H(jω ) = V 2(jω ) = j ω R C + 1 = j ω τ + 1 1 1 2 1 where τ1 = R1C2 is the time constant of the circuit and determines the accuracy. Continuous Time Accuracy Let τ1 = τC. The accuracy of τC can be expressed as, dτC dR1 dC2 ⇒ 5% to 20% depending on the size of the components τC = R1 + C2 Discrete Time Accuracy T 1 Let τ1 = τD = C2 = C . The accuracy of τD can be expressed as, C1 f c C 1 2 dτD dC2 dC1 df c ⇒ 0.1% to 1% depending on the size of components τD = C2 - C1 - f c The above is the primary reason for the success of switched capacitor circuits in CMOS technology. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 10 SWITCHED CAPACITOR CIRCUITS - k T / C NOISE Switched capacitors generate an inherent thermal noise given by kT/C. This noise is verified as follows. An equivalent circuit for a switched capacitor: Ron + vin C - + vout + vin C - - + vout - (a.) (b.) Figure 9.3-11 - (a.) Simple switched capacitor circuit. (b.) Approximation of (a.). The noise voltage spectral density of Fig. 9.3-11b is given as 2 eRon = 4kTRon Volts2/Hz = 2kTRon Volt2/Rad./sec. π (1) The rms noise voltage is found by integrating this spectral density from 0 to ∞ to give ∞ 2 v Ron 2kTR on ⌠ ω 12d ω 2kTR onπ ω 1 k T 2 = π ⌡ω 12+ ω 2 = π 2 = C Volts(rms) (2) 0 where ω1 = 1/(RonC). Note that the switch has an effective noise bandwidth of 1 fsw = 4RonC Hz which is found by dividing Eq. (2) by Eq. (1). ECE4430 Analog Integrated Circuit Design (3) Switched Capacitor Circuits (10/11/00) Page 11 SWITCHES MOS TRANSISTOR AS A SWITCH Symbol Bulk A B A B (S/D) (D/S) C (G) Fig4.1-2 On Characteristics of a MOS Switch Assume operation in active region (vDS < vGS - VT) and vDS small. iD = µCoxW v D S µCoxW (v G S - V T ) vDS ≈ (vGS - VT)vDS L L 2 Thus, vD S 1 RO N ≈ i = µC W D ox (v G S - V T ) L OFF Characteristics of a MOS Switch If vGS < VT, then iD = IOFF = 0 when vDS ≈ 0V. If vDS > 0, then 1 1 RO N ≈ = iD λ IOFFλ ≈ ∞ ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 12 MOS SWITCH VOLTAGE RANGES If a MOS switch is used to connect two circuits that can have analog signal that vary from 0 to 5V, what must be the value of the bulk and gate voltages for the switch to work properly? Bulk Circuit 1 (0 to 5V) (0 to 5V) (S/D) (D/S) Gate Circuit 2 Fig.4.1-3 • To insure that the bulk-source and bulk-drain pn junctions are reverse biased, the bulk voltage must be less than the minimum analog signal for a NMOS switch. • To insure that the switch is on, the gate voltage must be greater than the maximum analog signal plus the threshold for a NMOS switch. Therefore: VBulk ≤ 0V and V Gate > 5V + V T Also, VGate(off) ≤ 0V Unfortunately, the large value of reverse bias bulk voltage causes the threshold voltage to increase. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 13 CURRENT-VOLTAGE CHARACTERISTICS OF A NMOS SWITCH The following simulated output characteristics correspond to triode operation of the MOSFET. 100µA VGS=10V VGS=9V 60µA VGS=8V VGS=7V 20µA VGS=2V -20µA VGS=3V VGS=4V -60µA VGS=5V VGS=6V -100µA -1V -0.6V -0.2V SPICE Input File: MOS Switch On Characteristics M1 1 2 0 3 MNMOS W=3U L=3U .MODEL MNMOS NMOS VTO=0.75, KP=25U, +LAMBDA=0.01, GAMMA=0.8 PHI=0.6 VDS 1 0 DC 0.0 ECE4430 Analog Integrated Circuit Design 0.2V 0.6V 1V Fig. 4.1-3 VGS 2 0 DC 0.0 VBS 3 0 DC -5.0 .DC VDS -1 1 0.1 VGS 2 10 1 .PRINT DC ID(M1) .PROBE .END Switched Capacitor Circuits (10/11/00) Page 14 MOS SWITCH ON RESISTANCE AS A FUNCTION OF GATE-SOURCE VOLTAGE MOS Switch On Resistance 100kΩ W/L = 1 10kΩ W/L = 5 W/L = 10 1kΩ W/L = 50 100Ω 1.0V 1.5V 2.0V 2.5V 3.0V 3.5V 4.0V 4.5V 5.0V Fig. 4.1-5 Gate-Source Voltage SPICE Input File: +LAMBDA=0.01, GAMMA=0.8, PHI=0.6 MOS Switch On Resistance as a f(W/L) VDS 1 0 DC 0.001V M1 1 2 0 0 MNMOS W=3U L=3U VGS 2 0 DC 0.0 M2 1 2 0 0 MNMOS W=15U L=3U .DC VGS 1 5 0.1 M3 1 2 0 0 MNMOS W=30U L=3U .PRINT DC ID(M1) ID(M2) ID(M3) ID(M4) M4 1 2 0 0 MNMOS W=150U L=3U .PROBE .MODEL MNMOS NMOS VTO=0.75, KP=25U, .END ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 15 INFLUENCE OF THE ON RESISTANCE ON MOS SWITCHES Finite ON Resistance: vC(0) = 0 + vin=2.5V C v + C VGate vin>0 C RON Fig. 4.1-6 Example Initially assume the capacitor is uncharged. If VGate(ON) is 5V and is high for 0.1µs, find the W/L of the MOSFET switch that will charge a capacitance of 10pF in five time constants (KN’=110µA/V2 and VTN = 0.7V). Solution 20ns 100ns = 20ns. Therefore RON must be less than 10pF = 2kΩ. 5 The on resistance of the MOSFET (for small vDS) is The time constant must be equal to 1 W 1 1 ⇒ = = RON = K ’(W/L)(V -V ) L R ON ·K N ’(V GS -V T ) 2kΩ·110µA/V2·4.3 = 1.06 N GS T Comments: • It is relatively easy to charge on-chip capacitors with minimum size switches. • Switch resistance is really not constant during switching and the problem is more complex than above. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 16 INCLUDING THE INFLUENCE OF THE VARYING ON RESISTANCE Gate-source Constant K’W (t) = g gON(0) ID t=0 ON L (v GS (t)-V T ) -v DS (t) VGS=5V g ON (0) + g ON (∞) 1 gON(aver.) = r ≈ 2 ON(aver.) K’WV DS (0) K’W K’W gON(∞) = 2L (V GS -V T ) + 2L (V GS -V T ) 2L K’WV DS (0) K’W = L (V GS -V T ) 2L t=∞ vDS(∞) vDS(0) VDS Fig. 4.1-7 Gate-source Varying ID gON(0) t=0 VGate + vGS(t) - VGS=5V vIN VGS=5V-vIN + C - vC(0) = 0 gON(∞) t=∞ vDS(∞) vDS(0) VDS Fig. 4.1-8 K’WV DS (0) K’W K’W gON= 2L [V GS (0)-V T] + 2L [V GS(∞)-vIN-V T] 2L ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 17 SWITCH ON RESISTANCE EXAMPLE Assume that at t = 0, the gate of the switch shown is taken to 5V. Design the W/L value of the switch to discharge the C1 capacitor to within 1% of its initial charge in 10ns. Use the MOSFET parameters of Table 3.1-2. 5V 0V 5V + C1 = - 10pF C2 = 10pF 0V vout(t) + + Fig.4.1-9 Solution Note that the source of the NMOS is on the right and is always at ground potential so there is no bulk effect as long as the voltage across C1 is positive. The voltage across C1 can be expressed as -t vC1(t) = 5exp RONC1 At 10ns, vC1 is 5/100 or 0.05V. Therefore, -103 -10-8 = 5exp RON R 10-11 ON 0.05 = 5exp ⇒ exp(GON103) = 100 ⇒ GON = ln(100) = 103 0.0046S ∴ K’WV DS K’W 110x10 -6·5 W -6 W 110x10 -6 ·4.3 0.0046 = L (V GS -V T ) = = 198x10 2L L 2 L W 0.0046 Thus, L = = 23.2 ≈ 23 198x10-6 ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 18 INFLUENCE OF THE OFF STATE ON MOS SWITCHES The OFF state influence is primarily in any current that flows from the terminals of the switch to ground. An example might be: vin + RBulk CH + vCH - vout Fig. 4.1-10 Typically, no problems occur unless capacitance voltages are held for a long time. For example, vout(t) = vCH[1 - e-t/(RBulkCH)] If RBulk ≈ 109Ω and CH = 10pF, the time constant is 109·10-11 = 0.01seconds ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 19 INFLUENCE OF PARASITIC CAPACITANCES The parasitic capacitors have two influences: • Parasitics to ground at the switch terminals (CBD and CBS) add to the value of the desired capacitors. This problem is solved by the use of stray-insensitive switched capacitor circuits • Parasitics from gate to source and drain cause charge injection onto or off the desired capacitors. This problem can be minimized but not eliminated. Model for studying charge injection: 1 1 Cchannel 1 CL + vCL - Rchannel CL VS A simple switch circuit useful for studying charge injection. ECE4430 Analog Integrated Circuit Design CGS0 CGD0 A distributed model of the transistor switch. + vCL - Cchannel 2 2 CGS0 VS Cchannel CGD0 Rchannel CL VS A lumped model of the transistor switch. + vCL - Fig. 4.1-11 Switched Capacitor Circuits (10/11/00) Page 20 CHARGE INJECTION (CLOCK FEEDTHROUGH, CHARGE FEEDTHROUGH) Charge injection is a complex analysis which is better suited for computer analysis. Here we will attempt to develop an understanding sufficient to show ways of reducing the effect of charge injection. What is Charge Injection? 1.) When the voltages change across the gate-drain and gate-source dv capacitors, a current will flow because i = C dt . 2.) When the switch is off, charge injection will appear on the external capacitors (CL) connected to the switch terminals causing their voltages to change. Fig. 4.1-12 There are two cases of charge injection depending upon the transition rate when the switch turns off. 1.) Slow transition time. 2.) Fast transition time. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 21 SLOW TRANSITION TIME Consider the following switch circuit: A A Switch ON B vin+VT C B Switch OFF vin+VT C Charge injection vin CL vin CL Fig. 4.1-13 1.) During the on-to-off transition time from A to B, the charge injection is absorbed by the low impedance source, vin. 2.) The switch turns off when the gate voltage is vin+VT (point B). 3.) From B to C the switch is off but the gate voltage is changing. As a result charge injection occurs to CL. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 22 FAST TRANSITION TIME For the fast transition time, the rate of transition is faster than the channel time constant so that some of the charge during the region from point A to point B is injected onto CL even though the transistor switch has not yet turned off. A A Switch ON B vin+VT B Switch OFF C Charge injection vin CL vin vin+VT C Charge injection CL Fig. 4.1-14 ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 23 APPROXIMATE ANALYSIS OF FEEDTHROUGH The model for this case is given as: A B Switch OFF COL vin ≈VS ≈VD VS +VT C VT VL COL Charge injection CL COL + VS +VT Circuit at the VL instant gate reaches VS +VT CL vCL VS Fig. 4.1-16 The switch decrease from B to C is modeled as a negative step of magnitude VS +VT - VL. The output voltage on the capacitor after opening the switch is, CL COL COL COL vCL = V S - V T -(V S + V T -V L ) ≈ V S - (V S + 2V T -V L ) COL+CL COL+CL COL+CL CL if COL < CL. Therefore, the error voltage is COL COL V error ≈ -(V S + 2V T - V L ) = -(v in + 2V T - V L ) CL CL ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 24 SOLUTIONS TO CHARGE INJECTION 1.) Use minimum size switches to reduce the overlap capacitances and/or increaseCL. 2.) Use a dummy compensating transistor. φ1 φ1 W1 L1 WD = W1 LD 2L1 M1 MD Fig. 4.1-19 • Requires complementary clocks • Complete cancellation is difficult and may in fact may make the feedthrough worse 3.) Use complementary switches (transmission gates) 4.) Use differential implementation of switched capacitor circuits (probably the best solution) ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 25 INPUT-DEPENDENT CHARGE INJECTION Examination of the error voltage reveals that, Error voltage = Component independent of the input + Component dependent on the input This only occurs for switches that are floating and is due to the fact that the input influences the voltage at which the transistor switches (vin ≈ VS ≈ VD). Leads to spurious responses and other undesired results. Solution: Use delayed clocks to remove the input-dependence by breaking the current path for injection from the floating switches. φ1 Ci Cs φ2 Vin φ1d S1 S4 φ2 S2 S3 φ1 t φ2 Vout CL t φ1d t Clock Delay Fig. 4.1-20 Assume that Cs is charged to Vin (both φ1 and φ1d are high): 1.) φ1 opens, no input-dependent feedthrough because switch terminals (S3) are at ground potential. 2.) φ1d opens, no feedthrough occurs because there is no current path (except through small parasitic capacitors). ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 26 CMOS SWITCHES (TRANSMISSION GATE) Clock Clock A VDD B A B Clock Clock Advantages: • Feedthrough somewhat diminished • Larger dynamic range • Lower ON resistance Disadvantages: • Requires a complementary clock • Requires more area ECE4430 Analog Integrated Circuit Design Fig. 4.1-21 Switched Capacitor Circuits (10/11/00) Page 27 DYNAMIC RANGE OF THE CMOS SWITCH The dynamic range of a switch is the range of voltages at the switch terminals (VA ≈ VB = VA,B) over which the ON resistance stays reasonably small. VDD M1 A B VDD VA,B Switch On Resistance 3kΩ 1µA M2 Fig. 4.1-22 Spice File: 2.5kΩ 2kΩ 1.5kΩ VDD = 4V VDD = 4.5V VDD = 5V 1kΩ 0.5kΩ 0kΩ Simulation of the resistance of a CMOS 0V 1V 2V 3V 4V transmission switch VA,B (Common mode voltage) M1 1 3 2 0 MNMOS L=2U W=50U M2 1 0 2 3 MPMOS L=2U W=50U .MODEL MNMOS NMOS VTO=0.75, KP=25U,LAMBDA=0.01, GAMMA=0.5, PHI=0.5 .MODEL MPMOS PMOS VTO=-0.75, KP=10U,LAMBDA=0.01, GAMMA=0.5, PHI=0.5 VDD 3 0 VAB 1 0 IA 2 0 DC 1U .DC VAB 0 5 0.02 VDD 4 5 0.5 .PRINT DC V(1,2) .END Result: Low on resistance over a wide voltage range becomes very difficult as the power supply decreases. ECE4430 Analog Integrated Circuit Design 5V Switched Capacitor Circuits (10/11/00) Page 28 CMOS SWITCH WITH TWIN-WELL SWITCHING VControl M1 VDD M3 Analog Signal Input M4 Analog Signal Output M5 VSS M2 VControl Circuit when VControl is in its high state. Circuit when VControl is in its low state. Low State High State M1 M1 Analog Signal Input Analog Signal Output M2 Low State ECE4430 Analog Integrated Circuit Design Analog Signal Input VSS VDD M2 High State Analog Signal Output Switched Capacitor Circuits (10/11/00) Page 29 CHARGE PUMPS FOR SWITCHES WITH LOW POWER SUPPLY VOLTAGES As power supply voltages decrease below 3V, it becomes difficult to keep the switch on at a low value of on-resistance over the range of the power supply. Consequently, charge pumps are used. Charge pump circuit: VDD = 3.3V (Prevents latchup) To a single NMOS switch Vhi ≈ 5V Vsub_hi M1 0V C2 C1 CL 0V 3.3V 0V Vhi = 2VDD·C C2 gate,NMOS switch + C 2 + C L ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 30 CHARGE PUMP - CONTINUED High voltage generator for the well of M1: VDD = 3.3V 6.6V Vsub_hi C2 C1 CStorage 0V 3.3V 0V Prevents latch-up of M1 by providing a high bulk bias (6.6V). Use a separate clock driver for each switch to avoid crosstalk through the gate clock lines. Area for layout can be small. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 31 SIMULATION OF THE CHARGE PUMP CIRCUIT Circuit: M1 CLK_out M2 M3 M5 C1 C1 M4 M6 CLK_in VDD CLK_out VSS Fig. 4.1-23 Simulation: 3.0 Output 2.0 Volts Input 1.0 0.0 -1.0 0.0 1.0 2.0 3.0 ECE4430 Analog Integrated Circuit Design 4.0 5.0 6.0 Time (µs) 7.0 8.0 9.0 10.0 Fig. 4.1-24 Switched Capacitor Circuits (10/11/00) SUMMARY OF MOS SWITCHES • Symmetrical switching characteristics • High OFF resistance • Moderate ON resistance (OK for most applications) • Clock feedthrough is proportional to size of switch (W) and inversely proportional to switching capacitors. • Output offset due to clock feedthrough has 3 components: Ideal Input dependent Input independent • Complementary switches help increase dynamic range. • As power supply reduces, switches become more difficult to fully turn on. ECE4430 Analog Integrated Circuit Design Page 32 Switched Capacitor Circuits (10/11/00) Page 33 AMPLIFIERS CONTINUOUS TIME AMPLIFIERS R2 R1 vIN Gain and GB = ∞: Gain ≠ ∞, GB = ∞: vOUT vIN R1 R2 - - + + Noninverting Amplifier V out R1+R2 V in = R1 A vd (0) R 1 A vd(0) V out R1+R2 R1+R2 = = A (0)R 1 R1 A vd (0)R 1 V in 1 + vd 1 + R1+R2 R1+R2 vOUT Inverting Amplifier V out R2 = V in R1 -R 2A vd(0) R 1A vd(0) V out R 2 R1+R2 R1+R2 = = V in A vd (0)R 1 A vd (0)R 1 R 1 1 + R +R 1 + R +R 1 2 1 2 Gain ≠ ∞, GB ≠ ∞: GB·R 1 Vout(s) R1+R2 R1+R2 R1+R2 ω H = = GB·R 1 R1 s+ω H V in(s) R1 s + R +R 1 2 ECE4430 Analog Integrated Circuit Design Vout(s) R 2 = - V in(s) R1 GB·R 1 R1+R2 R ω = - R2 s+ωH GB·R 1 1 H s + R +R 1 2 Switched Capacitor Circuits (10/11/00) Page 34 EXAMPLE 9.2-1- ACCURACY LIMITATION OF VOLTAGE AMPLIFIERS DUE TO A FINITE VOLTAGE GAIN Assume that the noninverting and inverting voltage amplifiers have been designed for a voltage gain of +10 and -10. If Avd(0) is 1000, find the actual voltage gains for each amplifier. Solution For the noninverting amplifier, the ratio of R2/R1 is 9. 1000 Avd(0)R1/(R1+R2) = 1+9 = 100. V out 100 = 10 = 9.901 rather than 10. ∴ V in 101 For the inverting amplifier, the ratio of R2/R1 is 10. Avd(0)R1 1000 R1+R2 = 1+10 = 90.909 V out 90.909 = -(10) = - 9.891 rather than -10. ∴ V in 1+90.909 ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 35 EXAMPLE 9.2-2 - - 3d B FREQUENCY OF VOLTAGE AMPLIFIERS DUE TO FINITE UNITY-GAINBANDWIDTH Assume that the noninverting and inverting voltage amplifiers have been designed for a voltage gain of +1 and -1. If the unity-gainbandwidth, GB, of the op amps are 2πMrads/sec, find the upper -3dB frequency for each amplifier. Solution In both cases, the upper -3dB frequency is given by GB·R 1 ω H = R +R 1 2 For the noninverting amplifier with an ideal gain of +1, the value of R2/R1 is zero. ∴ ωH = GB = 2π Mrads/sec (1MHz) For the inverting amplifier with an ideal gain of -1, the value of R2/R1 is one. GB·1 GB ω H = 1+1 = 2 = π Mrads/sec (500kHz) ∴ ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 36 CHARGE AMPLIFIERS C2 C1 vIN Gain and GB = ∞: vOUT vIN C2 C1 vOUT - - + + Noninverting Charge Amplifier V out C1+C2 V in = C2 Gain ≠ ∞, GB = ∞: Avd(0)C2 C1+C2 V out C1+C2 = V in A vd (0)C 2 C2 1 + C +C 1 2 Gain ≠ ∞, GB ≠ ∞: GB·C2 V out C1+C2 C1+C2 V in = C2 GB·C 2 s + C +C 1 2 ECE4430 Analog Integrated Circuit Design Inverting Charge Amplifier V out C1 = V in C2 V out C1 V in = -C2 Avd(0)C2 C1+C2 A vd (0)C 2 1 + C +C 1 2 GB·C2 V out C1 C1+C2 V in = -C2 GB·C 2 s + C +C 1 2 Switched Capacitor Circuits (10/11/00) Page 37 SWITCHED CAPACITOR AMPLIFIERS Parallel Switched Capacitor Amplifier: 1 vin 1 2 + C1 - vC1 C2 2 + vC2 - 1 vout + Inverting Switched Capacitor Amplifier vin 1 2 + C1 - vC1 - vC2 + C2 vout + Modification to prevent open-loop operation Analysis: Assume that the switching frequency (clock frequency, fc = 1/T) is much greater than the signal bandwidth. Then, “R2” T/C 2 C1 Vout V in = - “R 1 ” ≈ - T/C1 = - C2 If the oversampling assumption is not made, then the transfer function becomes, C1 Vout -1 = V in C2 z ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 38 FREQUENCY RESPONSE OF SWITCHED CAPACITOR AMPLIFIERS Replace z by e jωT. H(jω ) = V out(e jωT) C1 -jω T/2 = e V in (e j ω T ) C2 and H(jω ) = V out(e jωT) V in (e j ω T ) C = -C1 e -jωT 2 If C1/C2 is equal to R2/R1, then the magnitude response is identical to inverting unity gain amplifier. However, the phase shift of Hoe(e jωT) is Arg[H (e jωT)] = ±180° - ωT/2 and the phase shift of Hoe(e jωT) is Arg[H (e jωT)] = ±180° - ω T. Comments: • The phase shift of the switched capacitor inverting amplifier has an excess linear phase delay. • When the frequency is equal to 0.5fc, this delay is 90°. • One must be careful when using switched capacitor circuits in a feedback loop because of the excess phase delay. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 39 POSITIVE AND NEGATIVE TRANSRESISTANCE EQUIVALENT CIRCUITS Transresistance circuits are two-port networks where the voltage across one port controls the current flowing between the ports. Typically, one of the ports is at zero potential (virtual ground). Circuits: i1(t) vC(t) 2 2 C v1(t) 1 Positive Transresistance Realization. 2 i2(t) C 2 CP CP vC(t) 1 v1(t) 1 CP i1(t) i2(t) 1 CP Negative Transresistance Realization. Analysis (Negative transresistance realization): v (t) v1 R T = 1(t) = i (average) i2 2 If we assumev1(t) is approximately constant over one period of the clock, then we can T 1 ⌠ q (T) - q 2 (T/2) Cv C (T) - Cv C (T/2) -Cv1 i2 (t)dt = 2 = = T i2(average) = T ⌡ T T T/2 Substituting this expression into the one above shows that R T = -T / C Similarly, it can be shown that the positive transresistance is T/C. Comments: • These results are only valid when fc >> f. • These circuits are insensitive to the parasitic capacitances shown as dotted capacitors. ECE4430 Analog Integrated Circuit Design write Switched Capacitor Circuits (10/11/00) Page 40 INVERTING STRAY INSENSITIVE SWITCHED CAPACITOR AMPLIFIER 1 vin vC1(t) 2 C1 1 vC1(t) 1 2 - vC2 + C2 vout + Inverting Switched Capacitor Voltage Amplifier. Analysis: Assume that the switching frequency (clock frequency, fc = 1/T) is much greater than the signal bandwidth. Then, “R2” T/C 2 C1 Vout V in = - “R 1 ” ≈ - T/C1 = - C2 ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 41 NONVERTING STRAY INSENSITIVE SWITCHED CAPACITOR AMPLIFIER Use the negative transresistor switched capacitor circuit at the input to get, 1 vin vC1(t) 1 C1 2 1 2 - vC2 + C2 vout + Noninverting Switched Capacitor Voltage Amplifier. Analysis: Assume that the switching frequency (clock frequency, fc = 1/T) is much greater than the signal bandwidth. Then, “R2” T/C2 C1 Vout = ≈ = + V in -T/C1 C2 “R 1 ” ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 42 EXAMPLE 9.2-3 - DESIGN OF A SWITCHED CAPACITOR SUMMING AMPLIFIER Design a switched capacitor summing amplifier using the circuits in stray insensitive transresistance circuits which gives the output voltage during the φ2 phase period that is equal to 10v1 - 5v2, where v1 and v2 are held constant during a φ2-φ1 period and then resampled for the next period. Solution Based on the previous examples, a solution is proposed below. 10C 1 v1 C 2 v2 1 2 1 5C 2 1 2 1 + It easy to show that if the oversampling assumption is true that, V o ≈ 10V 1 - 5V 2 ECE4430 Analog Integrated Circuit Design vo Switched Capacitor Circuits (10/11/00) Page 43 NONIDEAL OP AMPS - FINITE GAIN Consider the inverting switched capacitor amplifier during φ2: C1 vino (n-1)T + C2 e vout (n-1/2)T Avd(0) + e vout (n-1/2)T + Op amp with finite value of Avd(0) Fig. 9.2-11 The output during φ2 can be written as, e e v out(n C o C +C v out (n -1/2)T -1/2)T = C1 v in(n -1)T + 1C 2 A vd(0) 2 2 Converting this to the z-domain and solving for the Hoe(z) transfer function gives e V out(z) C1 -1/2 1 oe = C z H (z) = o . + C C 2 V in(z) 2 1 - 1 Avd(0)C 2 Comments: • The phase response is unaffected by the finite gain • A gain of 1000 gives a magnitude of 0.998 rather than 1.0. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 44 NONIDEAL OP AMPS - FINITE BANDWIDTH AND SLEW RATE Finite GB: • In general the analysis is complicated. (We will provide more detail for integrators.) • The clock period, T, should be equal to or less that 10/GB. • The settling time of the op amp must be less that T/2. Slew Rate: • The slew rate of the op amp should be large enough so that the op amp can make a full swing within T/2. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 45 CONTINUOUS TIME INTEGRATORS Vin R1 C2 - R Vout R Vin C2 R1 - - - + + + Vout Inverter (b.) (a.) (a.) Noninverting and (b.) inverting continuous time integrators. Ideal Performance: NoninvertingInverting1 V out(jω ) -1 -ω I jω I V out(jω ) ω I -jω I = = = = = = ω ω V in(jω ) jω R 1C2 j ω V in(jω ) jω R 1C2 j ω Frequency Response: |Vout(jω)/Vin(jω)| Arg[Vout(jω)/Vin(jω)] 90° 40 dB 20 dB 0 dB -20 dB ωI ωI ωI 100 10 10ωI 100ωI 0° log10ω ωI -40 dB (a.) ECE4430 Analog Integrated Circuit Design (b.) log10ω Switched Capacitor Circuits (10/11/00) Page 46 NONINVERTING SWITCHED CAPACITOR INTEGRATOR Approximate analysis: vC1(t) Assume that the switching frequency (clock frequency, vin 1 + - 2 S1 S4 fc = 1/T) is much greater than the signal bandwidth. Then, C 1 1/sC2 1/sC2 C1 ωI Vout = ≈ = + = V in “R 1 ” -T/C1 sTC2 s where 2 S2 1 S3 - vC2 + C2 + Noninverting, stray insensitive integrator. CI ω I = TC 2 Exact analysis: V out(z) C z-1 C1 1 = 1 -1 = V in(z) C2 1-z C2 z-1 Exact frequency response (replace z by ejωT ) to get, Vout(ejωT) e-jωΤ/2 C1 ω T C1 ω T/2 -jωΤ/2 = C j2 sin( ω T/2) ω T = jω TC (e ) 2 sin( ω T/2) Vin(ejωT) 2 ωI C = (Ideal)x(Magnitude error)x(Phase error) where ω I = 1 ⇒ Ideal = TC jω 2 ECE4430 Analog Integrated Circuit Design vout Switched Capacitor Circuits (10/11/00) Page 47 EXAMPLE 9.3-2 - COMPARISON OF A CONTINUOUS TIME AND SWITCHED CAPACITOR INTEGRATOR Assume that ωI is equal to 0.1ωc and plot the magnitude and phase response of the noninverting continuous time and switched capacitor integrator from 0 to ωI. Solution Letting ωI be 0.1ωc gives 1 1 πω / ω c -jπω/ωc jωΤ oo H(jω ) = and H (e ) = (e ) 10jω /ω c 10jω /ω c sin(πω /ω c) Plots: 0 5 Magnitude Phase Shift (Degrees) -50 4 Arg[H(j ω)] -100 3 oo jω T oo jω T |H (e )| 2 )] -200 |H(jω)| ωI 1 Arg[H (e -150 -250 -300 0 0 0.2 0.4 ω/ω c 0.6 ECE4430 Analog Integrated Circuit Design 0.8 1 0 ωI 0.2 0.4 0.6 ω/ω c 0.8 1 Switched Capacitor Circuits (10/11/00) Page 48 INVERTING SWITCHED CAPACITOR INTEGRATOR Analysis: vC1(t) 2 Approximate analysis: vin 2 S1 Assume that the switching frequency (clock S4 C1 frequency, fc = 1/T) is much greater than the signal S2 S3 1 1 bandwidth. Then, 1/sC2 1/sC2 C1 Vout ωI = ≈ = = V in “R 1 ” T/C1 sTC2 s - + C2 vout + Inverting, stray insensitive integrator. where CI ω I = TC 2 Exact analysis: Vout(z) C1 1 C1 z H(z) = = -1 = - V in(z) C2 1-z C2 z-1 Exact frequency response (replace z by ejωT ) to get, Vout(ejωT) e-jωΤ/2 C1 ω T C1 ω T/2 = C j2 sin( ω T/2) ω T = - jω TC ( e jωΤ/2) 2 sin( ω T/2) Vin(ejωT) 2 Same as noninverting integrator except for phase error. Consequently, the magnitude response is identical but the phase response is given as π ωΤ Arg[H(e jωΤ)] = 2 + 2 . ECE4430 Analog Integrated Circuit Design vC2 Switched Capacitor Circuits (10/11/00) Page 49 A SIGN MULTIPLEXER A circuit that changes the φ1 and φ2 of the leftmost switches of the stray insensitive, switched capacitor integrator. 1 2 x VC y To switch connected to the input signal (S1). VC x y 0 2 1 1 1 2 To the left most switch connected to ground (S2). Fig. 9.3-8 This circuit steers the φ1 and φ2 clocks to the input switch (S1) and the leftmost switch connected to ground (S2) as a function of whether Vc is high or low. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 50 FIRST-ORDER, SWITCHED CAPACITOR CIRCUITS GENERAL, FIRST-ORDER TRANSFER FUNCTIONS A general first-order transfer function in the s-domain: sa1 ± a 0 H(s) = s + b0 a1 = 0 ⇒ Low pass, a0 = 0 ⇒ High Pass, a0 ≠ 0 and a1 ≠ 0 ⇒ All pass Note that the zero can be in the RHP or LHP. The following continuous time circuit is capable of realizing most of the various forms above: Vin R1 C1 R2 Vout C2 + Fig.9.5-0 Vout R2 sR1C1+1 = V in R1 sR 2 C 2 +1 ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 51 NONINVERTING, FIRST-ORDER, LOW PASS CIRCUIT α2C1 φ2 φ1 α1C1 φ1 vi(t) φ1 φ2 vo(t) φ1 vo(t) φ2 φ2 φ2 φ1 - C1 + vi(t) φ2 α2C1 φ1 φ1 φ2 α1C1 φ2 φ1 C1 vo(t) + (a.) (b.) Figure 9.5-1 - (a.) Noninverting, first-order low pass circuit. (b.) Equivalent circuit of Fig. 9.5-1a. Transfer function: Noting that C1 of the general circuit is zero gives, Vout -α 1 -α 1/T α1 “R2” 1 1 V in = - ”R1” s”R2”C2+1 ≈ - α2 sT/ α 2 +1 = sT + α 2 = s + α 2 /T Equating the above to the H(s) of the general first-order transfer function gives, a0 b0 α 1 = a 0T = f and α2 = b0T = f c c ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 52 INVERTING, FIRST-ORDER, LOW PASS CIRCUIT An inverting low pass circuit can be obtained by reversing the phases of the leftmost two switches in Fig. 9.5-1a. α2C1 φ2 φ1 α1C1 φ2 vi(t) φ1 φ2 vo(t) φ2 vo(t) φ2 φ1 φ2 φ1 - C1 vi(t) φ2 α2C1 φ1 φ1 φ2 α1C1 φ1 φ1 C1 vo(t) + + Inverting, first-order low pass circuit. Equivalent circuit. It can be shown that, Vout V in = α1 α1 α 1/T “R2” 1 1 ≈ = = s + α 2 /T ”R1” s”R 2”C 2+1 α2 sT/ α 2 +1 sT + α 2 Equating the above to the H(s) of a general first order transfer function gives the design equations as a0 b0 α 1 = a 0T = f and α2 = b0T = f c c ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 53 EXAMPLE 9.5-1 - DESIGN OF A SWITCHED CAPACITOR FIRST-ORDER CIRCUIT Design a switched capacitor first-order circuit that has a low frequency gain of +10 and a 3dB frequency of 1kHz. Give the value of the capacitor ratios α1 and α2. Use a clock frequency of 100kHz. Solution Assume that the clock frequency, fc, is much larger than the -3dB frequency. In this example, the clock frequency is 100 times larger so this assumption should be valid. Therefore we can write, Vout(s) α1 α 1/α 2 ≈ = Vin(s) α 2 + s T 1 + s(T/ α 2 ) ω-3dB Setting this equation equal to the specifications gives α1 = 10α2 and α2 = f c ∴ α 2 = 6283/100,000 = 0.0628 and α 1 = 0.6283 The above represent capacitor ratios and should preferably be close to unity for small area. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 54 FIRST-ORDER, HIGH PASS CIRCUIT α2C φ2 φ1 φ1 α1C α2C φ2 φ1 φ1 φ2 α1C vo(t) vi(t) + vo(t) φ2 - C vi(t) φ2 - C + (b.) (a.) Figure 9.5-3 - (a.) Switched-capacitor, high pass circuit. (b.) Version of Fig. 9.5-3a that constrains the charging of C1 to the φ2 phase. Transfer function: It can be shown that, s“R2”C1 sTα1C/α2C sTα1/α2 sTα1 sα1 Vout V in = - s”R2”C2+1 ≈ - sTC/α 2C +1 = - sT/ α 2 +1 = - sT + α 2 = - s + α 2 /T Equating the above to the general first-order H(s) gives the design equations as a1 = α1 and α2/T = b0 Solving for α1 and α2 gives α1 = a1 and b0 α 2 =b 0T = f c ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 55 FIRST-ORDER, ALLPASS CIRCUIT φ2 α3C φ1 vi(t) α2C φ1 φ1 α3C φ2 vo(t) α1C φ2 φ2 φ1 φ1 - C + vi(t) φ2 φ2 α2C φ1 φ1 vo(t) α1C φ2 φ2 φ1 - C + (a.) (b.) Figure 9.5-5 - (a.) High or low frequency boost circuit. (b.) Modification of (a.) to simplify the z-domain modeling Transfer function: Summing the currents flowing into the inverting input of the op amp gives α1 sTα3/α1+1 α 3 s + α 1 /T Vout “R2” s“R1”C1+1 = = = V in s + α 2 /T α2 sT/ α 2 +1 “R 1 ” s“R 2”C 2+1 Therefore, α3 = a1, α1/T = a0 and α2/T = b0 or a0 b0 a1 = α3, α1 = a0T = f and α2 = b0T = f c c ECE4430 Analog Integrated Circuit Design φ2 Switched Capacitor Circuits (10/11/00) Page 56 EXAMPLE 9.5-2 - DESIGN OF A SWITCHED CAPACITOR BASS BOOST CIRCUIT Find the values of the capacitor ratiosα1, α2, and α3 using a 100kHz clock for Fig. 9.5-5 that will realize the asymptotic frequency response shown in Fig. 9.5-7. 20 dB 0 10Hz 100Hz 1kHz 10kHz Frequency Figure 9.5-7 - Bass boost response for Ex. 9.5-2. Solution From the previous results, we can write the all-pass transfer function approximately as, α 1 sT α 3 / α 1 - 1 -sT α 3 + α 1 H(s) ≈ sT + α = - α sT/ α + 1 2 2 2 From Fig. 9.5-7, we see that the desired response has a dc gain of 10, a right-half plane zero at 2π kHz and a pole at -200π Hz. Thus, we see that the following relationships must hold. α1 α1 α2 = 10 , = 2000π , and α2 Tα3 T = 200π From these relationships we get the desired values as α1 = 2000π fc , ECE4430 Analog Integrated Circuit Design α2 = 200π fc , a n d α 3 = 1 Switched Capacitor Circuits (10/11/00) Page 57 PRACTICAL IMPLEMENTATIONS OF THE FIRST-ORDER CIRCUITS Most practical implementations of switched capacitor circuits are fully differential as shown below. φ1 φ2 α1C φ1 φ2 vi(t) φ1 C1 α1C φ2 φ1 φ2 α2C φ2 α1C + φ2 φ2 vo(t) φ1 α1C φ1 φ2 + α2C φ1 vo(t) vi(t) φ2 vo(t) φ2 α2C φ1 φ2 φ2 φ2 α1C φ2 φ1 α1C φ1 φ2 α3C φ1 φ1 α3C φ2 C φ2 φ1 α2C C -+ + - vo(t) vi(t) - C φ2 φ1 φ2 C -+ + - φ1 φ1 α2C φ2 + C -+ + - vo(t) - C vo(t) φ2 α2C φ1 φ2 φ1 (c.) (a.) (b.) Figure 9.5-8 - Differential implementations of (a.) Fig. 9.5-1, (b.) Fig. 9.5-3, and (c.) Fig. 9.5-5. Comments: • Differential operation reduces clock feedthrough, common mode noise sources and enhances the signal swing. • Differential operation requires op amps or OTAs with differential outputs which in turn requires a means of stabilizing the output common mode voltage. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 58 ANTI-ALIASING IN SWITCHED CAPACITOR FILTERS A characteristic of circuits that sample the signal (switched capacitor circuits) is that the signal passbands occur at each harmonic of the clock frequency including the fundamental. T(jω) T(j0) T(jωPB) Anti-Aliasing Filter Baseband ωc-ωPB ωc+ωPB 2ωc-ωPB 2ωc+ωPB 0 ωc 2ωc -ωPB 0 ωPB Figure 9.7-28 - Spectrum of a discrete-time filter and a continuous-time anti-aliasing filter. ω The primary problem of aliasing is that there are undesired passbands that contribute to the noise in the desired baseband. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 59 NOISE ALIASING IN SWITCHED CAPACITOR CIRCUITS In all switched capacitor circuits, a noise aliasing occurs from the passbands that occur at the clock frequency and each harmonic of the clock frequency. Magnitude ,, ,, ,, From higher bands Noise Aliasing Baseband fc-fsw fc+fsw f fc-fB -fB fc+fB 0.5fc fc 0 fsw fB Figure 9.7-31 - Illustration of noise aliasing in switched capacitor circuits. It can be shown that the aliasing enhances the baseband noise voltage spectral density by a factor of 2fsw/fc. Therefore, the baseband noise voltage spectral density is kT/C 2fsw 2kT x f = f C volts2/Hz f sw c c eBN2 = Multiplying this equation by 2fB gives the baseband noise voltage in volts(rms)2. Therefore, the baseband noise voltage is 2kT 2fB 2kT /C 2kT 2f = = volts(rms)2 ( B) C C f OSR f c c vBN2 = where OSR is the oversampling ratio. ECE4430 Analog Integrated Circuit Design Switched Capacitor Circuits (10/11/00) Page 60 SUMMARY • Switched capacitor circuits have reached maturity in CMOS technology. • The switched capacitor circuit concept was a pivotal step in the implementation of analog signal processing circuits in CMOS technology. • The accuracy of the signal processing is proportional to capacitor ratios. • Switched capacitor circuits have been developed for: Amplification Integration Differentiation Summation Filtering Comparing Analog-digital conversion • Approaches to switched capacitor circuit design: Oversampled approach - clock frequency is much greater than the signal frequency z-domain approach - specifications converted to the z-domain and directly realized, can operate to within half of the clock frequency (not covered in the above notes) • Clock feedthrough and kT/C noise represent the lower limit of the dynamic range of switched capacitor circuits. ECE4430 Analog Integrated Circuit Design