Advanced VLSI

advertisement

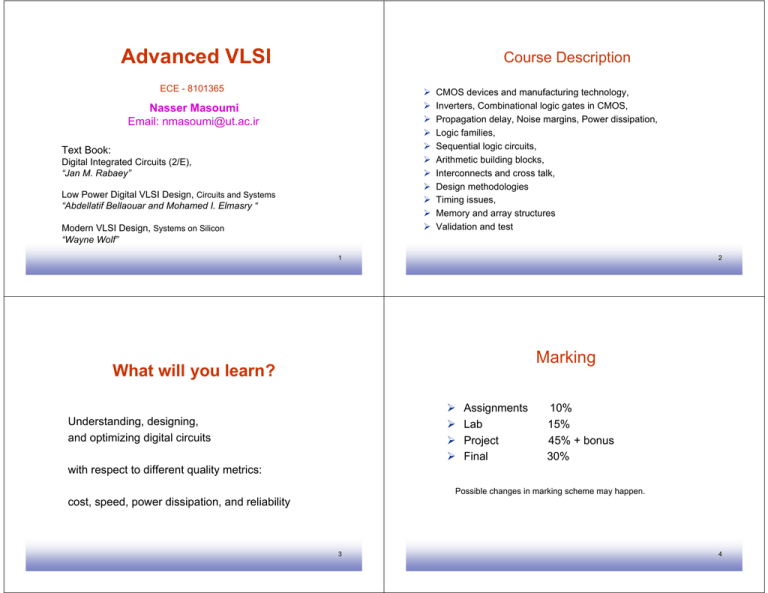

Advanced VLSI Course Description ECE - 8101365 ¾ ¾ ¾ ¾ ¾ ¾ ¾ ¾ ¾ ¾ ¾ Nasser Masoumi Email: nmasoumi@ut.ac.ir Text Book: Digital Integrated Circuits (2/E), “Jan M. Rabaey” Low Power Digital VLSI Design, Circuits and Systems “Abdellatif Bellaouar and Mohamed I. Elmasry “ Modern VLSI Design, Systems on Silicon “Wayne Wolf” CMOS devices and manufacturing technology, Inverters, Combinational logic gates in CMOS, Propagation delay, Noise margins, Power dissipation, Logic families, Sequential logic circuits, Arithmetic building blocks, Interconnects and cross talk, Design methodologies Timing issues, Memory and array structures Validation and test 1 2 Marking What will you learn? ¾ ¾ ¾ ¾ Understanding, designing, and optimizing digital circuits Assignments Lab Project Final 10% 15% 45% + bonus 30% with respect to different quality metrics: Possible changes in marking scheme may happen. cost, speed, power dissipation, and reliability 3 4 Presentations and Deadlines Projects ¾ ¾ ¾ ¾ ¾ ¾ ¾ ¾ ¾ ¾ Asynchronous Circuits, Clock Distribution, Transistor Sizing (Optimization), On Chip Cross-talk, Interconnects, Arithmetic Building Blocks, Memories, Pipelining, Power Management FPGAs. Project Topic End of Mehr First Presentation: Forth week of Aban Second Presentation: Last week of Azar Project Report Submission: Forth week of Bahman 5 6 Presentations and Deadlines Project Topic End of Esfand First Presentation: Third week of Farvardin Second Presentation: One week before final exam Project Report Submission: Two weeks after final exam PART I. THE FOUNDATIONS 7 8 2. THE MANUFACTURING PROCESS 1. INTRODUCTION ¾ ¾ ¾ ¾ ¾ ¾ A Historical Perspective ¾ Issues in Digital Integrated Circuit Design ¾ Quality Metrics of a Digital Design ¾ Cost of an Integrated Circuit ¾ Functionality and Robustness ¾ Performance ¾ Power and Energy Consumption Introduction Manufacturing CMOS Integrated Circuits Design Rules Packaging Integrated Circuits Perspective – Trends in Process Technology 9 3. THE DEVICES ¾ The MOS(FET) Transistor ¾ Introduction ¾ The Diode 10 A First Glance at the Device Static Behavior Dynamic or Transient Behavior The Actual Diode - Secondary Effects A First Glance at the Device Static Behavior Dynamic Behavior The Actual MOS Transistor - Secondary Effects SPICE Models for the MOS Transistor ¾ A Word on Process Variations ¾ Perspective: Technology Scaling 11 12 4. THE WIRE ¾ Introduction ¾ A First Glance ¾ Interconnect Parameters PART II. A CIRCUIT PERSPECTIVE Capacitance Resistance Inductance ¾ Electrical Wire Models ¾ Spice Wire Models 13 14 6. DESIGNING COMBINATIONAL LOGIC GATES in CMOS 5. THE CMOS INVERTER ¾ Introduction ¾ The CMOS Inverter ¾ Evaluating the Robustness of the CMOS Inverter: The Static Behavior Switching Threshold Noise Margins ¾ Performance of CMOS inverter: The Dynamic Behavior Computing the capacitances Propagation delay ¾ Power, Energy, and Energy-Delay ¾ Perspective: Technology Scaling and its Impact on the Inverter Metrics ¾ Introduction ¾ Static CMOS Design Complementary CMOS Ratioed Logic Pass Transistor Logic ¾ Dynamic CMOS Design 15 Dynamic Logic: Basic Principles Speed and power dissipation of dynamic logic Issues in Dynamic Design Cascading Dynamic Gates 16 7. DESIGNING SEQUENTIAL LOGIC CIRCUITS ¾ Introduction ¾ Static Latches and Registers ¾ Perspectives How to Choose a Logic Style? Designing Logic for Reduced Power Voltages The bistability principle Multiplexer-based Latches Master-Slave and Edge-Triggered FF's Low-voltage static latches Static SR Flip-Flops ¾ Dynamic Latches and Registers ¾ Alternative Register Styles 17 18 ¾ Pipelining: An Approach to Optimize Sequential Circuits ¾ Non-Bistable Sequential Circuits The Schmitt Trigger Monostable Sequential Circuits Astable Circuits Part III. A System Perspective ¾ Perspective: Choosing a Clocking Strategy 19 20 8. IMPLEMENTATION STRATEGIES FOR DIGITAL ICS 9. COPING WITH INTERCONNECTS ¾ Introduction ¾ Custom Circuit Design ¾ Cell-Based Design Methodologies Standard cell Macrocells, Megacells Semi-custom design flow ¾ Array-Based Implementation Approaches ¾ Perspective: The Implementation Platform of the Future ¾ ¾ ¾ ¾ ¾ ¾ Introduction Capacitive Parasitics Resistive Parasitics Inductive Parasitics Advanced Interconnect Techniques Perspective: Networks-on-a-chip 21 22 10. TIMING ISSUES in DIGITAL CIRCUITS ¾ Introduction ¾ Clock Skew and Sequential Circuit Performance ¾ Synchronizers and Arbiters Single-Phase Edge-Triggered Two-Phase Master-Slave Other Clocking Styles How To Counter Clock Skew Problems? ¾ Clock Generation and Synchronization ¾ Self-Timed Circuit Design Synchronizers - Concept and Implementation Arbiters Clock Generators Synchronization at the System Level ¾ Perspective: Synchronous versus Asynchronous Design Self-Timed Concept Completion-Signal Generation Self-Timed Signaling 23 24 11. DESIGNING ARITHMETIC BUILDING BLOCKS ¾ Introduction ¾ Data-paths in Digital Processor Architectures ¾ The Shifter The Adder The Binary Adder: Definitions The Full Adder: Circuit Design Considerations The Binary Adder: Logic Design Considerations ¾ Other Arithmetic Operators ¾ Power Considerations in Datapath Structures ¾ The Multiplier Barrel Shifter Logarithmic Shifter The Multiplier: Definitions The Array Multiplier Other Multiplier Structures Reducing the Supply Voltage Reducing the Effective Capacitance ¾ Perspective: Design as a trade-off 25 26 12. DESIGNING MEMORY and ARRAY STRUCTURES ¾ Introduction ¾ Semiconductor Memories - An Introduction Memory Classification Memory Architectures and Building Blocks ¾ Memory Reliability and Yield ¾ The Memory Core Read-Only Memories Non-Volatile Read- Write Memories Read-Write Memories (RAM) Signal-To-Noise Ratio Memory yield ¾ Case Studies in Memory Design ¾ Memory Peripheral Circuitry Drivers/Buffers Timing and Control The Programmable Logic Array (PLA) A 4 Mbit SRAM ¾ Perspective: Semiconductor Memory Trends and Evolutions The Address Decoders Sense Amplifiers 27 28 13. VALIDATION AND TEST OF MANUFACTUED CIRCUITS ¾ Introduction ¾ Test Procedure ¾ Design and Testability Issues in design for testability Ad Hoc testing Scan-based test Boundary-scan design Built-in Self-test (BIST) ¾ Test-Pattern Generation ¾ Fault Models ¾ Automatic Test Pattern Generation 29