view

advertisement

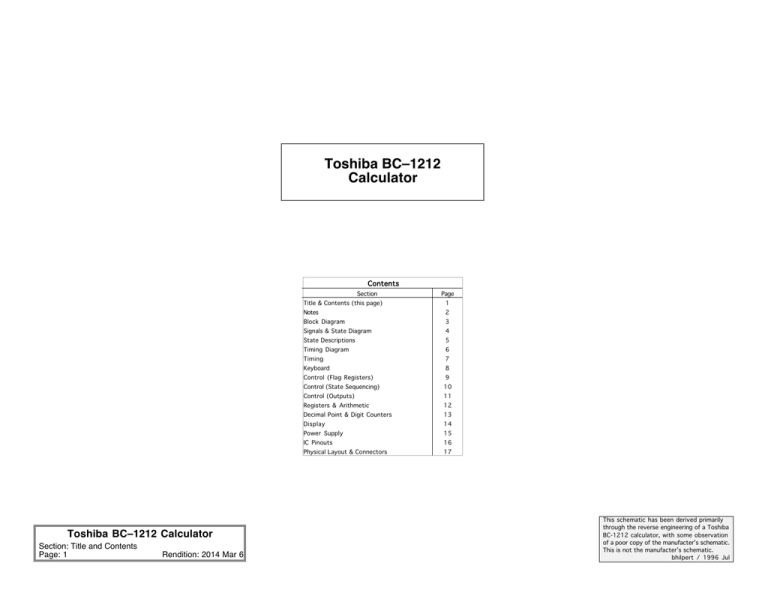

Toshiba BC–1212 Calculator Contents Section 1 Notes 2 Block Diagram 3 Signals & State Diagram 4 State Descriptions 5 Timing Diagram 6 Timing 7 Keyboard 8 Control (Flag Registers) Toshiba BC–1212 Calculator Section: Title and Contents Page: 1 Rendition: 2014 Mar 6 Page Title & Contents (this page) 9 Control (State Sequencing) 10 Control (Outputs) 11 Registers & Arithmetic 12 Decimal Point & Digit Counters 13 Display 14 Power Supply 15 IC Pinouts 16 Physical Layout & Connectors 17 This schematic has been derived primarily through the reverse engineering of a Toshiba BC-1212 calculator, with some observation of a poor copy of the manufacter’s schematic. This is not the manufacter’s schematic. bhilpert / 1996 Jul Notes Logic Implementation ♦ The symbol denotes a physical connector pin where c=connector, and pp=pin. Solid black end is the male side of the connector. White end is the female side of the connector. Most AND and OR gates are constructed from discrete diodes and resistors. Some gates, and more complex logic elements, are contained in integrated circuits. Ncpp ♦ connection between different sections. connection limited to same section. Arrows indicate direction of signal or energy flow. ♦ The symbol denotes V–24. ♦ Capacitance in microfarads unless otherwise indicated. Gate Identification Gate symbols and signal names are presented in accordance with positive logic: logic 1 = 0V, GND logic 0 = V–24 The internal construction of discrete gates is shown in the following diagrams. A wire–AND or wire–OR construction is indicated by the input line traversing the width of the gate. AND Gate OR Gate OR Gate with ‘wired’ input ♦ See www.cs.ubc.ca/~hilpert/eec for additional information. r r r Log ♦ These drawings based on unit with Serial No. 165632 z and a manufacturer schematic which appears to be dated 69/3/13. R R ♦ 1996 Jul: Initial drawing (bhilpert). 2000 Apr: State diagrams and descriptions added (bh). 2007 Jan: Some minor reorganisation of notes (bh). 2011 May: Several symbol name corrections, noticed by Pavel Zima. R Resistance (R) 33K 39K 24K 47K 100K 470K 220K 330K no resistor The TM4000 / µPD Integrated Circuit Family The integrated circuits are from an early family of MOS SSI / MSI technology produced by several Japanese manufacturers during the late 1960’s to early 1970’s. (Note these ICs are not CMOS and should not be confused with standard CMOS series ICs.) ♦ Outputs are open-collector, closing to GND (logic 1) and requiring external pulldown resistor to V–24 (logic 0). (See table above.) ♦ Inferred for flip-flops: The flip-flops in this logic family appear to be Master/Slave D-type flip-flops with the clocks for the master and slave sections kept separate. This permits a system design where data capture is done in accordance with the requirements of the logic while all outputs are changed synchronously by a single clock signal. ØC = Capture Input (master section clock) ØT = Toggle Input (slave section clock) The state of the D input is captured when ØC is logic 0 (V–24). The Q output is set in accordance with the captured state when ØT goes to logic 0. Toshiba BC–1212 Calculator Rendition: 2014 Mar 6 Gate Type ID 0 3 4 5 6 As Logic Element flip–flop inverter 2 by 2 AND–OR gate 64–bit shift register 60–bit shift register serial adder IC Type TM4103 or µPD10 µPD13 TM4005 or µPD14 TM4105 TM4106 TM4006 Some discrete gates have no distinguishing identifier. There are two ICs identified as “0–9” on the boards and in the original schematic. This schematic distinguishes them as “0–9S” and “0–9D”. Most outputs have load resistors (R) connected from the output to one side of the power supply. For outputs from integrated circuits the resistor always goes to V–24. To reduce clutter these resistors are indicated in the schematic by one of the following letters (r) in a box near the output. The letters are the same as those printed on the circuit board to identify resistor values. Symbol (r) P Q R S V Y Z n – Section: Notes Page: 2 Gates and logic elements are identified by a symbol taking one of the following forms: x/y refers to a gate constructed from discrete components x/ “ /y “ g–n refers to a gate contained within an integrated circuit where x = number printed on board beside load resistor y = number on original schematic g = gate type identifier (see table below) n = number See “Physical Layout and Connectors” page for more about IC and gate location. Original Schematic The original schematic has some errors and uses some undocumented shorthand nomenclature. ♦ Logic 1 is GND (0V), logic 0 is V–24. ♦ Signals are named in terms of positive logic. An old set of gate symbols is used. Both positive logic and negative logic gates are represented. Gate symbols with a “+” in them are positive logic gates, otherwise the gate is negative logic. AND Gate OR Gate + + Modern Symbol (Positive Logic) Old Symbol, Positive Logic Old Symbol, Negative Logic The double-ended arrows indicate identical construction, thus a positive-logic AND gate is constructed in the same manner as a negative-logic OR gate. For the most part, the control portion of the calculator is constructed in terms of negative logic, the data portion is constructed in terms of positive logic. Timing Ø C ØT Keyboard KC, KA, KAS, KX, KD, KEX, KR, KP, KPS KA, KK SC Flag SN Flag ØBn bit timing SX Flag Power Supply V+10 ØDn digit timing SD Flag V–24 V–20 V+65 V+100 V+178 V+180 logic supplies SP Flag SEX Flag SCH Flag display supplies State Sequencing Control S0 K0…K9 Numeral Encoder Y Outputs KN CY… X Outputs YCa1 Y=0 CXX CXY W Outputs X=0 CWW CWY S15 P, G, C Outputs DG=15 CGG CGC CPP CPC PCY=… CCDATA PCa CCG CCP CCNP X S Register (4 bits) Y Register (displayed operand, 60 bits) Arithmetic (BCD serial adder, 4 bits) Digit (DG) Counter DG PCY KNUM W Decimal Point (PCY) Counter Y X Register (2nd operand, 64 bits) PI W Register (accumulator, 64 bits) Y1 Y2 Y4 Y8 Toshiba BC–1212 Calculator Section: Block Diagram Page: 3 Rendition: 2014 Mar 6 Display Latch (4 bits) 1-of-10 Decoder and Drivers Overflow Driver and Indicator 12 Nixie Displays 000987654321. Decimal Point Driver Counter Adder Signal Names Section Timing State Diagram Lines represent state transitions occuring at the end of each full number cycle. Labels for these lines are the conditions under which the transition occurs. Note the condition must exist at the end of the number cycle (ØD16B8C). Signal Ø… ØC ØT ØB… ØD… ØB8C ØD16B8C Description Master timing. Master clock, data capture phase. Master clock, toggle outputs phase. Bit timing. Digit timing (4 bits constitutes a digit). Capture pulse at the end of each digit. Capture pulse at the end of each full number cycle. Keyboard K… The keyboard and numeral encoder. These signals all go to control. idle Control S…, C… SST SX SD SXD SN SC SP SCH S0…S15 CY… CX… CW… CP… CG… CC… The state machine. Flag indicating start of operation. Flag indicating a multiply operation is pending. Flag indicating a divide operation is pending. Combination of SX OR SD. Flag indicating beginning/end of operands. Flag indicating clear operation. Flag indicating addition/subtraction and DP pressed. Flag to capture data conditions during the number cycle. The states of the state machine. Outputs from control to the Y register. “ X register. “ W register. “ decimal point (PCY) counter. “ digit (DG) counter. “ adder for PCY and DG counters. 0 Y Register Y… The operand being displayed. Arithmetic is also incorporated in this register. Y1,Y2,Y4,Y8 BCD numerals on their way to the display. Y=0 YCa1 Borrow signal for the divide algorithm. X Register X… X=0 The second operand. W Register W The accumulator. PCY Counter PCY… PCY=0 PCY=5 PCY<14 PCa PI Point Counter for the Y register. The decimal point timing counter. DG Counter Digit counter. Used during multiply and divide to count digits. DG… DG=15 The SCH (presumably Catch-and-Hold) flip–flop is used to latch conditions which occur before the end of the number cycle. Labels noted with ‘*’ are conditions caught by the SCH flip–flop. The state numbers appear to have been chosen to simplify the hardware and have no symbolic relation to their place in the algorithm. Full descriptions of the activity which occurs during a state are presented in the table on the following page. ST KC C KN 11 KR PCY≠15 KAS+KEX +KM+KD KAS•SX 1 PCY≠15 15 4 PCY=15 PCY=15 SEX Y=0•DG≠15 Y≠0 7 8 Y≠0 5 Y≠0* 12 3 DG=15 • (X≠0 + PCY=5) * Y=0•DG=15 Y=0* Y=0•DG≠15 KAS•SD 13 KACC Y=0* 10 SEX 6 Y≠0* SEX YCa1 2 YCa1 14 9 DG=15 • (X≠0 + PCY=5) * Algorithm Notes The PCY and DG registers function as count–by–16 counters, thus the operations upon them are base 16. Signal to the display to turn on the decimal point at the appropriate time. ♦ A lowercase “n” in a signal name indicates the logical NOT operation. Toshiba BC–1212 Calculator Section: Signals and State Diagram Page: 4 Rendition: 2014 Mar 6 During the display state (S0) the PCY counter decrements once per digit. When the bit pattern in PCY is 15, the decimal point indicator is turned on. Consequently, the value which appears in PCY during ØD16 is the number of decimal positions currently being displayed. i.e. If there are 3 decimal positions in the display, the PCY register will contain 3 during ØD16. Negation is accomplished in the adder with no extra number cycles: • The B input to the operand adder is complemented. • Intra-digit carry in operand adder is normal due to double inversion. • Initial (beginning of number cycle) borrow of 1 is generated in operand adder. • Tens carry for sum≥16 is inverted. • Tens carry generates correction in normalisation adder of 9+1=10. 9 is from inversion of 6, 1 is from first bit carry generation in normalisation adder. • Otherwise correction is 15+1=0 Intent Register Actions PCY Counter Actions DG Counter Actions 0 Idle (display loop). – PCY – 1 → PCY each digit, when PCY =15 turn on decimal point. – C Clear just about everything. 0 → Y; 0 → X 0 → PCY – ST Start. All sequences except clear come through this state to begin. – If multiply then PCY + PS → PCY. 0 → DG 11 Numeral and decimal point entry. If numeral, then shift Y left one digit and enter keyboard numeral into LSD of Y. If SP set (DP has been pressed) and not KDP then PCY + 1 → PCY. if KDP then set SP. – First stage of aligning the entered number (Y) to the selected number of decimal point positions (PS). – During first digit, if PCa from state 1 then PCY – 2 → PCY else PCY – 1 → PCY. PCY – 1 → PCY during all other digits. – Clear excess decimal places if more decimal places were entered than are selected by the decimal point position switch. Clear digits of Y until PCY = 14 or 15. PCY – PS – 1 → PCY – Rotate Y until in proper position according to PS. PCY was prepared for this phase during state 1. Loop terminates when PCY = 15. Shift Y left one digit. PCY + 1 → PCY – 13 A somewhat overloaded state. If addition then Y + X → Y. If subtraction then X – Y → Y. If multiply or divide then Y → X. If exchange do nothing. If recall then W → Y and, if accumulate then 0 → W. PS → PCY – 12 Accumulator update. Y + W → Y; original Y → W. – – 3 Used during accumulator update. Y ↔W – – 7 During multiply, shift Y left until MSD of Y is non–zero. Shift Y left one digit. – DG + 1 → DG 8 During multiply, repeatedly add multiplicand (X) to result (Y) and decrement multiplier (MSD of Y). Loop terminates when MSD of Y = 0. Y + X → Y; ––Y(MSD) – – 5 During divide, shift Y (the dividend) left as far as possible. Shift Y left one digit. PCY + 1 → PCY – During divide or exchange, swap X and Y registers. X ↔Y If dividing then PS – PCY → PCY. If exchanging then PS → PCY. – 6 During divide, shift Y (now the divisor) left as far as possible. Shift Y left one digit. PCY + 1 → PCY – 2 During divide, repeatedly subtract divisor from dividend and increment quotient. Loop terminates when dividend goes negative (too many subtractions). Y – X → Y; ++Y(LSD) – 14 During divide, restore dividend and quotient because state 2 terminated with one extra subtraction. Y + X → Y; ––Y(LSD) PCY + 1 → PCY During divide, ? Shift digits of Y left until SCH occurs, clear other digits. – State 1 15 4 10 9 DG + 1 → DG (DG – 1 → DG 15 times) DG – 1 → DG each digit. Toshiba BC–1212 Calculator Section: State Descriptions Page: 5 Rendition: 2014 Mar 6 Note: PS = Point Set, the number of decimal positions selected by the decimal point position switch LSD = Least Significant Digit MSD = Most Significant Digit 2100 0µS 140 280 420 560 700 840 980 1120 1260 1400 1540 1680 1820 1960 2240 0µS 2100 logic 1 (0V, GND) (28.9 KHz) ØC logic 0 (–24V) ØT (7225 Hz) ØB1 ØB2 ØB4 ØB8 ØnB8C (452 Hz) ØnD1 ØnD2 ØnD16 ØnD16B8C Y and PCY with 000987654321. in the display. Y PCY Digit in register outputs, also ØDn 16 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Digit being displayed – – 1 (LSD) 2 3 4 5 6 7 8 9 10 11 12 (MSD) – – – Value in PCY at ØB8c 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 One full number cycle in registers Toshiba BC–1212 Calculator Section: Timing Diagram Page: 6 Rendition: 2014 Mar 6 ØB1 NL15 470K 82K 220K 2SA495 9 2SA495 150pF 200 4.7K pF 150pF 3–6 S 3 ØnB1 NL14 2SA495 NL11 4.7K 4.7K 82K NL17 4.7K NL10 ØC (Ø1) NL9 200 4.7K pF S 10 ØT (Ø2) NL13 S 2 3–6 7 9 ØC 3 ØT D Q ØC S 5 0–5 ØT 8 D Q ØC ØC ØT ØT S 4 10 0–5 D ØC ØC ØT ØT Q S 2 11 0–5 D ØC ØC ØT ØT Q S 1 11 ØnB8C 2SA495 3–6 NL29 S 1 ØC 0–5 150 4.7K NL18 2SA495 ØnD16 S ØC 150 8 3–6 S 4 ØnB8C ØT 7 9 3 D ØC Q S 5 0–4 8 D ØnB8C ØC ØT ØT ØT Q S 4 0–4 10 D ØnB8C ØC ØT ØT Q S 2 0–4 11 D ØnB8C ØC ØT ØT Q S 1 0–4 7 ØnB8C ØT 9 3 D ØC Q S 5 0–3 8 D ØnB8C ØC ØT ØT ØT Q S 4 0–3 10 D ØnB8C ØC ØT ØT Q S 2 0–3 11 D ØnB8C ØC ØT ØT Q S 1 0–3 NL20 ØnD1 ØnD2 ØnD3 ØnD4 ØnD5 ØnD6 ØnD7 ØnD8 2SC372 7 ØnB8C ØT 9 3 D ØC S Q 5 0–2 8 D ØnB8C ØC ØT ØT ØT S Q 4 0–2 10 D ØnB8C ØC ØT ØT S Q 2 0–2 11 D ØnB8C ØC ØT ØT S Q 1 0–2 7 ØnB8C ØT 9 3 D ØC S Q 5 0–1 8 D ØnB8C ØC ØT ØT ØT S Q 4 0–1 10 D ØnB8C ØC ØT ØT S Q 2 0–1 11 D ØnB8C ØC ØT ØT P Q 1 0–1 47K NL8 ØnD9 Toshiba BC–1212 Calculator Section: Timing Page: 7 ØB8 4.7K 4.7K Y ØB4 2SA495 47K ØnD1 ØnD2 ØnD3 ØnD4 ØnD5 ØnD6 ØnD7 ØnD8 ØnD9 ØnD10 ØnD11 ØnD12 ØnD13 ØnD14 ØnD15 ØB2 Rendition: 2014 Mar 6 ØnD10 ØnD11 ØnD12 ØnD13 ØnD14 ØnD15 NL16 ØnD16 ØnD16B8C 150 NK3 C 0 NKM 47K + 1 NKT 2 NKC S – NKV KC 7 3–1 – 5 NKB KnAS KS NKS 3 NKR 4 NKP 5 × NKL KM 47K ÷ S KMD NKK KD 47K NKN 6 NK11 7 NK10 8 NK9 9 EX NKJ NK8 KEX 0 1 2 3 4 5 6 7 8 9 NK5 10 3–2 47K – 2 KnR KR – KF DP NKU 0 2 4 NK1 9 47K K NKA – 3 KnA KK 47K Toshiba BC–1212 Calculator Section: Keyboard Page: 8 3–2 Rendition: 2014 Mar 6 S 4 ØB2 ØB4 8 S KNUM 4–3 9 11 ØB8 5 3 8 S 4–3 2 7 10 S 9 0 KN KP2 47K KP4 47K NK4 4 5 6 7 1 ØB1 KP NK2 A 2 3 6 7 S S 47K R 1 3 5 7 9 KC ØnD16B8C KF KN 10 40/44 330K SnST KMD 9 3–4 3 SnST 17/25 4/20 S D ØnD16B8C ØC ØT ØT Q S 4 S 7 3/2 SC 10 3–5 S (14) 2 SnC ØT D Q ØnD16B8C ØC ØT ØT S 5 0–7 SnST 47K KnR+SnST S 82/77 n 10 3–4 Sn11 37/42 ØC S 2 0–6 Sn0 0–6 2 5/6 S Sn8 Sn9 Sn13 83/78 n 8 ØT KK 3 Q C372 41/24 ØnD16B8C SnN SEX Sn13 9 D 2 0.001 8 KnR ØT 3–1 10 S 8 3–1 S 8 KS KP 18/4 4 9 3–4 3–1 4 4 KD KC 38/43 KM KC 16/3 39/5 KEX 11 3–4 3–2 /91 n 11 ØC D ØC ØT ØT 7 SnN 8 0–7 3–8 – 4 3–8 – 3 SN ØT ØnD16B8C n S 4 D ØnD16B8C ØC ØT ØT Q S 1 9 0–7 Q S 5 SX SX SD – 5 4 3–5 – 4 S 19/22 1 SnST 2/41 S 84/75 1/1 10 D ØnD16B8C ØC ØT ØT S Q S 2 11 3–12 1 Sn1 SnP Sn6 0–7 X=0 nDG=15 Sn9 S n 11 D S ØnD16B8C ØC ØT ØT S Q 1 Toshiba BC–1212 Calculator SnXD 64/69 36/72 66/73 65/71 SnEX Sn9 S S S S S 0–6 11 3–5 S 1 nPCY<14 Sn15 /96 n 11 ØnB8C ØT 67/68 S C372 SEX Section: Control (Flag Registers) Page: 9 Rendition: 2014 Mar 6 – 5 nPCY=5 nDG=15 Sn9 /92 KC n 3–5 SD Sn5 20/23 SXD 7 SnD 8 0–6 SnX Y=0 KF KC SN Sn0 7 S 81/74 3 Q PCa 4 3 SnST Sn0 S 9 D 68/70 S 9 3 D ØC ØT Q 0–11 S 1 SnCH 7 3–12 – 5 SCH KN 7 SnST 3–2 1 (S1) 5 SnST KnAS SnX 71/64 25/66 S S nPCY=15 9 60/35 S YCa1 11 2, 4 (S7) 4 (S5) Sn1 Sn2 3–8 1 Sn2 Sn4 nPCY=15 Sn4 SnST KnR+SnST 3 2, 8 (S11) SnST SnD Sn1 3–10 4, 8 (S13) SCH Sn5 1, 4, 8 (S13) 62/62 S 2 (S15) 2 (S2) 32/37 S 4, 8 (S14) 4 (S4) 30/32 28/33 S S 1, 8 (S13) C372 1 99/94 Z 7 1, 4 (S5) ØnD16B8C SnCH Sn5 Sn6 SCH Sn6 nY=0 DG=15 74/65 S ØT 2, 8 (S10) 29/67 S S 31/39 S /95 Z 1, 2, 4 (S7) S S SEX Sn10 Sn12 SnEX Sn13 KnA SnXD SnN SEX Toshiba BC–1212 Calculator ØT ØT V+10 0–9S 470K n2 A495 S 8 (S8) C372 1 (S1) S /97 Z 10 46/27 S D 1 (S1) ØC ØT S Q 2 V+10 0–9S 470K ØT n4 220K 34/61 26/34 S S 33/63 S n1 n2 4 8 1 2 n4 8 Q S S Q S Q Sn0 1 2 4 n8 Sn1 n1 2 4 n8 Sn2 1 n2 4 n8 Sn3 n1 n2 4 n8 Sn4 1 2 n4 n8 Sn5 n1 2 n4 n8 Sn6 1 n2 n4 n8 Sn7 n1 n2 n4 n8 Q P P P R R Sn8 Sn9 Sn10 Sn11 Sn12 Sn13 4 1 n2 n4 8 1 (S1) 2, 4 (S6) C372 1, 2 (S3) S 1 n2 4 8 n1 2 n4 8 A495 2 (S2) 8 2, 8 (S10) /98 Z 11 D ØnD16B8C ØC ØT ØT Q 0–9S S 1 V+10 470K n8 A495 8 8 1, 8 (S9) 4 (S4) SCH+Sn9 n1 n2 n4 8 n4 220K 4, 8 (S12) Sn13 Section: Control (State Sequencing) Page: 10 Rendition: 2014 Mar 6 ØC ØnD16B8C 27/36 Sn14 Sn15 ØnD16B8C 220K 4 35/31 Sn9 D S Q 4 8 (S8) Sn8 SnCH 8 1 2 4 8 n1 2 4 8 2 73/38 63/30 Sn9 470K ØT n1 A495 C372 1, 2, 4 (S7) Sn7 SCH V+10 0–9S 4 (S6) 2 59/18 nY=0 nDG=15 ØC 1 Sn8 Sn8 3 S 5 220K Sn7 Sn7 9 Q 2 (S2) 61/19 Y=0 D S Q S Sn(4+5+6+7) Q Q Sn14 Sn15 SnN Sn11 KnAS ØnD16 SnST SnX 7 SnST KP2 ØB2 KP4 ØB4 8 3–8 5 4–21 9 S 7 11 8 10 3–16 4 12/14 ØnD16 Sn1 23/28 ØnD16 Sn10 ØnD1 Sn10 KP ØnB1 ØnD16 SnP Sn11 Sn13 ØnB1 ØnD1 Sn14 11 SnCH ØnB1 ØnD1 3–1 1 Sn14 51/53 S 11 3–4 1 Sn15 KP Sn11 SnCH SC Sn0 ØnB1 ØnD16 Sn(4+5+6+7) ØnD1 13/15 S 52/55 Sn15 S KR SN SX SD SEX Sn13 S S KnR Sn13 56/29 S KP SN Sn11 Sn9 54/57 24/13 S 89/90 Z 8 3–12 S 4 S ØnD1 S ØnD16 Sn8 KNUM S 57/60 91/85 n 9 3–12 S 3 CGC CCG CPP 92/84 n 3–2 47/49 50/12 48/50 S S 7 S Sn3 Sn12 85/79 S Sn(4+5+6+7) SCH+Sn9 87/81 Sn12 S 95/87 96/88 72/52 n 10 n 9 n 11 n 9 3–18 S 5 CYAX 3–18 S 2 CYAW 3–18 S 3 CYAS 3–16 S 1 CYBX 3–16 S 3 CYBY S S 97/89 4 CYAY Sn13 n CYBINJ S SnN+Sn11 SnC Sn13 58/17 98/82 n SnP Sn12 49/51 70/40 S S Sn2 /93 SXD SnP Sn13 69/100 KK SnN Sn11 7/ SX SnN Sn11 8/7 KR SN SnXD SEX Sn13 9/8 KnR KnA Sn13 43/47 CYPN CCP CCNP S SnC Sn10 88/99 S n CXX 8 3–18 S 4 3–18 S 1 CXY S S 94/86 Sn3 Rendition: 2014 Mar 6 Z S CGG S Toshiba BC–1212 Calculator Section: Control (Outputs) Page: 11 8 Sn14 SnST ØnD16 SEX Sn10 6/10 S CPC (1 during idle state) Sn10 44/46 n Sn11 11/54 Sn7 Sn8 Sn9 ØnD16 10/11 86/80 S Sn2 42/59 45/48 S Sn2 Sn8 Sn10 Sn14 KR 53/58 21/26 SnN+Sn11 SnC Sn(4+5+6+7) Sn9 Sn10 S CCDATA Sn13 55/58 22/9 Sn12 93/85 n n CWW 11 CWY 1 CYAS X CYAX 4 W CYAW X CYBX ØT S ØnD1 2 ØT ØC ØC ØT ØT Q S 4 10 0–23 D Q ØC ØC ØT ØT S 2 11 0–23 D Q ØC ØC ØT ØT operand adder 9 10 2 7 S 11 10 3–16 NL26 3 4 2 An 1 nNEG S 11 Σn 5 2 S 5 ØC ØT 10 8 Cn–1 As1 Cn ØC S 11 ØT ØC 9 3 ØC Q S 1 10 0–10 ØT Y8 Cn–1 S OUT 7 D ØC ØC ØT ØT Q S 2 8 0–10 Y4 D Q ØC ØC ØT ØT S 4 7 0–10 Y2 D Q ØC ØC ØT ØT 8 10 YCa1 ØT ØT 0–11 NL23 normalization adder S 5 2 3 0–10 S 4 ØnB1 4 ØB2 S 7 NL30 α n 10 CYBINJ ØnB8C ØC ØT ØT 0–11 4–21 β 3 S Q 2 D 11 10 8 An 1 nNEG Σn S 5 8 IN Bn ØC Cn–1 As2 Cn 11 6 9 ØT ØC OUT Y 6–7 (60 bits) S NL19 2 Y ØT Cn–1 S OUT 7 ØC ØT 6 generator 4–8 S 5 2 Y1 Y2 Y4 Y8 NL22 1 ØB4 2SC372 S NL27 47K nY=0 10 3–8 – 2 Y=0 Ca 4–17 S 7 7 10 ØC ØT 9 3 D ØC ØT Q 0–22 S 5 8 D ØC ØC ØT ØT Q 0–22 S 4 10 D Q S 2 11 D ØC 0–22 ØC ØC ØC ØT ØT ØT ØT S CWY ØC Y1 tens-carry detector and latch NL21 11 9 ØnB8C S 5 ØT NL28 8 10 Q ØC tens carry 11 D ØT 3 9 D Bn 4–8 Y8 Y 0–23 NL24 4–15 Y4 CWW S 1 7 9 CXY 0–23 D CYPN Y2 Y 8 5 bit carry CXX ØC S 5 NL25 1 4 ØnB1 3 Q 4–19 1 ØB1 9 D 3 CYBINJ n ØC 3 8 CYBY CYAS 5 4 CYAY n 7 4–17 2 Q S 1 8 0–22 ØC ØT 7 3–16 S 5 IN OUT V 2 X OUT V 2 W X 6–24 6 Ø C (60 bits) 9 ØT X=0 4–19 S 7 8 8 ØC ØT Toshiba BC–1212 Calculator Section: Registers and Arithmetic Page: 12 Rendition: 2014 Mar 6 IN W 5–25 6 Ø C (64 bits) 9 ØT 3 CGG 4–14 4 S 5 1 CGC 7 2 ØC ØT 9 3 D ØC Q S 5 0–13 ØT 8 D ØC ØC ØT ØT Q S 4 0–13 10 D ØC ØC ØT ØT Q S 2 0–13 11 D ØC ØC ØT ØT Q S 1 DG 0–13 n 10 S 2 3–10 1 nDG=15 11 3–10 – 1 DG=15 CCG 4 CCP 10 CPP 11 9 CPC CCNP 4–14 S 7 7 8 ØC ØT 9 3 D ØC Q 0–20 ØT S 5 8 D ØC ØC ØT ØT Q 0–20 S 4 10 D ØC ØC ØT ØT Q 0–20 S 2 11 D ØC ØC ØT ØT n Q S 1 58/17 S 10 3–12 2 3 CCDATA 0–20 n 4 ØnB1 7 3–10 5 n nPCY<14 8 8 Toshiba BC–1212 Calculator S 2 2SC372 Section: Decimal Point and Digit Counters Page: 13 Rendition: 2014 Mar 6 5 3 PCY nPCY=5 n 4–15 2 S 4 3–10 D ØnB8C ØC ØT ØT Q 0–11 S 4 nPCY=15 NL32 PI ØC ØT 10 8 An 1 nNEG S Σn 5 Bn Cn–1 ØC ØT As3 Cn S 11 Cn–1 S OUT 7 PCa V+65 150K ND32 V+65 2SC780 Y8 11 D ØnB8C ØC ØT ØT Q S 1 47K 8 2SC372 0–9D n2 150K n8 150pF 100K n4 V+65 n8 V–20 150K ND29 2 2SA495 Y4 ØnB8C D ØC ØT 47K 150K n4 V+65 0–9D n4 47K ØnB8C ØC ØT ØT Q S 4 0–9D 470K 2SC495 S 7 3–6 n2 S 5 ØnD1 ØnD14 ØnD15 ØnD16 Y 2SC780 100K 18K ND7 2SC780 OVER FLOW 8 47K 150K V+10 470K 2SC495 470K 2SC372 330K n1 47K 1 47K 470K 2SC372 47K Y1 ØnB8C ØT 7 9 3 D ØC Q S 5 0–9D V–20 ØT 470 2SC780 PI Toshiba BC–1212 Calculator Section: Display Page: 14 ND22 2SC780 150pF V–20 ND23 V+65 2SC780 Rendition: 2014 Mar 6 NL31 100K V–20 10K 150pF 150K V+65 V+100 1 3 5 7 9 NEC LD–955A 0 2 4 6 8 . 150K 47K 5.6K ND8 ND24 V+65 V+180 0.022 470K 150K 4 2SA429 ND25 V+65 47K 150pF 47K 2SC372 33K 2SC780 2 DIGITS 11 to 1 (LSD) V+178 ØnD13 150K 330K V+180 2SC780 V+65 2 V+10 ND26 47K 4 D DIGIT 12 (MSD) 150K 150pF V–20 8 ND27 V+65 2SC780 n2 The 200V rating of the original 0.022 capacitors is inadequate (204V in use). Failure of the capacitors can result in blown ICs. These capacitors should be replaced with units with a 250V or greater rating. 150K 100K Y2 2SC780 150pF ØT ND28 4 S Q 2 V–20 2SC372 ATTENTION V+65 2SC780 10 ND30 2SC780 ND31 Drive Digit Connection ØnD2 1 ND21 ØnD3 2 ND20 ØnD4 3 ND18 ØnD5 4 ND17 ØnD6 5 ND16 ØnD7 6 ND14 ØnD8 7 ND13 ØnD9 8 ND12 ØnD10 9 ND11 ØnD11 10 ND10 ØnD12 11 ND9 NKD NL1 ND2 2 of 1N3195 4.7 150V 83V ND5 4.7 250V 470K 220 43K 4.7 150V black NKE POWER 3.9K 2W NL2 33K 1S136 2K 2K yellow 2SA495 brown NKF NL3 ND3 0.5 AMP NL4 NL5 V–20 2SA495 330 2K 50V 47 2SD130 ND15 470 12 10 10 12 TM4103M µPD10 3–n 4–n 5–n 6–n Asn µPD13 TM4005M µPD14 TM4105M TM4106M TM4006M 6 6 5 5 6 V+10 NL6 10K 47 4 of 1N3193 V+65 ND19 5.6K 12 0–n V+100 0.022 200V 0.1 2K 27V 240mA NKH 0.022 200V 6.2K 2K 5.6K 0.022 12 V+178 18K ND1 white 117 VAC V+180 10 15V 10 V–24 NL7 0–1 0–2 0–3 0–4 0–5 0–6 0–7 0–9S 0–9D 0–10 0–11 0–13 0–20 0–22 0–23 3–1 3–2 3–4 3–5 3–6 3–8 3–10 3–12 3–16 3–18 4–3 4–8 4–14 4–15 4–17 4–19 4–21 5–25 6–7 6–24 As1 As2 As3 ND4 Unused Gates 9 Toshiba BC–1212 Calculator Section: Power Supply Page: 15 Rendition: 2014 Mar 6 3–5 3 12 11 10 9 8 7 12 Toshiba 0V TM4103M NEC µPD13 NEC id: 3 µPD10 11 10 9 8 3 4 9 12 11 10 0V Cn Out ØC Toshiba TM4006M id: As 2 5 6 D D Q Q D D ØT Q Q ØC 8 7 10 ØT Cn–1 Out 0V Toshiba TM4105M Serial Adder An nNEG In 1 2 3 4 5 6 3 4 9 8 7 ØT Serial In 5 1 2 6 10 ØC 0V 5 Equivalent Internal Structure of TM4006 Serial Adder 2 An 3 Bn Sn 5 4 C n–1 Cn 11 D Q Cn–1 7 1 nNEG ØC ØT ØC Toshiba BC–1212 Calculator Section: IC Pinouts Page: 16 Rendition: 2014 Mar 6 2 3 4 5 9 8 7 7 –24V 1 TM4106M ØT 10 8 ♦ Logic 1 = 0V Logic 0 = –24V ♦ Outputs are open-collector, closing to 0V (logic 1) and requiring external pull-down resistor to –24V (logic 0). ØT Serial In 6 ØC 60-bit Shift Register Serial Out –24V 4 8 id: 4 6 id: 6 3 9 µPD14 Toshiba Serial Out 10 NEC 64-bit Shift Register id: 5 Bn Cn–1 Sn In In Out –24V 2 11 0V TM4005M –24V 1 12 Toshiba id: 0 1 7 0V 1 2 –24V 3 4 5 6 Connectors ND1 NK NL KK A 1 KP2 1 xfmr hi-V 1 xfmr hi-V KS B 2 KP4 2 xfmr hi-V 2 xfmr hi-V 3 kybd GND 3 xfmr lo-V 3 xfmr lo-V 4 KA KADD C xfmr hi-V D 4 xfmr lo-V 4 xfmr lo-V xfmr hi-V E 5 KR 5 V+10 5 V+180 xfmr lo-V F 6 – 6 GND 6 – xfmr lo-V H 7 – 7 V–24 7 overflow 8 key 9 8 ØnD15 8 digit 12 KEX J KD K 9 key 8 9 ØB8 9 digit 11 KX L 10 key 7 10 ØB4 10 digit 10 K C M 11 key 6 11 ØB2 11 digit 9 key 5 N 12 – 12 – 12 digit 8 key 4 P 13 – 13 ØT 13 digit 7 key 3 R 14 – 14 ØnB1 14 digit 6 key 2 S 15 – 15 ØB1 15 V–24 key 1 T 16 – 16 ØnD16 16 digit 5 17 Ø C 17 digit 4 18 ØnD16B8C 18 digit 3 19 Y 19 GND 20 ØnD1 20 digit 2 21 Ca 22 β 21 digit 1 23 SYPN delayed 23 numeral 8 24 SYPN 24 numeral 7 25 Y op adder, A in 25 numeral 6 26 Y op adder, B in 26 numeral 5 KP U 17 – key 0 V 18 – 27 numeral 4 28 Ca1 28 numeral 3 29 ØnB8C 30 α 29 numeral 2 31 – 31 decimal point 32 PI 32 numeral 0 30 numeral 1 0–5 digit drivers 3–6 0–3 6–7 Middle Board (top view) 0–4 AS2 AS1 4–8 numeral drivers 1-of-10 numeral decoder 0–9D ND32 NL32 0–10 5–25 6–24 4–21 4–19 Lower Board (top view) 0–23 0–20 0–22 NL1 AS3 4–17 0–13 4–14 4–15 3–18 3–10 3–16 3–12 ØnB1 0–11 89/90 ØnD1 ØnD16 SnCH 3–1 Sn15 bottom top NKA NK1 Sn12 Sn(4+5+6+7) Sn48 3–2 NK5 Sn8 KC NK8 Note: ♦ Italicised expressions are connections with no signal name in the schematic. NK11 Sn4 4–3 SEX SnX Toshiba BC–1212 Calculator Section: Physical Layout and Connectors Page: 17 Rendition: 2014 Mar 6 NL1 0–2 22 numeral 9 27 nY=0 master clock 0–1 ND NKV SnN SnST – 3–4 3–5 0–6 /95 /97 /98 Sn0 99/94 0–9S NL32 3–7 3–8