Diode-Transistor Logic (DTL)

advertisement

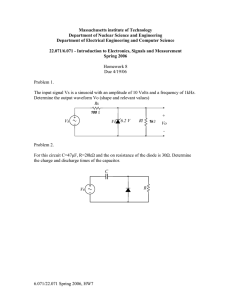

Diode-Transistor Logic (DTL) University of Connecticut 56 Diode Logic VA VB OR GATE n n n VOUT AND GATE VA VCC VOUT VB Diode Logic suffers from voltage degradation from one stage to the next. Diode Logic only permits the OR and AND functions. Diode Logic is used extensively but not in integrated circuits! University of Connecticut 57 Level-Shifted Diode Logic AND GATE VA VB With either input at 0V, Vx=0.7V, DL is just cut off, and VOUT=0V. VCC=5V RH x VOUT DL RL With both inputs at 1V, VX=1.7V and VOUT=1V. With VA=VB=5V, both input diodes are cut off. Then VOUT n n n VCC − 0.7V = RL RH + RL Level shifting eliminates the voltage degradation from the input to the ouput. However, the logic swing falls short of rail-to-rail, and the inverting function still is not available without using a transistor! University of Connecticut 58 Diode-Transistor Logic (DTL) VCC VA RC VB VC n n n n VOUT Primitive Precursor to DTL Q1 If any input goes high, the transistor saturates and VOUT goes low. If all inputs are low, the transistor cuts off and VOUT goes high. This is a NOR gate. “Current Hogging” is a problem because the bipolar transistors can not be matched precisely. University of Connecticut 59 Diode-Transistor Logic (DTL) VCC RB RC VOUT VA VB Improved gate with reversed diodes. Q1 VC n n n n If all inputs are high, the transistor saturates and VOUT goes low. If any input goes low, the base current is diverted out through the input diode. The transistor cuts off and VOUT goes high. This is a NAND gate. The gate works marginally because VD = VBEA = 0.7V. University of Connecticut 60 Diode-Transistor Logic (DTL) VCC RB VA RC VOUT x VB VC n n n Basic DTL NAND gate. Q1 RD If all inputs are high, Vx = 2.2V and the transistor is saturated. If any input goes low (0.2V), Vx=0.9V, and the transistor cuts off. The added resistor RD provides a discharge path for stored base charge in the BJT, to provide a reasonable tPLH. University of Connecticut 61 DTL VTC VCC VOUT VA VOUT x VB VC 4 RC RB 5 Q1 3 2 1 RD 0 0 n VOH = VIL = VOL = VIH = 1 2 3 4 5 VIN The noise margins are more symmetric than in the RTL case. University of Connecticut 62 DTL Power Dissipation RB=3.4kΩ RC=4.8kΩ RD=1.6kΩ VCC RC RB VA VOUT x VB VC PL = Q1 RD PH = n Scaling RB and RC involves a direct tradeoff between speed and power. University of Connecticut P= 63 DTL Fanout RB=3.4kΩ RC=4.8kΩ RD=1.6kΩ βF=50 RB VA x RC VOUT VB VC n Q1 RD Good fanout requires high β F, large RD /RB. University of Connecticut I CS = VCC I BS = I CS = N max = 64 930 Series DTL (ca 1964 A.D.) βF=50 VCC n 1.75kΩ 6kΩ 2kΩ VA Q1 VB VC University of Connecticut VOUT Q2 5kΩ n One of the series diodes is replaced by Q1, providing more base drive for Q2 and improving the fanout (Nmax = 45). Does Q1 saturate? 930 DTL Characteristics 5.0V / 0.2V VOH / VOL 1.5V / 1.4V VIH / VIL 45 Fanout 10mW Dissipation 75ns tP 65 930 DTL Propagation Delays βF =50 CL=5pF VCC 1.75kΩ 6kΩ Q1 VB VC tPLH >> tPHL n tPLH = tS+tr /2 ts = 2kΩ VA n VOUT Q2 5kΩ tr ≈ University of Connecticut 66 Transistor-Transistor Logic (TTL) University of Connecticut 67 Why TTL? VA VB n The DTL input uses a number of diodes which take up considerable chip area. n In TTL, a single multi-emitter BJT replaces the input diodes, resulting in a more area-efficient design. n DTL was ousted by faster TTL gates by 1974. DTL VC VA VB VC University of Connecticut TTL 68 Basic TTL NAND Gate. VCC=5V RB ALL INPUTS HIGH. • QI is reverse active. • QO is saturated. • VOL = VCES RCP VOUT D1 VA VB VC n QO QI RD n ANY INPUT LOW. • QI is saturated. • QO is cut off. • VOH = VCC Multi-emitter transistor. Forward-biased emitter base junctions override reverse-biased junctions in determining the base and collector currents. University of Connecticut 69 TTL Switching Speed: tPLH n VCC=5V RC RB VA VB VC QI RCP n VOUT QS n QO RD CL n The depletion capacitance of the QI EB junction must discharge; Base charge must be removed from the saturated QS; Ditto for QO; and The capactive load must be charged to VCC. Multi-emitter transistor. Forward-biased emitter base junctions override reverse-biased junctions in determining the base and collector currents. University of Connecticut 70 TTL Switching Speed: tPLH n VCC=5V RC RB VA VB VC n QI RCP n VOUT QS QO RD CL The time required to discharge the QI depletion layers is << 1ns. The time required to extract the QS base charge is also << 1ns: • QI becomes forward active; • |IBR| becomes large for QS Removal of base charge from QO is similar to the DTL case. With RD = 1 kΩ, ts = 10ns (these are typical values for 7400 series TTL). University of Connecticut 71 TTL Switching Speed: tPLH VOUT 5 VCC=5V 4 RC RB RCP 3 VA VB VC QI VOUT QS QO RD CL 2 1 t (ns) 0 0 n 100 200 300 Charging of the capacitive load can be slow with “passive pullup.” e.g., with a 5kΩ pull-up resistor and a 15 pF load (ten TTL gates) RC = 75 ns and tr = 2.3RC = 173 ns! University of Connecticut 72 TTL with Active Pullup n n In the previous example, the dominant switching speed limitation was the charging of capacitive loads through the pullup resistor. A small pullup resistance will improve the switching speed but will also increase the power and reduce the fanout. VCC With active pullup, we can achieve the best of both worlds: RC n QP VOUT QO RD University of Connecticut n When the output is low, QP is cutoff, minimizing the power and maximizing the fanout; when the output goes high, QP becomes forward active to provide maximum drive current for a quick rise time. 73 TTL with Active Pullup n n With a high output, n QS is cutoff n QP is forward active With a low output, n QS is saturated n QP should be cutoff The low output case is unsatisfactory with this circuit: VBP = VCC=5V RC RB VA VB VC QI QS QP VOUT QO RD VEP = VBEP = The “Totem Pole Output” solves this problem. University of Connecticut 74 TTL with “Totem Pole Output” VCC=5V RC RB n RCP n QP VA VB VC QI n QS DL VOUT QO During turn-off, QS switches off before QO. QP begins to conduct when VCS = VCESO+VD+VBEAP = 1.6V Initially, I BP = RD RCP limits the collector current to a safe value. University of Connecticut 75 Typical 74xx Series TTL VCC=5V 4kΩ 1.6kΩ 130Ω QP VA VB VC QI QS QO 1kΩ 1/3 T. I. 7410 triple 3-input NAND University of Connecticut DL VOUT 74xx TTL Characteristics 12 ns tPLH 8 ns tPHL 10 Fanout 10 mW Dissipation 100 pJ PDP The anti-ringing diodes at the input are normally cut off. During switching transients, they turn on if an input goes more negative than -0.7V. 76 Standard TTL: VTC β F =70 β R = 0.1 VCC=5V RC 1.6kΩ 4kΩ n 130Ω VIN=0. QI is saturated; QS, QO are cutoff; QP is forward active. VOH = QP VIN QI QS QO 1kΩ 1/6 NSC 7404 Hex Inverter University of Connecticut (the drop in the base resistor is small) DL VOUT n First Breakpoint. QS turns on. VIL = (at the edge of conduction, IC=0) 77 Standard TTL: VTC β F =70 β R = 0.1 VCC=5V RC 1.6kΩ 4kΩ n VIN = 130Ω VOUT = QP VIN QI QS DL VOUT QO 1kΩ Second Breakpoint. QO turns on. n Third Breakpoint. QO saturates. VIH = 1/6 NSC 7404 Hex Inverter University of Connecticut 78 Standard TTL: VTC 1/6 NSC 7404 Hex Inverter VCC=5V RC 1.6kΩ 4kΩ 130Ω QI QS DL VOUT QO β F =70 β R = 0.1 1kΩ VNML = University of Connecticut 5 4 3 QP VIN VOUT 2 1 0 VIN 1 2 3 4 5 VNMH = 79 Standard TTL: Low State ROUT collector current (mA) 100 2.4 mA 2 mA 1.6 mA 80 1.2 mA 0.08V 60 0.8 mA 21 mA 40 IB = 0.4mA 20 Characteristics for a 0 Texas Instruments junction isolated digital npn BJTat 25 oC. University of Connecticut 0 0.1 0.2 For the saturated BJT with IB = 2.4 mA, the output impedance is 0.3 0.4 0.5 collector-emitter voltage (V) ROL = The very low output impedance means that noise currents are translated into tiny noise voltages. Thus only a small noise margin is neccesary. 80 Standard TTL: Input Current 1/4 TI 7400 Quad VCC=5V 2-input NAND RC 1.6kΩ 4kΩ IIH n (QI is reverse active) I BI = 130Ω QP VA VB QI β F =70 β R = 0.1 QS DL VOUT I IH = QO 1kΩ n IIL (QI is saturated) I IL = University of Connecticut 81 Standard TTL: DC Fanout 1/4 TI 7400 Quad VCC=5V 2-input NAND RC 1.6kΩ 4kΩ With high inputs, n I CI = 130Ω I CS = QP VA VB QI β F =70 β R = 0.1 QS DL VOUT QO 1kΩ I BO = n To keep QO saturated, N max = AC considerations usually limit the fanout to a much lower number. University of Connecticut 82 Standard TTL: DC Dissipation 1/4 TI 7400 Quad VCC=5V 2-input NAND RC 1.6kΩ 4kΩ 130Ω QP VA VB QI β F =70 β R = 0.1 N = 10 PH = QS DL VOUT PL = QO 1kΩ P= University of Connecticut 83 Advanced TTL Designs n Schottky Clamping. QS and QO may be Schottky clamped, preventing saturation. This greatly improves tPLH. n Darlington Pullup. The Darlington pullup arrangement increases the average output drive current for charging a capacitive load. Although RCP limits the maximum output current, this maximum drive is maintained over a wider range of VOUT than with a single pullup transistor. n Squaring Circuit. Active pull-down for the base of the output transistor squares the VTC, improving the low noise margin. An added benefit is faster charge removal for the output transistor. n Improved Fabrication. Smaller devices, and oxide isolation, have steadily reduced parasitic capacitances and reduced RC time constants. University of Connecticut 84 Darlington Pullup VCC=5V RC RCP 900Ω n n 50Ω QP QP2 REP 3.5kΩ VOUT n n QP2 is added, forming a Darlington pair with QP. The EB junction of QP2 introduces a 0.7V level shift, so DL can be eliminated. QP2 can not saturate, so Schottky clamping is not neccessary. REP is needed to provide a discharge path for QP2 base charge. The Darlington emitter follower provides a very low output impedance, approaching RC /β 2. This greatly reduces the rise time. University of Connecticut 85 Squaring Circuit VOUT VOUT QS QO RBD 500Ω 5 VOH 4 BP2 3 RCD 2 250Ω QD 7400 74S00 VIL VOL BP3 1 0 1 VIH n n n n 2 3 4 VIN 5 There is no path for QS emitter current until QD and QO turn on. QS and QO begin to conduct simultaneously. BP1 is eliminated from the VTC; in other words, the VTC is “squared.” VIL is increased, improving the low noise margin. University of Connecticut 86 Schottky TTL (74S / 54S Series) 1/4 74S00 quad 2-input NAND RB VCC=5V RC 2.8kΩ RCP 900Ω 50Ω QP QP2 VA QI Features: QS REP n n n n n 3.5kΩ VB VOUT QO RBD 500Ω RCD 250Ω QD Performance: n n n University of Connecticut Schottky clamping Schottky anti-ringing diodes Darlington pullup circuit Squaring circuit Scaled resistors P = 20 mW tP = 3 ns (15 pF) PDP = 60 pJ 87