CMOS Process Flow: Micro- and Nanofabrication

advertisement

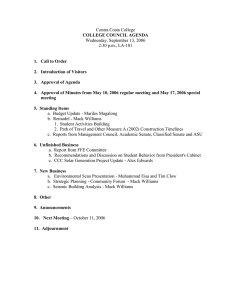

9/6/2013 CHE323/CHE384 Chemical Processes for Micro- and Nanofabrication Basic CMOS Process Flow 0. 1. 2. 3. 4. 5. 6. 7. 8. 9. Lecture 9 CMOS Process Flow Chris A. Mack Adjunct Associate Professor Reading: Chapter 16, Fabrication Engineering at the Micro- and Nanoscale, 4th edition, Campbell © Chris Mack, 2013 (some images obtained from Wikimedia Commons) 1 Wafer Prep: Laser Scribe, Clean, gettering, 0th layer Alignment Marks N-Well and P-Well Diffusion Active Area Polysilicon Gate Lightly Doped Drain (LDD) Source-Drain Implant/Diffusion Salicide Formation/Contact Holes Tungsten plugs + First Level Metallization Additional Metal Layers Passivation Layer and Bonding Pads © Chris Mack, 2013 1. N-Well Diffusion © Chris Mack, 2013 2. Active Area 3 © Chris Mack, 2013 4 4. n+ Source-Drain Diffusion 3. Poly Gate © Chris Mack, 2013 2 5 © Chris Mack, 2013 6 1 9/6/2013 5. p+ Source-Drain Diffusion © Chris Mack, 2013 6. Contact Holes 7 7. First Level Metallization © Chris Mack, 2013 9 © Chris Mack, 2013 10 Lecture 9: What have we learned? • Most devices require multiple levels of metallization • Be able to list the basic steps in the CMOS process flow • Given a list of processes steps, put them in the correct order • Be able to find the transistors when looking at a top-down design view – Deposit interlayer dielectric (ILD) – Pattern vias and trenches – Fill with copper Source: IBM, 2005 8 Cross-Section and Top Down More Process Steps © Chris Mack, 2013 © Chris Mack, 2013 11 © Chris Mack, 2013 12 2