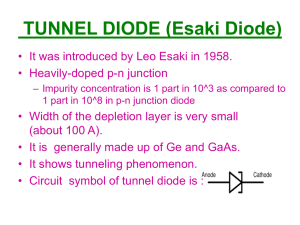

silicon/silicon-germanium heterostructure tunnel diodes

advertisement