Chapter 2 Digital Circuits (TTL and CMOS) (Based on Chapter 3

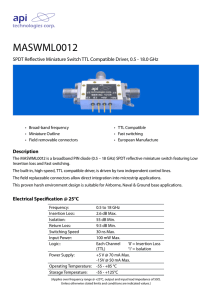

advertisement

EE201L_ClassNotes_Ch2.fm

Chapter 2

Digital Circuits (TTL and CMOS)

(Based on Chapter 3 Digital Circuits in Wakerly)

1

Logic Signals and physical phenomena representing them

Compared to ANALOG, DIGITAL STORAGE and RETRIEVAL and

DIGITAL COMPUTATION are more RELIABLE and REPEATABLE

because of the NOISE IMMUNITY of digital circuits.

Representation of digital signals (1, 0) in different technologies: (Table 3.1 of Wakerly)

1/15/07

CMOS

0-1.5V

3.5-5.0V

TTL

0-0.8V

2.0-5.0V

EE201L Class Notes - Chapter #2 Page 1 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

2

Logic Signal Levels: Consider TTL logic signal levels.

0 - 0.8V represents signal LOW condition (i.e. LOGIC 0).

So, whether the signal is 0.3V or 0.5V or 0.7V, it is UNAMBIGUOUSLY

interpreted by any gate receiving this signal as LOW or LOGIC 0.

0V ZERO VOLTS is the IDEAL value for LOGIC 0.

5V FIVE VOLTS is the IDEAL value for LOGIC 1.

A gate, apart from performing its LOGIC FUNCTION, serves as a BUFFER

AMPLIFIER to REGENERATE "WEAK" (not so ideal) input signals into

"STRONG" (nearly ideal) output signals.

2.8V

Logic 1

3.2V

Logic 1

Noise

3.6V

2.6V

Logic 1 Ohmic Logic 1

Drop

0.4V

Logic 0

Note: Any signal in the range of 2.0V-5.0V is an ACCEPTABLE

HIGH (LOGIC 1) at the input of any TTL gate.

As can be seen from the Table 3.1 on the previous page, logic can be implemented

in a variety of technologies. In fact logic gates can be implemented in pneumatic and

hydraulic systems for special purpose applications in hazardous areas in petrochemical plants. For this course, we need to study only TTL and CMOS (mostly TTL).

1/15/07

EE201L Class Notes - Chapter #2 Page 2 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

3

Major Logic families: TTL and CMOS

TTL (Transistor-Transistor Logic):

Introduced in 1960. Became very popular but gradually replaced by CMOS.

CMOS (Complementary Metal-Oxide Semiconductor):

Uses both NMOS and PMOS transistors in complementary fashion.

Supplanted TTL, thanks to its superior speed and low power consumption.

Some more families:

NMOS (N-Channel Metal-Oxide Semiconductor): Uses only NMOS transistors.

ECL (Emitter Coupled Logic):

Very fast bipolar logic but consumes too much power and hence not used.

4 Subfamilies:

TTL and CMOS have several subfamilies

some consuming more power and faster and

some consuming less power and slower.

The low-voltage subfamilies use an operating voltage lower than 5V.

For example, 3.3V LVTTL (low-voltage TTL)

and 1.8V LVCMOS (low-voltage CMOS).

5

Various CRITERIA to choose a particular logic family to suit an application:

SPEED

POWER DISSIPATION

COST

AVAILABILITY (popularity and breadth)

FANOUT (Load Handling Capability)

1/15/07

EE201L Class Notes - Chapter #2 Page 3 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

6

TTL Characteristics:

We cover here only the EXTERNAL CHARACTERISTICS of TTL gates.

The internal design details are not in the scope of this course.

6.1

VOLTAGE and CURRENT:

Question: Is a signal

a VOLTAGE or a CURRENT ?

Answer:

Analogy between an electrical system and a hydraulic system:

VOLTAGE is similar to ______________ water PRESSURE / water FLOW.

CURRENT is similar to ______________ water PRESSURE / water FLOW.

Difference between a 12V CAR BATTERY and

a stack of eight 1.5V D-CELLs?

1.5V

1.5V

1.5V

1.5V

1.5V

1.5V

1.5V

1.5V

12 V

Difference between ordinary Alkaline rechargeable batteries you use in a calculator and the heavy duty NiMH (Nickel-Metal Hydride) batteries used in Digital Cameras?

For electric wires, where/when do you need more insulation

and when do you need thicker copper wire?

When you travel to Europe, before plugging in your Blow Dryer into the outlet near

the bathroom sink, you need to know its VOLTAGE requirement

and its CURRENT requirement.

1/15/07

EE201L Class Notes - Chapter #2 Page 4 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

Which of the two (VOLTAGE and CURRENT)

a fixed item and which is a variable?

Car batteries are usually rated 12V 400A.

What happens if you are just using a small cabin light?

Ohms law:

I=V/R

Please understand the difference between current capability of the battery and the

actual current delivered to a specific load.

1/15/07

EE201L Class Notes - Chapter #2 Page 5 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

6.2

EXTERNAL CHARACTERISTICS of TTL gates represent the parameters

of the gates you (the board-level designer) need to know to successfully complete

your design. They vary from family to family. We chose to cover TTL characteristics.

6.2.1

SUPPLY VOLTAGE VCC = 5V -+ 0.25V (Max 5.25V, Min. 4.75V)

6.2.2

VOH

and VIH

For HIGH signal, HIGHER the BETTER!

VIH

VOH

MINIMUM (GUARANTEED)

HIGH OUTPUT VOLTAGE

2.4V

MINIMUM VOLTAGE

GUARANTEED TO BE

RECOGNIZED AS

"HIGH" INPUT

2.0V

Compatibility

Requirement

VOH > VIH

6.2.3

VOL

and VIL

For LOW signal, LOWER the BETTER!

VIL

VOL

MAXIMUM LIMIT OF

OUTPUT VOLTAGE FOR

LOW LEVEL OUTPUT

0.4V

1/15/07

MAXIMUM VOLTAGE

GUARANTEED TO BE

RECOGNIZED AS

"LOW" INPUT

Compatibility

Requirement

VOL < VIL

EE201L Class Notes - Chapter #2 Page 6 / 40

0.8V

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

6.2.4

IOH

and IIH

Capability shall be as _______ (high/low) as possible.

Demand shall be as _______ (high/low) as possible.

IIH

IOH

MAXIMUM CURRENT

MAXIMUM ACCEPTABLE

CONSUMPTION

CURRENT LOADING

WHEN INPUT IS

(= MINIMUM ASSURED

AT HIGH LEVEL

CURRENT OUTPUT

+ 40uA

CAPABILITY)

Compatibility

UNDER HIGH LEVEL Requirement

CONDITION

IOH > IIH

So

Ca ur c

pa i ng

bil

ity

- 0.4mA

6.2.5

IOL

Capability should exceed demand.

and IIL

IIL

IOL

Sin

C a ki n

pa g

bi l

ity

MAXIMUM ACCEPTABLE

CURRENT LOADING

(= MINIMUM ASSURED

CURRENT SINKING

CAPABILITY)

Compatibility

UNDER LOW LEVEL Requirement

CONDITION

IOL > IIL

MAXIMUM CURRENT

"THROWN OUT"

WHEN INPUT IS

AT LOW LEVEL BY

THE INPUT STAGE

- 1.6mA

+ 16mA

Capability should exceed demand.

Note the SIGN CONVENTION. Current into the gate is considered

positive. Hence we needed to use the modulus operator in the

compatibility statements above.

1/15/07

EE201L Class Notes - Chapter #2 Page 7 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

Direction of currents IOL and IIL:

The direction of currents IOL and IIL may be confusing because it is counter-intuitive.

Our intuition tells us that the current shall flow in the direction of the signal propagation.

But, remember that the CURRENT is NOT the SIGNAL; VOLTAGE is the SIGNAL.

To understand the direction of current flow, let us take an analogy of a

pneumatic system with a signal driver and a signal receiver.

The signal here is the air pressure. The signal driver either turns on the blower to

convey a high pressure signal or the vacuum pump to convey a low pressure signal.

SIGNAL RECEIVER

SIGNAL DRIVER

Signal: HIGH PRESSURE

AIR FLOW

IOH

IIH

Blower

Signal: LOW PRESSURE

AIR FLOW

IOL

IIL

Vacuum pump

Similar to the fact that the air flows away from the signal receiver towards the signal driver

during the low pressure signal transmission, the current, during low voltage signal

transmission between logic gates, flows from the receiving gate to the driving gate.

NOISE MARGINS:

6.2.6

5V (ideal high)

High-State Noise Margin

VIH

VOH

VOHtypical = 3.6V

Noise Margin = VOHmin - VIHmin

= 2.4V - 2.0V = 0.4V

Low-State Noise Margin

VIL

VOL

Noise Margin = V

=

1/15/07

V -

V =

-

V

High-State

DC Noise Margin =

VOHmin - VIHmin =

2.4V - 2.0V = 0.4V

Low-State

DC Noise Margin =

V

-V =

V - V= V

VOLtypical = 0.2V

V

EE201L Class Notes - Chapter #2 Page 8 / 40

VOHmin = 2.4V

VIHmin = 2.0V

Signal level

ambiguous

VILmax = 0.8V

VOLmax = 0.4V

0V (ideal low)

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

6.2.7

Propagation delays

After an input change, for the output to change,

the gate takes some time. This is called

propagation delay. For logic gates, there are

TWO delay parameters (not just ONE!).

tpHL =

A

A

B

Time taken by the OUTPUT to go

from HIGH to LOW after a corresponding event

at the input (whatever it is).

tpLH =

B

tpLH

tpHL

Time taken by the OUTPUT to go

from LOW to HIGH after a corresponding event

at the input (whatever it is).

Note: The suffixes, HL and LH in tpHL and tpLH refer to OUTPUT TRANSITIONS.

Fanout:

Driving Gate

The driving gate shall be capable of conveying both

HIGH state and LOW state signals by meeting the

current demands of the driven gates.

6.2.9

FANOUT = minimum of

the ratios

= minimum of

{

IOHmax

IIHmax

{

-400 uA

+40uA

};{

IOLmax

IILmax

}

};{

+16mA

-1.6mA

} = 10

FAN-IN: Similar to FANOUT, there is a term

called FAN-IN. It specifies the number of inputs

coming into the gate. If a logic family is said to have a

fan-in of 4 if in general the maximum number of

inputs on gates in that family is 4. While in principle,

you can think of an 8-input NAND gate, in practice, it

is built using two 4-input NAND gates, a 2-input NOR

gate, and an inverter.

1/15/07

for STANDARD TTL

Fanout is a number indicating how many gates

(how many gate inputs) can be driven by one gate

(one gate output).

Driven gates

6.2.8

EE201L Class Notes - Chapter #2 Page 9 / 40

Fig. 3-17 from Wakerly

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

7

TTL Subfamilies:

Two major series of TTL chips based on operating conditions:

74 Series: Industrial grade ICs for operation at 00 to 700C

54 Series: Premium grade ICs for operation at -550 to +1250C

for mainly military and space applications.

Within each of the above series there are several subfamilies which mainly

differ in their DELAY (SPEED) and the amount of POWER they consume.

Speed can easily be improved if you are allowed to consume more power.

However, we want less delay and less power.

Hence the POWER-DELAY PRODUCT is used as a

figure of merit comparing designs.

Inverters from obsolete families:

7404

74L04

STANDARD TTL

L = Low Power (consumes less power compared to Standard TTL)

Also slower than 74 series.)

74H04

H = High Speed (Faster but consumes more power)

Inverters from TTL families existing in design in 1980’s (Schottky families):

74S04

S = Schottky These are much faster than the Standard TTL

without too much increase in power consumption

74LS04

LS = Low Power Schottky

74AS04

74ALS04

74F04

AS = Advanced Schottky (Faster than Schottky)

ALS = Advanced Low Power Schottky (Faster than 74LS)

F = Fast (between 74AS and 74ALS)

1/15/07

EE201L Class Notes - Chapter #2 Page 10 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

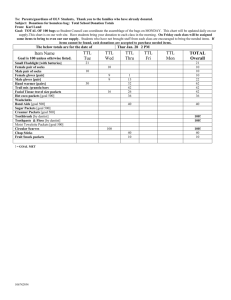

The following table lists the characteristics of the above 5 subfamilies (from Wakerly).

8

Compatibility among various families/subfamilies of chips

Signal Voltage Compatibility requirement:

VOHmin of the driver gate > VIHmin of the driven gate

VOLmax of the driver gate < VILmax of the driven gate

Normally there is no problem with this among the subfamilies of a family. However usually

signal voltage compatibility does not exist across different families.

For example the worst case TTL HIGH output (VOHmin of 2.4V) is not suitable as HIGH

input to a CMOS gate (VIHmin of 3.5V). In such cases, a pull-up resistor or a special level

shifting circuits are used to convert signals from one family to signal suitable as inputs

to another family.

Voltage compatibility may exist among subfamilies, but sometimes noise margins may differ.

(Example: VOHmin of any subfamily is higher than VIHmin of any subfamily but the difference between them

may change depending on the two subfamilies involved. Case 1: 2.7 - 2.0 = 0.7V; Case 2: 2.4 - 2.0 = 0.4V.

Note: VOHmin of standard TTL (plain 74 series) is only 2.4V.)

1/15/07

EE201L Class Notes - Chapter #2 Page 11 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

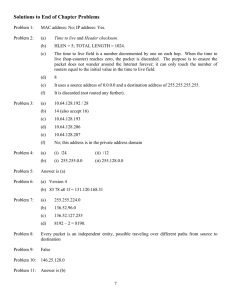

Current specs vary a lot even among subfamilies. Hence the FANOUT number

applies only within a subfamily (and not across subfamilies).

Hence, if you are using gates from a variety of subfamilies in one circuit,

it is necessary that we perform a current capacity check as shown below.

Current Capacity Check: The driver gate shall have enough current output

9

| IOHmax | >=

Σ | IIHmax |

| IOLmax | >=

Σ | IILmax |

Driving Gate

Driven gates

capability to meet sum of the demands of all the receiving gates.

Some IC packages:

14

1

7

8

14-pin DIP (Dual PLCC

Plastic Leaded

inline) package

PGA

BGA

Pin Grid Array

Ball Grid Array

Chip Carrier

VCC

GND

1/15/07

EE201L Class Notes - Chapter #2 Page 12 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

10 Typical manufacturer’s data sheet for the 74LS00 (Try "google" to find the complete data sheet on the web).

1/15/07

EE201L Class Notes - Chapter #2 Page 13 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

11 CMOS logic families (sec. 3.8 in Wakerly 4th ed.):

4000-series CMOS: Slow and obsolete

74HC

HC = High-speed CMOS

74HCT

HCT = High-speed CMOS, TTL Compatible

Fig. 3-60 Input and output levels for CMOS devices using 5V supply: (a) HC; (b) HCT

Fig. 3-61 Transfer Characteristics of HC

and HCT inverters.

An input of 2.1V is ambiguous to (or may be treated as low by) an HC device. where as, it is

clearly high for TTL and HCT devices.

74AHC

74AHCT

AHC = Advanced High-speed CMOS (advanced = faster than the HC)

AHCT = Advanced High-speed CMOS, TTL Compatible

Note 1uA

IIH/IIL

VILmax

VIHmin

Table 3.6 Input specifications for CMOS families with VCC between 4.5 and 5.5V

Note: The question of TTL compatibility araises only with the VILmax and VIHmin specifications.

TTL Load =

more

current

Table 3.7 Output specifications for CMOS families with VCC between 4.5 and 5.5V

(Output specs are same for HC/HCT; they are same for AHC/AHCT also.

1/15/07

EE201L Class Notes - Chapter #2 Page 14 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

AC/ACT (Advanced CMOS) have much higher current drive capability (IOH/IIL).

They are particularly useful to drive heavy DC loads.

The VOHmin and VOLmax for most CMOS families (HC, HCT, AHC, AHCT, AC, ACT)

are specified for a CMOS load on its output (less load current) as well as TTL load.

FCT (Fast CMOS TTL compatible) is TTL compatible and is similar to ACT but the raise

and fall times are deliberately slowed down to reduce "analog" transmission line reflection

problems. FCT-T (Fast CMOS TTL compatible with TTL VOH) has reduced VOH . While

the VOH of FCT (or AC or ACT) is superior to TTL, the VOH of FCT-T is made similar to

TTL. The idea is to limit the swing (VOL to VOH or VOH to VOL) so that both power

consumption and switching noise problems are reduced.

Consider the analogy of a water-hammer to understand switching noise.

Fig. 3-62 Comparison of logic levels

Note: All voltage parameters for

5V TTL and 3.3V LVTTL are the same!

Note that the CMOS logic has voltage parameters distributed symmetrically over 0 to Vcc.

12 Digilent board D2XL with Xilinx FPGA XC2S30 TQ144 (Students are not responsible for this

item)

The Xilinx Spartan 2 FPGA XC2S30 has an internal core running

at 2.5V. Technology used might be some proprietary MOS technology (mostly CMOS/NMOS). The FPGA has two power supply

connections: VCCINT ( = 2.5V) to power the core and VCCO (=

1.5V or 2.5V or 3.3V depending on the type of I/O the user wishes

to connect to the FPGA).

1/15/07

EE201L Class Notes - Chapter #2 Page 15 / 40

2.5V

VCCINT 3.3V

VCCO

Xilinx

FPGA

XC2S30

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

Digilent have connected 3.3V to the VCCO so that both LVTTL and regular 5V

TTL I/O can be connected.

The digilent board D2XL and the associated DIO1 board use 74HC series gates

(74HC244, 74HC14). However, you can attach regular 5V TTL such as 74LS04 as

Input/output. Some details from the Xilinx data sheet are given below.

1/15/07

EE201L Class Notes - Chapter #2 Page 16 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

13 Exercise:

13.1 Manufacturer Smith offers TTL devices with VOHmin = 2.7V

Manufacturer Bates offers TTL devices with VOHmin = 2.4V

Whose devices are better?

Smith / Bates

13.2 Manufacturer ABC offers TTL devices with VILmax = 0.7V

Manufacturer XYZ offers TTL devices with VILmax = 0.9V

Whose devices are better?

ABC / XYZ

Note: Best low is 0.0V.

13.3 Consider the digital comparator on the right.

Input X is driven by 4.6V.

Input Y is driven by 3.8V.

Which output will be TRUE? X > Y / X = Y / X < Y

4.6V

X

3.8V Y

X>Y

X=Y

X<Y

13.4 Is it better to have wide noise margin or narrow noise margin? Wide / Narrow

High State Noise Margin = V

V

Low State Noise Margin = V

V

13.5 Given that three inverters connected in series as shown below, label and find the values for

each of the 6 delays in the waveform.

A

tpHL = 1.5ns

tpLH = 2.2ns

B

tpHL = 1.6ns

tpLH = 2.3ns

C

tpHL = 1.7ns

tpLH = 2.4ns

D

A

B

C

D

13.6 Which of the following are NOT usually found in a data sheet? Cross them off.

VIHmin / VIHmax; VILmin / VILmax; VOHmin / VOHmax; VOLmin / VOLmax;

IIHmin / IIHmax;

IILmin / IILmax;

IOHmin / IOHmax;

IOLmin / IOLmax;

13.7 You know that VOLmax = 0.8V. Give a typical value of the same. VOLtyp = _____V.

13.8 Do you use AC (Alternating Current) or DC (Direct Current) to power your ICs? AC / DC

1/15/07

EE201L Class Notes - Chapter #2 Page 17 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

13.9 Buffers are used to make weak signals stronger.

Buffers are also used at the entry to a subsystem so that the loads in the

subsystem are handled by the buffer.

Example: Address buffer at the entry to an add-on PCI card.

Address line A10

A10

BA10

BB1_A10

PCI Card #1

internal loads

PCB trace

(Lengthy and Highly

Capacitive)

Buffer

BA10

BA10

Processor

Subsystem

BB8_A10

PCI Card #8

internal loads

uP

A buffer can be compared to a Power Steering in a car.

From the "HowStuffWorks" web page

If you compare a buffer in TTL gates or a power booster in a power-assisted steering with an

amplifier, what exactly is amplified?

In a buffer in TTL gates, is VOLTAGE amplified? Example: 0.7V becomes 0.7 x 4 = 2.8V?

In a power booster in a power-assisted steering, is rotational displacement amplified?

Example: Compared to a manual steering, a power-assisted steering causes the wheels to

rotate more?!

1/15/07

EE201L Class Notes - Chapter #2 Page 18 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

13.10 A manufacturer has designed a NEW series of digital gates 74USCxxx. Note: these need not

be compatible with any existing series of gates.

He tested a number of inverters (74USC04) and plotted their INPUT/OUTPUT characteristic.

Given below is the "SPREAD" of the plots. Help him write the four voltage specs.

State min or max for each.

Provide a 0.1V process tolerance margin over and above the band of characteristics shown.

VIH

5

VIL

= _____________ V

VOH

= _____________ V

Output (VO)

= _____________ V

4

3

2

1

VOL

= _____________ V

1

2

3

4

Input (VI)

5

13.11 In the design below, we have cascaded two inverters (with slightly different specs to make a

non-inverting buffer. Find the four voltage specs for the resulting non-inverting buffer.

Use "max" or "min" for each of the specs.

VIH

VIL

= 2.0V

= 0.8V

VOH

VOL

VIH

VIL

= 2.7V

= 0.5V

A

= 1.9V

= 0.9V

B

= 2.9V

= 0.3V

C

74LS04

VIH

VIL

VOH

VOL

74_new_04

=

=

V

V

VOH

VOL

A

=

=

V

V

C

resulting non-inverting buffer

Is the above 74_new_04 superior or inferior (or superior in some specs and inferior in some

other specs) than the 74LS04? ____________________________________________________

1/15/07

EE201L Class Notes - Chapter #2 Page 19 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

14 Transfer Characteristics of TTL gates

14.1 Transfer Characteristic =

a plot of output voltage signal vs. input voltage signal

Which of the following is the closest representation of the Transfer

Characteristic of a TTL inverter?

V

V

O

I

1

2

1

1

2

3

4

Input (VI)

5

4

3

2

1

1

2

3

4

Input (VI)

5

1

2

3

4

Input (VI)

The actual kinks in the shape are due to the

nonlinear behavior of a bipolar transistor.

We are NOT interested in these details, but

given a choice, would you like to reshape

the characteristic as "A" or "B"?

Output (VO)

Output (VO)

5

A

4

3

2

1

3

2

4

3

2

1

5

1

2

3

4

Input (VI)

5

1

2

3

4

Input (VI)

5

5

4

3

2

1

1

2

3

4

Input (VI)

5

B

4

3

2

1

1

1/15/07

4

1

14.2 The TTL inverter 74LS04 has a transfer

characteristic which looks like the one

shown on the side.

5

5

Output (VO)

2

3

5

Output (VO)

3

5

4

Output (VO)

4

Output (VO)

5

Output (VO)

Output (VO)

5

2

3

4

Input (VI)

5

1

2

3

4

Input (VI)

EE201L Class Notes - Chapter #2 Page 20 / 40

5

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

Consider aspects such as larger VILmax and lower VIHmin which possibly lead

to wider noise margins.

Given

as input, which one of the will produce n

and which would produce n

?

Which is preferable and why?

Also consider the characteristic being touchy (very sensitive) to noise.

14.3 Transmission of a digital signal over a long (> 1 foot) of a ribbon cable or

a PCB trace:

Behavior #1

Ideal

Behavior #2

Due to resistance

and capacitance

of the ribbon cable,

signals get rounded.

Behavior #3

Voltage VO

Voltage VO

Voltage VI

Noise can

further creep in.

VT Single Threshold

time

time

time

1/15/07

EE201L Class Notes - Chapter #2 Page 21 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

14.4 So finally do you want to reshape the characteristic to look like "A" or "B" ?

14.5 We want the advantage of "B" shown in "Behavior #2" namely turning rounded

signals into sharp signals, but at the same time, we do not want the disadvantage

of "Behavior #3" namely noise amplification.

That is where a schmitt trigger input gate with two thresholds has an advantage.

The difference between the two thresholds,

VT+ - VT- = 1.7V - 0.9V = 0.8V is called the

hysteresis.

Output (VO)

5

Direction of the

arrows is important!

14.6 Unlike an ordinary inverter such as 74LS04

which has a single threshold (VT = ~ 1.3V),

a schmitt trigger inverter 74LS14 has two

thresholds:

a positive going threshold VT+ = ~1.7V

a negative going threshold VT- = ~0.9V

4

3

2

1

1

2

3

4

Input (VI)

VT+

5

VTIf the input was low and is now rising up

(but in a noisy environment), the schmitt-trigger input device (such as a 74LS14

inverter or a 4-input NAND 74LS13) will not treat the input as having gone

HIGH until there is a substantial evidence at the input namely the crossing of the

VT+ in the positive direction. Once the input crosses VT+ in the positive

direction, the output switches and then onwards the VT+ has no significance.

Only when there is a substantial evidence at the input to indicate that the input

has gone really low by crossing VT-, in the negative direction, the output

switches again. This hysteresis helps to filter noise as can be seen in the diagrams

below.

Dictionary (http://dictionary.reference.com/browse/hysteresis) definition of the word hysteresis:

1. the

lag in response exhibited by a body in reacting to changes in the forces, esp. magnetic forces, affecting it.

2. the phenomenon exhibited by a system, often a ferromagnetic or imperfectly elastic material, in which

the reaction of the system to changes is dependent upon its past reactions to change.

1/15/07

EE201L Class Notes - Chapter #2 Page 22 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

VT+ = ~1.7V

VT = ~1.3V

VT- = ~0.9V

TTL

74LS00

74LS13

Figures 3-25, 3-47 and 3-48

from Wakerly (4th Edition)

VT+ = 2.9V

VT = 2.5V

VT- = 2.1V

1/15/07

EE201L Class Notes - Chapter #2 Page 23 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

14.7 Schmitt-trigger inverter response to triangular wave input (your lab experiment)

VT+

VT-

VI

VO

14.8 Schmitt-trigger applications:

PCB trace

(Lengthy and Highly

Capacitive)

Address line A10

BA10

PCI Card #1

BA10

uP

Note

Processor

Subsystem

From www.ti.com

1/15/07

BB1_A10

BA10

Noise can easily

get into the

signal here

BB8_A10

PCI Card #8

internal loads

A10

Note

internal loads

14.8.1When TTL signals have to travel long distances (more than 1 foot, for example

from one PCB to another PCB through ribbon cable) the receiving device input

shall be schmitt-trigger input type.

74LS241 buffer application

EE201L Class Notes - Chapter #2 Page 24 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

14.8.2 In RESET circuits

VCC

Node IN

RESET

VC

VT+

VC

t

Any noise at the Node IN

can potentially cause the

RESET signal to go up and

down if we use an ordinary

buffer to produce RESET.

14.8.3To square-up

slowly varying

signals

14.9 Recognizing a schmitt-trigger input device:

In the symbols for devices with schmitt-trigger input, they show the hysteresis symbol:

Note

or

Note: 74S04

S = Schottky (not Schmitt-trigger)

There is no special letter in the

device number to indicate

that it has schmitt-trigger input.

From Texas Instruments (www.ti.com)

Octal tri-state buffer 74LS241

1/15/07

EE201L Class Notes - Chapter #2 Page 25 / 40

C Copyright 2007 Gandhi Puvvada

EE201L_ClassNotes_Ch2.fm

15 Exercise:

15.1 Which of the following is the closest representation of the Transfer

Characteristic of a TTL schmitt-trigger inverter 74LS14?

4

3

2

Note

4

3

2

Note

1

2

3

4

Input (VI)

5

4

3

2

2

3

4

Input (VI)

5

4

3

2

Note

1

1

1

D

5

Note

1

1

C

5

Output (VO)

Output (VO)

Output (VO)

B

5

Output (VO)

A

5

VO

VI

1

2

3

4

Input (VI)

Arrows differ

1

5

2

3

4

Input (VI)

5

Arrows differ

15.2 In the design below, we have cascaded two schmitt-trigger inverters (with

identical specs to make a non-inverting schmitt-trigger buffer.

VI

VO

Which of the above four is the closest representation of the Transfer

Characteristic of the resulting non-inverting schmitt-trigger buffer?

15.3 To produce the desired non-inverting schmitt-trigger buffer, is it necessary to

use both schmitt-trigger type inverters in the cascade or is it enough to use one

schmitt-trigger type inverter and one ordinary inverter? ________ (both / one)

If one is adequate, which one of them shall be a schmitt-trigger type inverter?

__________________ (first / second / either).

15.4 If you use both schmitt-trigger type inverters in the cascade, and if they have

slightly different VT+ and VT-, the resulting non-inverting schmitt-trigger buffer

would have VT+ and VT-, which are _____________________________________

( same as the first inverter /

same as the second inverter /

average of the two sets of specs).

15.5 "schmitt-trigger" is an attribute to describe the behavior at the

___________________ (input/output/input and output) of the gate.

1/15/07

EE201L Class Notes - Chapter #2 Page 26 / 40

C Copyright 2007 Gandhi Puvvada