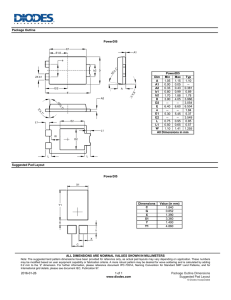

Exposed Pad : A Brief Introduction

advertisement

Thermal Design Considerations of Exposed Pad IC As the miniaturization of electronic devices, the small area and close proximity of ICs in these modules demands small packages with excellent thermal properties. Thermal performance is a system level concern, impacted by IC packaging as well as PCB design. This application note addresses the thermal considerations for the exposed pad package. The introduction of the exposed pad helps to reduce package size and improve the thermal characteristics of the device. The exposed pad on ICs is intended to provide significant power dissipation, and the PCB designer should add vias from the exposed pad's land area to a copper polygon on the other side of the PCB. This provides lower thermal impedance from the IC to the ambient air. An example of increasing thermal performance by proper PCB layout of the exposed pad will also be provided. General Description: Most of the heat generated by an IC is conducted to the PCB and then radiates from the PCB to the ambient. Heat is transferred to the PCB from the leads and package. An exposed pad package improves the heat transfer efficiency by creating a low thermal resistive path to the PCB. This will increase the maximum power dissipation of packages. When an exposed pad is offered as an option, it is specifically to increase the power dissipation capabilities of the IC package. Bonding Wire Die Lead Frame Exposed Pad Soldering Top Layer Thermal Pad PCB Thermal Vias Ground Plane Power Plane Bottom Layer Thermal Pad Fig.1 Heat transfer General guidelines will be given by which to aid in designing a PCB that uses exposed pad packages. 1. The thermal pad should be designed with 0mm to 0.3mm larger per side than the IC’s exposed pad. 2. In order to increase the power dissipation ability, exposed pad must enlarge the copper foil area as large as possible on PCB, and add vias from the exposed pad’s land area to a copper polygon on the other side of the PCB. 3. A grid of 1mm to 1.2mm pitch thermal vias, which connect to bury copper planes, should be placed under the thermal pad. The vias should be about 0.3mm to 0.33mm in diameter, with the barrel plated to about 1 ounce or 2 ounces copper. Thermal Pad 1~1.2mm 0.3~0.33mm Thermal Via Fig.2 Thermal Via Types 4. Avoids heating components too close, which will degradation the thermal performance of exposed pad IC. Actual utilization: D1 + C5 C1 1uF 100uF U1 N2 L1 100uH Vout N3 1 2 3 4 C7 0.1uF + C2 470uF D2 SC SE CF GND AIC1573 BST CS VIN FB 8 7 6 5 R1 0.1 Vin C6 0.1uF N4 C3 100pF GND GND R2 3k C4 33nF Fig.3 AIC1573 PWM buck converter N1 R3 1k Fig.4 PCB Top Layer (The blue area is thermal pad and ground trace) Operation temperature: EP_6 (115°C) > EP_3&EP_4&EP_5(83°C) > EP_1&EP_2(76° C) Efficiency: EP_1&EP_2(79%) > EP_3&EP_4&EP_5(77%) > EP_6(75%) Vout ripple noise (full bandwidth): EP_6(30mV) > EP_2&EP_3&EP_4&EP_5(24mV) > EP_1(20mV) Summary The purpose of this application note is to give a brief introduction to general layout considerations that can be applied to obtain the benefits of the exposed pad package. Proper soldering of the exposed pad to a suitable thermally conductive surface, such as a ground plane, is critical in obtaining the improved performance of the exposed pad package and proper operation of the IC.