2Q 2016 Analog Applications Journal Issue

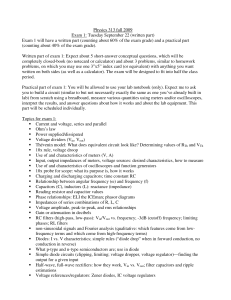

advertisement