µA µA

advertisement

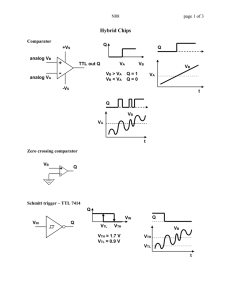

94 Chapter 3 Digital Circuits DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY Ta b l e 3 - 3 Manufacturer’s data sheet for a typical CMOS device, the 54/74HC00 quad NAND gate. DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE The following conditions apply unless otherwise specified: Commercial: TA = −40°C to +85°C, VCC = 5.0V±5%; Military: TA = −55°C to +125°C, VCC = 5.0V±10% Sym. Test Conditions (1) Parameter Min. Typ.(2) Max. Unit VIH Input HIGH level Guaranteed logic HIGH level 3.15 — — V VIL Input LOW level Guaranteed logic LOW level — — 1.35 V IIH Input HIGH current VCC = Max., VI = VCC — — 1 µA IIL Input LOW current VCC = Max., VI = 0 V — — −1 µA VIK Clamp diode voltage VCC = Min., IN = −18 mA — −0.7 −1.2 V IIOS Short-circuit current VCC = Max.,(3) VO = GND — — −35 mA VOH Output HIGH voltage VCC = Min., VIN = VIL IOH = −20 µA 4.4 4.499 — V IOH = −4 mA 3.84 4.3 — V VOL Output LOW voltage VCC = Min. VIN = VIH IOL = 20 µA — .001 0.1 V 0.17 0.33 ICC Quiescent power supply current VCC = Max. VIN = GND or VCC, IO = 0 2 10 µA Min. Typ. Max. Unit IOL = 4 mA — SWITCHING CHARACTERISTICS OVER OPERATING RANGE, CL = 50 pF Sym. Parameter (4) Test Conditions tPD Propagation delay A or B to Y — 9 19 ns CI Input capacitance VIN = 0 V — 3 10 pF Cpd Power dissipation capacitance per gate — 22 — pF No load NOTES: 1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics. 2. Typical values are at VCC = 5.0 V, +25°C ambient. 3. Not more than one output should be shorted at a time. Duration of short-circuit test should not exceed one second. 4. This parameter is guaranteed but not tested. WHAT’S IN A NUMBER? Two different prefixes, “74” and “54,” are used in the part numbers of CMOS and TTL devices. These prefixes simply distinguish between commercial and military versions. A 74HC00 is the commercial part and the 54HC00 is the military version. C Section 3.5 CMOS Steady-State Electrical Behavior DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY DO NOT COPY D D D LOADING TEST CIRCUIT FOR ALL OUTPUTS VCC VCC Parameter t en Pulse Generator VIN VOUT Device Under Test RL S1 t dis S2 CL RT VCC 50% 0.0 V tH VCC 50% 0.0 V Clock Input tREM VCC 50% 0.0 V Asyncronous Control Input (PR, CLR, etc.) VCC 50% 0.0 V Syncronous Control Input (CLKEN, etc.) tH PROPAGATION DELAY tpHZ CL S1 S2 1 KW 50 pF or 150 pF Open Closed 1 KW tpLZ tPLH tPHL Output Transition tPLH — e c d 3 T o p C Open Open Closed Closed Open Open Open PULSE WIDTH LOW-HIGH-LOW Pulse tW HIGH-LOW-HIGH Pulse tPHL VCC 50% 0.0 V Enable Disable Control Input tPZL VOH 50% VOL Output Normally LOW VCC 50% 0.0 V Output Normally HIGH tPLZ 50% tPZH Figure 3-24 Test circuits and waveforms for HC-series logic. r 50 pF or 150 pF Closed VOH 50% VOL VOH 50% VOL THREE-STATE ENABLE AND DISABLE TIMES Same-Phase Input Transition Opposite-Phase Input Transition tpZL RL DEFINITIONS: CL = Load capacitance, includes jig and probe capacitance. RT = Termination resistance, should equal ZOUT of the Pulse Generator. Data Input tSU tpZH t pd SETUP, HOLD, AND RELEASE TIMES tSU 95 tPHZ 50% VCC 50% 0.0 V VCC 10% VOL VOH 90% 0.0 V