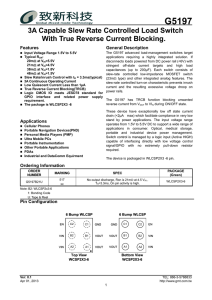

Programmable Output Voltage Ultra-Low Power

advertisement

TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 支持高达 50mA/200mA 输出电流的可编程输出电压超低功耗降压转换器 查询样品: TPS62736, TPS62737 特性 应用范围 1 • • • • 低输出电流方面行业最高效率:I输出= 15µA 时大于 90% 超低功耗降压转换器 – TPS62736 针对 50mA 输出电流进行了优化 – TPS62737 针对 200mA 输出电流进行了优化 – 1.3V-5V 电阻器可编程输出电压范围 – 2V-5.5V 输入工作范围 – 对于 TPS62736/TPS62737, ,有源运行期 间,380nA/375nA 的静态电流 – 出厂模式运行期间,10nA 静态电流 – 2% 电压调节精度 100% 占空比(直通模式) EN1 和 EN2 控制 – 两个断电状态: – 1) 出厂模式(完全断电状态) – 2) 包括 VIN_OK 指示在内的待机模式 输入电源正常指示 (VIN_OK) – 推挽驱动器 – 电阻器可编程阀值电平 超低功耗应用 2 节和 3 节碱性电池供电类应用 能量采集 太阳能充电器 热电发电机 (TEG) 能量采集 无线传感器网络 (WSN) 低功耗无线监测 环境监测 桥梁和结构健康监测 (SHM) 智能楼宇控制 便携式和可佩戴式健康器件 娱乐系统遥控 • • • • • • • • • • • • 100 95 TPS62736 90 Efficiency (%) • 85 80 75 70 65 Test Conditions: VO = 2.5V, VIN = 3V, TA = 25oC, L = 10mH (Toko DFE252012C) 60 55 0.001 > 90% at IOUT = 15 PA VIN 0.01 10 100 G000 L 10 PH SW IN VOUT OUT 4.7F 0.1 1 Iout (mA) TPS62736 22 PF 1 Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. UNLESS OTHERWISE NOTED this document contains PRODUCTION DATA information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters. 版权 © 2012–2013, Texas Instruments Incorporated English Data Sheet: SLVSBO4 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates. 说明 TPS6273X 系列提供了一个高度集成的超低功耗降压转换器解决方案,此解决方案非常适合于满足诸如能量采集等 超低功耗应用的特殊需要。 为了保持与一个线性降压转换器相对的电源管理级的总体效率,TPS6273X 提供具有 一个外部可编程经稳压电源的系统。 为了给低压电子器件供电,这个稳压器用于将来自诸如电池或者超大电容器等 储能元件的电压降低。 为了在整个低输出电流 (<10µA) 到高电流 (200mA) 的转换过程中提供高效率,已经对经稳 压的输出进行了优化。 TPS6273X 集成了一个针对低功耗应用的已优化的滞后控制器。 为了减少平均静态电流,内部电路采用一个基于 时间的采样系统。 为了帮助用户进一步严格管理他们的能耗预算,当输入电源上的电压已经下降到低于一个预先设定的关键电平以下 时,TPS6273X 切换输入正常指示器,向一个已连接的微控制器发出一个信号。 这个信号用于触发负载电流衰 减,以防止系统进入一个欠压条件。 还有独立使能信号来使系统能够控制转换器是否调节输出,还是只监视输入电 压,或者在超低静态睡眠状态中关断。 输入正常阀值和输出稳压器电平是由外部电阻器独立设定的。 TPS6273X 的全部功能被封装在一个小封装尺寸 14 接线 3.5mm x 3.5mm 四方扁平无引线 (QFN) 封装。 ORDERING INFORMATION TA PART NO. OUTPUT VOLTAGE MAX OUTPUT CURRENT INPUT UVLO –40°C to 85°C TPS62736 (1) Resistor Programmable 50 mA 2V –20°C to 85°C (1) TPS62737 (1) Resistor Programmable 200 mA 2V ORDERING NUMBER (TAPE AND REEL) TPS62736RGYR TPS62736RGYT TPS62737RGYR TPS62737RGYT PACKAGE MARKING QUANTITY 3000 TPS62736 250 3000 TPS62737 250 The RGY package is available in tape on reel. Add R suffix to order quantities of 3000 parts per reel, T suffix for 250 parts per reel. ABSOLUTE MAXIMUM RATINGS (1) over operating free-air temperature range (unless otherwise noted) VALUE (2) UNIT MIN MAX –0.3 5.5 V 100 mA Pin voltage Input voltage range on IN, EN1, EN2, VRDIV, VIN_OK_SET, VOUT_SET, VIN_OK, OUT, SW,NC TPS62736 Peak currents IN, OUT TPS62737 Peak currents IN, OUT 370 mA TJ Temperature range Operating junction temperature range –40 125 °C Storage temperature range –65 150 °C TSTG Human Body Model - (HBM) ESD (3) (1) (2) (3) 2 1 kV Machine Model (MM) 150 V Charge Device Model - (CDM) 500 V Stresses beyond those listed under “absolute maximum ratings” may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under “recommended operating conditions” is not implied. Exposure to absolute–maximum–rated conditions for extended periods may affect device reliability. All voltage values are with respect to VSS/ground terminal ESD testing is performed according to the respective JESD22 JEDEC standard. Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 THERMAL INFORMATION RGY THERMAL METRIC (1) θJA Junction-to-ambient thermal resistance 33.7 θJCtop Junction-to-case (top) thermal resistance 37.6 θJB Junction-to-board thermal resistance 10.1 ψJT Junction-to-top characterization parameter 0.4 ψJB Junction-to-board characterization parameter 10.3 θJCbot Junction-to-case (bottom) thermal resistance 2.9 (1) UNITS 14-Pins °C/W For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953. RECOMMENDED OPERATING CONDITIONS MIN IN IN voltage range TPS62736 Input Capacitance 4.7 TPS62737 Input Capacitance 22 COUT Output Capacitance 10 R1 + R2 + R3 Total Resistance for setting reference voltage CIN LBUCK TA TJ NOM MAX 2 TPS62736 Inductance 4.7 TPS62737 Inductance 10 UNIT 5.5 V μF 22 μF 13 MΩ 10 μH TPS62736 Operating free air ambient temperature –40 85 TPS62737 Operating free air ambient temperature –20 85 Operating junction temperature –40 105 °C °C ELECTRICAL CHARACTERISTICS Over recommended ambient temperature range, typical values are at TA = 25°C. Unless otherwise noted, specifications apply for conditions of VIN = 4.2 V, VOUT = 1.8 V External components, CIN = 4.7 µF for TPS62736 and 22 µF for TPS62737 , LBUCK = 10 µH, COUT = 22 µF PARAMETER TEST CONDITIONS MIN TYP MAX TPS62736 Buck enabled state (EN1 = 0, EN2 = 1) 380 550 TPS62736 Buck disabled VIN_OK active state (EN1 = 0, EN2 = 0) 340 520 10 65 375 600 TPS62737 Buck disabled VIN_OK active state (EN1 = 0, EN2 = 0) 345 560 TPS62737 Ship mode state (EN1 = 1, EN2 = x) 11 45 UNIT QUIESCENT CURRENTS IQ TPS62736 Ship mode state (EN1 = 1, EN2 = x) TPS62737 Buck enabled state (EN1 = 0, EN2 = 1) Copyright © 2012–2013, Texas Instruments Incorporated VIN = 2 V, No load on VOUT nA nA 3 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn ELECTRICAL CHARACTERISTICS (continued) Over recommended ambient temperature range, typical values are at TA = 25°C. Unless otherwise noted, specifications apply for conditions of VIN = 4.2 V, VOUT = 1.8 V External components, CIN = 4.7 µF for TPS62736 and 22 µF for TPS62737 , LBUCK = 10 µH, COUT = 22 µF PARAMETER TEST CONDITIONS MIN TYP MAX UNIT V OUTPUT VBIAS VOUT VDO tSTART-STBY tSTART-SHIP Output regulation reference 1.205 1.21 1.217 TPS62736 Output regulation (Spec does not include the resistor accuracy error) IOUT = 10 mA; 1.3 V < VOUT < 3.3 V –2% 0% 2% TPS62737 Output regulation (Spec does not include the resistor accuracy error) IOUT = 100 mA; 1.3 V < VOUT < 3.3 V; –2% 0% 2% TPS62736 Output line regulation IOUT = 100 µA; VIN = 2.4 V to 5.5 V 0.01 TPS62737 Output line regulation IOUT = 10 mA; VIN = 2.3 V to 5.5 V 0.31 TPS62736 Output load regulation IOUT = 100 µA to 50 mA, VIN = 2.2 V 0.01 %/mA TPS62737 Output load regulation IOUT = 100 µA to 200 mA, VIN = 2.2 V; -20 °C < TA < 85°C 0.01 %/mA TPS62736 Output ripple VIN = 4.2V, IOUT = 1 mA, COUT = 22 μF 20 mVpp TPS62737 Output ripple VIN = 4.2V, IOUT = 1 mA, COUT = 22 μF 40 mVpp Programmable voltage range for output voltage threshold IOUT = 10 mA TPS62736 Drop-out-voltage when VIN is less than VOUT(SET) VIN = 2.1 V, VOUT(SET) = 2.5 V, IOUT = 10 mA, 100% duty cycle 24 30 mV TPS62737 Drop-out-voltage when VIN is less than VOUT(SET) VIN = 2.1 V, VOUT(SET) = 2.5 V, IOUT = 100 mA, 100% duty cycle 180 220 mV Startup time with EN1 low and EN2 transition to high (Standby Mode) TPS62736, COUT = 22 µF 400 TPS62737, COUT = 22 µF 300 μs Startup time with EN2 high and EN1 transition from high to low (Ship Mode) COUT = 22 µF 100 ms TPS62736 High side switch ON resistance VIN = 3 V 2.4 3 Ω TPS62736 Low side switch ON resistance VIN = 3 V 1.1 1.5 Ω TPS62737 High side switch ON resistance VIN = 2.1 V 1.8 2.2 Ω TPS62737 Low side switch ON resistance VIN = 2.1 V 0.9 1.3 Ω TPS62736 Cycle-by-cycle current limit 2.4 V < VIN < 5.25 V; 1.3 V < VOUT < 3.3 V 68 86 100 mA TPS62737 Cycle-by-cycle current limit 2.4 V < VIN < 5.25 V; 1.3 V < VOUT < 3.3 V; -20 °C < TA < 85°C 295 340 370 mA %/V 1.3 VIN - 0.2 V μs POWER SWITCH RDS(on) ILIM fSW Max switching frequency 2 MHz INPUT VIN-UVLO Input under voltage protection VIN-OK Input power good programmable voltage range VIN-OK-ACC TPS62736 Accuracy of VIN-OK setting VIN falling VIN increasing TPS62737 Accuracy of VIN-OK setting 1.91 1.95 Fixed hysteresis on VIN_OK threshold, OK_HYST VIN increasing VIN_OK-OH VIN-OK output high threshold voltage Load = 10 µA VIN_OK-OL VIN-OK output low threshold voltage V 5.5 V -2 2 % -3 VIN-OK-HYS 2 2 3 40 mV VIN - 0.2 V 0.1 V EN1 and EN2 VIH Voltage for EN High setting. Relative to VIN VIL Voltage for EN Low setting. 4 VIN = 4.2V VIN - 0.2 V 0.2 V Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 PIN ASSIGNMENTS IN NC TPS62736 RGY PACKAGE (TOP VIEW) 1 14 NC 2 13 SW NC 3 12 VSS NC 4 11 OUT EN1 5 10 VIN_OK EN2 6 9 VOUT_SET 8 VRDIV VIN_OK_SET 7 PIN DESCRIPTION PIN NO. NAME I/O Type Description 1 IN Input Input supply to the buck regulator 2 NC Input Connect to VSS 3 NC Input Connect to VSS 4 NC Input Connect to VSS 5 EN1 Input 6 EN2 Input Digital input for chip enable, standby, and ship-mode. EN1 = 1 sets ship mode independent of EN2. EN1=0, EN2 = 0 disables the buck converter and sets standby mode. EN1=0, EN2=1 enables the buck converter. Do not leave either pin floating. 7 VRDIV 8 VIN_OK_SET Input Resistor divider input for VIN_OK threshold. Pull to VIN to disable. Do not leave pin floating. 9 VOUT_SET Input Resistor divider input for VOUT regulation level 10 VIN_OK Output Push-pull digital output for power good indicator for the input voltage. Pulled up to VIN pin. 11 OUT Output Step down (buck) regulator output 12 VSS Input Ground connection for the device 13 SW Input Inductor connection to switching node 14 NC Input Connect to VSS 15 Thermal Pad Input Connect to VSS Output Resistor divider biasing voltage Copyright © 2012–2013, Texas Instruments Incorporated 5 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn IN NC TPS62737 RGY PACKAGE (TOP VIEW) 1 14 SW 2 13 SW VSS 3 12 VSS NC 4 11 OUT EN1 5 10 VIN_OK EN2 6 9 VOUT_SET 8 VRDIV VIN_OK_SET 7 PIN DESCRIPTION PIN NO. 1 6 NAME I/O Type Description IN Input Input supply to the buck regulator 2, 13 SW Input Inductor connection to switching node 3, 12 VSS Input Ground connection for the device 4, 14 NC Input Connect to VSS 5 EN1 Input 6 EN2 Input Digital input for chip enable, standby, and ship-mode. EN1 = 1 sets ship mode independent of EN2. EN1=0, EN2 = 0 disables the buck converter and sets standby mode. EN1=0, EN2=1 enables the buck converter. Do not leave either pin floating. 7 VRDIV 8 VIN_OK_SET Input Resistor divider input for VIN_OK threshold. Pull to VIN to disable. Do not leave pin floating. 9 VOUT_SET Input Resistor divider input for VOUT regulation level 10 VIN_OK Output Push-pull digital output for power good indicator for the input voltage. Pulled up to VIN pin. 11 OUT Output Step down (buck) regulator output 15 Thermal Pad Output Input Resistor divider biasing voltage Connect to VSS Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 FUNCTIONAL BLOCK DIAGRAM IN VSS SW Buck Controller TPS6273x Functional Block Diagram VIN > UV? OUT EN2 VOUT_SET VIN_OK VIN_OK_SET + Input Threshold Control UV OK + Vref Nano-Power Management and Reference Generation Vref VIN_UV EN1 Copyright © 2012–2013, Texas Instruments Incorporated VRDIV 7 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn TYPICAL APPLICATION SCHEMATIC TPS62736 IN VIN CIN1 CIN2 4.7PF 0.1PF SW L 10 PH System Load OUT Buck Controller GPIO1 VIN_OK GPIO2 EN1 GPIO2 EN2 22PF COUT VSS Host VRDIV R3 R2 VOUT_SET VIN_OK_SET Nano-Power Management R1 Figure 1. Typical Application Circuit for a 3-resistor String TPS62737 IN VIN CIN1 CIN2 22PF 0.1PF SW L 10 PH System Load OUT 22PF Buck Controller GPIO1 VIN_OK GPIO2 EN1 GPIO2 EN2 COUT VSS Host VRDIV R3 R2 VOUT_SET VIN_OK_SET Nano-Power Management R1 Figure 2. Typical Application Circuit 8 Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 TPS62736 IN VIN CIN1 CIN2 4.7PF 0.1PF SW L 10 PH System Load OUT 22PF Buck Controller GPIO1 VIN_OK GPIO2 EN1 GPIO2 EN2 COUT VSS Host VRDIV R3 VOUT_SET R2 R4 VIN_OK_SET Nano-Power Management R1 Figure 3. Typical Application Circuit for a 4-resistor String TPS62736 IN VIN CIN1 CIN2 4.7PF 0.1PF SW L 10 PH System Load OUT 22PF Buck Controller GPIO1 VIN_OK GPIO2 EN1 GPIO2 EN2 COUT VSS Host VRDIV R3 VOUT_SET R4 VIN VIN_OK_SET Nano-Power Management Figure 4. Typical Application Circuit for Disabling VIN_OK Copyright © 2012–2013, Texas Instruments Incorporated 9 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn TYPICAL CHARACTERISTICS Table of Graphs for TPS62736 Unless otherwise noted, graphs were taken using Figure 1 with L = Toko 10 µH DFE252012C VO = 2.5 V Efficiency η VO = 1.8 V Efficiency VO = 1.3 V Efficiency VO = 2.5 V VOUT (DC) VO = 1.8 V VO = 1.3 V Figure 5 vs. Input Voltage Figure 6 vs. Output Current Figure 7 vs. Input Voltage Figure 8 vs. Output Current Figure 9 vs. Input Voltage Figure 10 vs. Output Current Figure 11 vs. Input Voltage Figure 12 vs. Temperature Figure 13 vs. Output Current Figure 14 vs. Input Voltage Figure 15 vs. Temperature Figure 16 vs. Output Current Figure 17 vs. Input Voltage Figure 18 vs. Temperature Figure 19 VO = 2.5 V IOUT MAX (DC) Input IQ VO = 1.8 V Figure 20 vs. Input Voltage Figure 22 EN1 = 1, EN2 = 0 (Ship Mode) Figure 23 EN1 = 0, EN2 = 0 (Standby Mode) Switching Frequency VO = 2.5 V Output Ripple VO = 2.5 V Power Management Response Transient Response Startup Behavior 10 Figure 21 VO = 1.3 V vs. Input Voltage EN1 = 0, EN2 = 1 (Active Mode) Steady State Operation FIGURE vs. Output Current VIN = 3 V, VO = 2.5 V Figure 24 Figure 25 vs. Output Current Figure 27 vs. Input Voltage Figure 28 vs.Output Current Figure 29 vs. Input Voltage Figure 30 RO = 50 Ω Figure 31 RO = 100 kΩ Figure 32 VIN = 3 V, VO = 1.8 V, L = 4.7 µH RO = 50 Ω Figure 33 VRDIV Behavior VO = 2.5 V Figure 34 Line Transient, VIN = 3.0V -> 5.0V, ROUT = 50 Ω Figure 35 Load Transient, VIN = 4.0V, ROUT = none -> 50 Ω Figure 36 IR Pulse Transient, VIN = 4.0V, 200mA transient every 1us Figure 37 EN1 1 to 0, EN2=1 - Ship mode startup Figure 38 EN1 = 0, EN2 0 to 1 - Standy mode startup Figure 39 VO = 2.5 V VIN = 4.0 V, VO = 1.8 V Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 100 100 IO =Series1 0.1 mA IO =Series2 1 mA IO =Series4 10 mA IO =Series5 45 mA 95 98 90 Efficiency (%) Efficiency (%) 85 80 75 70 65 60 55 50 0.001 Test Conditions: VO = 2.5 V, TA = 25C L = 10 µH (Toko DFE252012C) 0.01 0.1 1 VSeries2 IN = 4.2 V VSeries4 IN = 3.6 V VSeries5 IN = 3 V VSeries6 IN = 2.7 V 10 IOUT (mA) 2.0 4.0 4.5 IO = 0.1 mA Series1 96 75 70 65 60 Series1 VIN = 4.2 V Test Conditions: VO = 1.8 V, TA = 25C L = 10 µH (Toko DFE252012C) 0.01 0.1 1 IO = 1 mA Series2 IO = 10 mA Series4 IO = 45 mA Series5 94 92 90 88 VIN = 3.6 V Series2 VIN =3V Series4 86 VIN = 2.1 V Series5 10 84 100 2.0 2.5 3.0 3.5 4.0 4.5 Figure 7. Efficiency Vs Output Current, VOUT = 1.8 V 98 C004 IO =Series1 0.1 mA IO =Series2 1 mA IO =Series4 10 mA IO =Series5 45 mA Test Conditions: VO = 1.3 V, TA = 25C L = 10 µH (Toko DFE252012C) 96 Efficiency (%) 94 0.1 1 IOUT (mA) 90 88 84 82 80 100 C00 Figure 9. Efficiency Vs Output Current, VOUT = 1.3 V Copyright © 2012–2013, Texas Instruments Incorporated 92 86 VIN = 4.2 V Series1 VIN = 3.6 V Series2 VIN =3V Series4 VIN = 2.1 V Series5 10 5.5 Figure 8. Efficiency vs Input Voltage, VOUT = 1.8 V 100 0.01 5.0 VIN (V) C003 Test Conditions: VO = 1.3 V, TA = 25C L = 10 µH (Toko DFE252012C) 5.5 C002 Test Conditions: VO = 1.8 V, TA = 25C L = 10 µH (Toko DFE252012C) 98 80 5.0 Figure 6. Efficiency vs Input Voltage, VOUT = 2.5 V Efficiency (%) Efficiency (%) 3.5 100 IOUT (mA) Efficiency (%) 3.0 VIN (V) 85 100 95 90 85 80 75 70 65 60 55 50 45 40 35 30 0.001 2.5 C001 90 40 0.001 Test Conditions: VO = 2.5 V, TA = 25C L = 10 µH (Toko DFE252012C 88 95 45 92 100 100 50 94 90 Figure 5. Efficiency Vs Output Current, VOUT = 2.5 V 55 96 2.0 2.5 3.0 3.5 4.0 VIN (V) 4.5 5.0 5.5 C006 Figure 10. Efficiency vs Input Voltage, VOUT = 1.3 V 11 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn 2.520 2.6 2.5 2.515 2.510 VOUT (V) VOUT (V) 2.4 2.505 2.2 2.1 2.500 2.495 0.001 IO =Series1 0.1 mA Series2 VIN = 4.2 V Test Conditions: VIN = 3.6 V VO = 2.5 V, TA = 25C Series1 VIN =3V L = 10 µH (Toko DFE252012C) Series4 VIN = 2.7 V Series5 0.01 0.1 1 10 2.0 IO =Series4 10 mA IO =Series5 45 mA 1.8 100 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 VIN (V) C007 Figure 11. Output Voltage vs Output Current. VOUT = 2.5 V C008 Figure 12. Output Voltage vs Input Voltage, VOUT = 2.5 V 1.805 2.525 Test Conditions: VO = 2.5 V, VIN = 3 V L = 10 µH (Toko DFE252012C) 2.520 2.515 1.800 VOUT (V) 2.510 2.505 2.500 2.495 IO Series1 = 1 mA 2.490 IO Series2 = 10 mA ±40 ±20 0 20 40 60 Temperature (C) 1.795 1.790 1.785 IO Series4 = 50 mA 2.485 1.780 0.001 80 VINSeries1 = 4.2 V VINSeries2 = 3.6 V VINSeries4 =3V VINSeries5 = 2.7 V Test Conditions: VO = 1.8 V, TA = 25C L = 10 µH (Toko DFE252012C) 0.01 0.1 1.815 1.8 1.795 100 C010 1.805 Test Conditions: VO = 1.8 V, VIN = 3 V L = 10 µH (Toko DFE252012C) 1.8 VOUT (V) 1.805 10 Figure 14. Output Voltage vs Output Current, VOUT = 1.8 V IO Series1 = 0.1 mA IO Series2 = 1 mA IO Series4 = 10 mA IO Series5 = 45 mA 1.81 1 IOUT (mA) C009 Figure 13. Output Voltage vs Temperature, VOUT = 2.5 V VOUT (V) IO =Series2 1 mA Test Conditions: VO = 2.5 V, TA = 25C L = 10 µH (Toko DFE252012C) 1.9 IOUT (mA) VOUT (V) 2.3 1.795 1.79 1.79 Test Conditions: VO = 1.8 V, TA = 25C L = 10 µH (Toko DFE252012C) 1.785 1.78 1.78 2.0 2.5 3.0 3.5 4.0 VIN (V) 4.5 5.0 5.5 C011 Figure 15. Output Voltage vs Input Voltage, VOUT = 1.8 V 12 IO Series1 = 1 mA IO Series2 = 10 mA IO Series4 = 50 mA 1.785 ±40 ±20 0 20 40 Temperature (C) 60 80 C012 Figure 16. Output Voltage vs Temperature, VOUT = 1.8 V Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 1.303 1.305 1.301 1.3 VOUT (V) 1.297 1.295 1.293 1.291 1.289 0.001 VIN = 4.2 V Series1 Test Conditions: VIN =3V Series2 VO = 1.3 V, TA = 25C VIN = 3.6 V L = 10 uH (Toko DFE252012C) Series4 VIN = 2.1 V Series5 0.01 0.1 1 1.29 IO =Series1 0.1 mA IO =Series2 1 mA IO =Series4 10 mA IO =Series5 45 mA 1.285 1.28 10 100 IOUT (mA) 2.0 2.5 3.0 Test Condition: VO = 1.3 V, TA = 25C L = 10 µH (Toko DFE252012C) 3.5 4.0 4.5 5.0 VIN (V) C013 5.5 C014 Figure 17. Output Voltage vs Output Current, VOUT = 1.3 V Figure 18. Output Voltage vs Input Voltage, VOUT = 1.3 V 1.305 100 Test Conditions: VO =1.3 V, VIN = 3 V L = 10 µH (Toko DFE252012C) 1.300 VOUT (V) 1.295 Maximum Output Current (mA) VOUT (V) 1.299 1.295 1.290 IO Series1 = 1 mA IO Series2 = 10 mA IO Series4 = 50 mA 1.285 -40 -20 0 20 40 60 60 40 TASeries1 = ±40C TASeries2 = 0C TASeries4 = 25C TASeries5 = 85C 20 0 2.0 2.5 3.0 3.5 4.0 4.5 5.0 VIN (V) C015 Figure 19. Output Voltage vs Temperature, VOUT = 1.3 V 5.5 C016 Figure 20. Maximum Output Current vs. Input Voltage VOUT = 2.5 V 100 100 90 Test Conditions: VO =1.8 V ± 100 mV L = 10 µH (Toko DFE252012C) 80 70 60 TSeries1 A = ±40C TSeries2 A = 0C TSeries4 A = 25C TSeries5 A = 85C 50 40 2.0 2.5 3.0 3.5 4.0 4.5 VIN (V) 5.0 5.5 C017 Figure 21. Maximum Output Current vs. Input Voltage, VOUT = 1.8 V Copyright © 2012–2013, Texas Instruments Incorporated Maximum Output Current (mA) Maximum Output Current (mA) 80 80 Temperature (C) Test Conditions: VO = 2.5 V ± 100 mV L = 10 µH (Toko DFE252012C) Test Conditions: VO = 1.3 V ± 100 mV L = 10 µH (Toko DFE252012C) 90 80 70 60 TASeries1 = ±40C TASeries2 = 0C TASeries4 = 25C TASeries5 = 85C 50 40 2.0 2.5 3.0 3.5 4.0 VIN (V) 4.5 5.0 5.5 C018 Figure 22. Maximum Output Current vs. Input Voltage, VOUT = 1.3 V 13 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 450 1200 350 300 Input Quiescent Current (nA) = 85°C 85C TT A= TT = 55°C 55C A= TT = 25°C 25C A= 0C TTA = 0°C TTA ±40°C -40 C A == 400 Input Quiescent Current (nA) www.ti.com.cn 250 200 150 100 TT=85C A = 85°C TT=55C A = 55°C 1000 TT=25C A = 25°C TT=0C A = 0°C TTA ±40°C -40 C A == 800 600 400 200 50 0 0 2.0 2.5 3.0 3.5 4.0 4.5 5.0 2.0 5.5 Input Quiescent Current (nA) Input Quiescent Current (nA) 800 600 400 200 4.5 5.0 5.5 C020 Rsum = 1 M Rsum=1M 700 Rsum=13M Rsum = 13 M 600 500 400 300 200 0 2.0 2.5 3.0 3.5 4.0 4.5 5.0 2.0 5.5 Figure 25. Input Quiescent Current vs. Input Voltage Active Mode 80 60 40 VIN = 2 V Vin Vin VIN = 3 V 20 Vin VIN = 4 V Vin VIN = 5 V 0 10 20 30 40 Output Current (mA) 50 60 C022 Figure 27. Major Switching Frequency vs Output Current 3.5 4.0 4.5 5.0 5.5 C026 Figure 26. Input Quiescent Current vs. Input Voltage Active Mode where RSUM = R1+R2+R3 Major Switching Frequency (kHz) VO = 1.3 V L = 10 PH 0 3.0 Input Voltage (V) 120 100 2.5 C021 Input Voltage (V) Major Switching Frequency (kHz) 4.0 100 0 14 3.5 Figure 24. Input Quiescent Current vs. Input Voltage Standby Mode 800 TAT=85C = 85°C TAT=55C = 55°C TAT=25C = 25°C TAT=0C = 0°C TAT==±40°C -40 C 1000 3.0 Input Voltage (V) Figure 23. Input Quiescent Current vs. Input Voltage Ship Mode 1200 2.5 C019 Input Voltage (V) 130 120 110 100 90 80 70 60 50 40 30 20 10 0 IOUT = 100 A Iout=100uA VO = 1.3 V L = 10P+ IOUT = 1 mA I=1mA IOUT = 10 mA I=10mA IOUT = 50 mA I=50mA 2.0 2.5 3.0 3.5 4.0 Input Voltage (V) 4.5 5.0 5.5 C023 Figure 28. Major Switching Frequency vs Input Voltage Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 30 Output Voltage Ripple (mVPP) Output Voltage Ripple (mVPP) 25 20 15 10 VIN = 2 V Vin Vin VIN = 3 V 5 Vin VIN = 4 V VO = 1.3 V C = 22 PF 0 10 20 30 40 Output Current (mA) 50 IOUT = 1 mA I=1mA 25 IOUT = 10 mA I=10mA IOUT = 50 mA I=50mA 20 15 10 Vin VIN = 5 V 0 IOUT = 100 A Iout=100uA 5 VO = 1.3 V C = 22 PF 0 2.0 60 2.5 3.0 3.5 4.0 4.5 5.0 5.5 Input Voltage (V) C025 Figure 29. Output Voltage Ripple vs Output Current C024 Figure 30. Output Voltage Ripple vs Input Voltage 2 V/div 10 mV/div 100 mA/div 2 V/div 10 mV/div 50 mA/div IL VOUT-AC SW 10 Ps/div 1 V/div IL 1 V/div VOUT-AC SW 4 Ps/div Figure 33. Steady State Operation with RO = 50 Ω and L = 4.7 µH Copyright © 2012–2013, Texas Instruments Incorporated VOUT-AC SW 2 Ps/div Figure 32. Steady State Operation with RO = 100 kΩ, L = 10 µH 1 V/div 2 V/div 10 mV/div 100 mA/div Figure 31. Steady State Operation with RO = 50 Ω, L = 10 µH IL VIN VOUT VRDIV 2 ms/div Figure 34. Sampling Waveform 15 TPS62736 TPS62737 40 ms/div 2 V/div 2 V/div 2 V/div 5 V/div IOUT VOUT 2 V/div SW VOUT-AC SW EN1 VIN_OK VOUT SW 20 ms/div 4 Ps/div Figure 37. IR Pulse Transient Response 2 V/div 2 V/div 2 V/div 5 V/div IOUT 10 Ps/div Figure 36. Load Transient Response Figure 35. Line Transient Response 2 V/div 100 mA/div 50 mA/div 20 mV/div VOUT-AC IL 5 V/div 50 mA/div www.ti.com.cn VIN 10 mV/div 2 V/div ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 Figure 38. Ship-Mode Startup Behavior EN2 VIN_OK VOUT SW 400 Ps/div Figure 39. Standby-Mode Startup Behavior 16 Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 Table of Graphs for TPS62737 Unless otherwise noted, graphs were taken using Figure 2 with L = Toko 10 µH DFE252012C VO = 2.5 V Efficiency η VO = 1.8 V Efficiency VO = 1.3 V Efficiency VO = 2.5 V VOUT (DC) VO = 1.8 V VO = 1.3 V vs. Output Current Figure 40 vs. Input Voltage Figure 41 vs. Output Current Figure 42 vs. Input Voltage Figure 43 vs. Output Current Figure 44 vs. Input Voltage Figure 45 vs. Output Current Figure 46 vs. Input Voltage Figure 46 vs. Temperature Figure 48 vs. Output Current Figure 49 vs. Input Voltage Figure 50 vs. Temperature Figure 51 vs. Output Current Figure 52 vs. Input Voltage Figure 53 vs. Temperature Figure 54 VO = 2.5 V IOUT MAX (DC) VO = 1.8 V Figure 55 vs. Input Voltage VO = 1.3 V EN1 = 0, EN2 = 0 (Standby Mode) Figure 58 vs. Input Voltage EN1 = 0, EN2 = 1 (Active Mode) Figure 59 Figure 60 vs. Output Current Figure 61 vs. Input Voltage Figure 62 vs.Output Current Figure 64 vs. Input Voltage Figure 64 RO = 100 kΩ Figure 65 RO = 9 Ω Figure 66 VO = 2.5 V Figure 67 Load Transient, VIN = 3.6V, ROUT = none -> 9 Ω Figure 68 Line Transient, VIN = 3.6V -> 4.6V, ROUT = 9 Ω Figure 69 VO = 2.5 V IR Pulse Transient, VIN = 4.0V, 200mA transient every 1us Figure 70 VIN = 0 V to 5 V to 0 V, VO = 1.8 V EN1 = 0, EN2=1 Figure 71 EN1 = 1 to 0, EN2=1 - Ship mode startup Figure 72 EN1 = 0, EN2 0 to 1 - Standy mode startup Figure 73 Switching Frequency VO = 1.8 V Output Ripple VO = 1.8 V Steady State Operation VIN = 3.6 V, VO = 1.8 V Power Management Response VRDIV Behavior VO = 1.8 V Transient Response Startup Behavior Figure 56 Figure 57 EN1 = 1, EN2 = 0 (Ship Mode) Input IQ FIGURE VIN = 3.6 V, VO = 1.8 V Copyright © 2012–2013, Texas Instruments Incorporated 17 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn 100.0 100 90 95.0 Efficiency (%) Efficiency (%) 80 70 60 = 5.5 V VVIN IN = 3.0 V 50 40 0.001 85.0 80.0 VVIN 2.5VV IN ==5.5 0.01 0.1 1 10 100 75.0 2.5 1000 3 3.5 100 95 90 Efficiency (%) 70 VIN 2.5VV V IN ==2.5 60 VIN 3.0VV V IN ==3.0 VIN 3.6VV V IN ==3.6 50 V VIN 5.5VV IN ==5.5 0.1 1 10 100 0.01mA mA IIO O ==0.01 0.1mA mA IIO O ==0.1 mA IIO O ==11mA 10mA mA IIO O ==10 IIO 100mA mA O ==100 200mA mA IIO O ==200 85 80 2 3 4 6 C044 Figure 43. Efficiency vs Input Voltage, VOUT = 1.8 V 100 85 0.01 mA IIO mA O ==0.1 IIO mA O ==11mA 95 80 IIO 10mA mA O ==10 90 Efficiency (%) 75 Efficiency (%) 5 VIN (V) C047 90 70 65 60 VIN 2.5VV V IN ==2.5 55 VIN 3.0VV V IN ==3.0 50 VIN 3.6VV V IN ==3.6 45 VIN 4.2VV V IN ==4.2 0.01 0.1 1 10 100 IIO 100mA mA O ==100 IIO 200mA mA O ==200 85 80 75 70 V VIN 5.5VV IN ==5.5 IOUT (mA) 65 1000 C046 Figure 44. Efficiency Vs Output Current, VOUT = 1.3 V 18 C045 70 Figure 42. Efficiency Vs Output Current, VOUT = 1.8 V 40 0.001 5.5 90 1000 IOUT (mA) 5 75 VIN 4.2VV V IN ==4.2 0.01 4.5 Figure 41. Efficiency vs Input Voltage, VOUT = 2.5 V 100 80 4 VIN (V) C048 Figure 40. Efficiency Vs Output Current, VOUT = 2.5 V Efficiency (%) 90.0 2.3VV VVIN IN ==4.2 IOUT (mA) 40 0.001 = 0.1 mA IIO O = 0.1 mA mA IIO O ==11mA 10mA mA IIO O ==10 100mA mA IIO O ==100 IIO 200mA mA O ==200 2 3 4 VIN (V) 5 6 C043 Figure 45. Efficiency vs Input Voltage, VOUT = 1.3 V Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 2.53 2.54 2.52 2.52 2.5 2.48 VOUT (V) VOUT (V) 2.51 2.5 2.49 2.48 2.47 2.46 0.001 2.46 2.44 VIN = 3.0 V V IN = 3.0 V VIN =3.6 3.6VV V = IN 2.42 VIN 4.2VV V IN ==4.2 2.38 V VIN 5.5VV IN ==5.5 0.01 = 0.001 IIO O = 0.001 mA 0.1mA mA IIO O ==0.1 10mA mA IIO O ==10 IIO 170mA mA O ==170 2.4 2.36 0.1 1 10 100 1000 IOUT (mA) 2.5 3 3.5 4 = 0.01 mA IIO O = 0.01 mA mA IIO O ==11mA 100mA mA IIO O ==100 IIO 200mA mA O ==200 4.5 5 5.5 VIN (V) C061 Figure 46. Output Voltage vs Output Current. VOUT = 2.5 V C058 Figure 47. Output Voltage vs Input Voltage, VOUT = 2.5 V 1.8 2.52 IO = 1 mA 2.51 1.795 1.785 IO = 10 mA 2.49 VOUT (V) Output Voltage (V) 1.79 2.50 2.48 IO = 100 mA 2.47 1.78 1.775 1.77 VIN = 2.5 V V IN = 2.5 V 1.765 VIN 3.0VV V IN ==3.0 1.76 VIN 3.6VV V IN ==3.6 1.755 VIN 4.2VV V IN ==4.2 IO = 180 mA 2.46 1.75 0.001 2.45 ±20 ±5 10 25 40 55 70 Temperature (oC) 85 VIN 5.5VV V IN ==5.5 0.01 1 10 100 1000 IOUT (mA) Figure 48. Output Voltage vs Temperature, VOUT = 2.5 V C060 Figure 49. Output Voltage vs Output Current, VOUT = 1.8 V 1.81 1.84 1.8 1.83 IO = 1 mA Output Voltage (V) 1.79 1.78 VOUT (V) 0.1 C020 1.77 1.76 1.75 1.74 = 0.001 IIO O = 0.001 mA 0.1mA mA IIO O ==0.1 10mA mA IIO O ==10 IIO 170mA mA O ==170 1.73 1.72 1.71 2 3 4 VIN (V) = 0.01 mA IIO O = 0.01 mA mA IIO O ==11mA 100mA mA IIO O ==100 IIO 200mA mA O ==200 1.81 1.80 IO = 10 mA 1.79 IO = 100 mA 1.78 IO = 180 mA 1.77 5 ±20 C057 Figure 50. Output Voltage vs Input Voltage, VOUT = 1.8 V Copyright © 2012–2013, Texas Instruments Incorporated 1.82 ±5 10 25 40 Temperature (oC) 55 70 85 C020 Figure 51. Output Voltage vs Temperature, VOUT = 1.8 V 19 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn 1.335 1.33 1.325 1.33 1.32 1.315 1.31 1.32 VOUT (V) VOUT (V) 1.325 1.315 VIN = 2.5 V V IN = 2.5 V 1.31 1.28 VIN 4.2VV V IN ==4.2 1.295 0.001 1.275 VIN 5.5VV V IN ==5.5 0.01 1.27 0.1 1 10 100 1000 IOUT (mA) 3 4 5 VIN (V) C059 C056 Figure 53. Output Voltage vs Input Voltage, VOUT = 1.3 V 1.325 300 Maximum Output Current (mA) IO = 1 mA 1.315 Output Voltage (V) 2 = 0.01 mA IIO O = 0.01 mA mA IIO O ==11mA IIO 100mA mA O ==100 IIO 200mA mA O ==200 Figure 52. Output Voltage vs Output Current, VOUT = 1.3 V 1.320 1.310 IO = 10 mA 1.305 1.300 1.295 1.290 IO = 100 mA 1.285 1.280 ±20 ±5 10 25 40 55 260 240 220 200 180 TA =T=85C 85°C TA =TA 55°C = 55 TA =TA=25 25°C TA = 0°C TA=0 TA TA=-20 = ±20°C 160 140 100 70 85 Temperature (oC) 2.0 2.5 3.0 C020 3.5 4.0 4.5 5.0 5.5 C020 Input Voltage (V) Figure 54. Output Voltage vs Temperature, VOUT = 1.3 V Figure 55. Maximum Output Current vs. Input Voltage VOUT = 2.5 V 330 Maximum Output Current (mA) 330 Maximum Output Current (mA) 280 120 IO = 180 mA 1.275 280 230 180 TA =T=85C 85°C TA =TA 55°C = 55 TA = 25°C TA=25 TA = 0°C TA=0 TA TA=-20 = ±20°C 130 80 2.0 2.5 3.0 3.5 4.0 Input Voltage (V) 4.5 5.0 280 230 180 TA =TA=85 85°C TA =TA 55°C = 55 TA = 25°C TA=25 TA = 0°C TA=0 TA TA=-20 = ±20°C 130 80 5.5 C020 Figure 56. Maximum Output Current vs. Input Voltage, VOUT = 1.8 V 20 = 0.001 IIO O = 0.001 mA 0.1mA mA IIO O ==0.1 IIO 10mA mA O ==10 IIO 170mA mA O ==170 1.285 VIN 3.6VV V IN ==3.6 1.3 1.3 1.295 1.29 VIN 3.0VV V IN ==3.0 1.305 1.305 2.0 2.5 3.0 3.5 4.0 Input Voltage (V) 4.5 5.0 5.5 C020 Figure 57. Maximum Output Current vs. Input Voltage, VOUT = 1.3 V Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn 500 1,200 400 350 Input Quiescent Current (nA) o C = 85 TTA A = 85 C oC TTA 2525 C A == oC TTA = 0 A = 0 C o TTA A = =-40 -40CC 450 Input Quiescent Current (nA) ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 300 250 200 150 100 1,000 800 TA = 85oC 600 TA = 0oC TA = 25oC 400 200 50 0 2 2.5 3 3.5 4 4.5 5 Input Voltage (V) 5.5 2 3 3.5 4 Input Voltage (V) 4.5 5 5.5 C055 Figure 59. Input Quiescent Current vs. Input Voltage Standby Mode 1,000 100 TA = 85oC 800 600 TA = 0oC TA = 25oC 90 Major Switching Frequency (kHz) Input Quiescent Current (nA) 2.5 C054 Figure 58. Input Quiescent Current vs. Input Voltage Ship Mode 400 200 TA = -40oC 80 70 60 50 40 20 VIN = 2.5 V V IN = 2.45 V VIN 3.0VV V IN ==3.0 10 VIN 3.6VV V IN ==4.2 30 VIN 4.2VV V IN ==5.5 0 0 2 2.5 3 3.5 4 4.5 5 Input Voltage (V) 0 5.5 20 40 60 80 100 120 140 160 180 200 Output Current (mA) C053 Figure 60. Input Quiescent Current vs. Input Voltage Active Mode C049 Figure 61. Major Switching Frequency vs Output Current 70 120 110 IO = 100 mA 100 Output Voltage Ripple (mV) Major Switching Frequency (kHz) TA = -40oC 0 90 80 IO = 5 mA 70 60 50 IO = 10 mA 40 30 IO = 50 mA IO = 500 PA 20 60 50 40 30 VIN = 2.5 V V IN = 2.45 V 20 VIN 3.0VV V IN ==3.0 10 VIN 3.6VV V IN ==4.2 10 VIN 4.2VV V IN ==5.5 0 0 2.1 2.6 3.1 3.6 4.1 Input Voltage (V) 4.6 0 5.1 C051 Figure 62. Major Switching Frequency vs Input Voltage Copyright © 2012–2013, Texas Instruments Incorporated 20 40 60 80 100 120 140 160 180 200 Output Current (mA) C050 Figure 63. Output Voltage Ripple vs Output Current 21 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn 200 mA 50 mV 60 IO = 100 mA IO = 5 mA IO = 10 mA SW 2V 50 40 IO = 50 mA 20 IO = 500 PA 0 2.1 2.6 3.1 3.6 4.1 4.6 IL VOUT VIN 47.5 mV 30 10 SW 5.1 Input Voltage (V) 1 ms/div C052 Figure 64. Output Voltage Ripple vs Input Voltage Figure 65. Steady State Operation with RO = 100 kΩ IL 200 mAV/div VOUT 2 V/div VIN 2 V/div 50 mV/div IL VOUT VIN 1.9 V 47.5 mV 190 mA Output Voltage Ripple (mV) 70 50 mV 80 VRDIV VIN-OK SW 2 V/div 2 V/div 2 V/div VOUT 10 μs/div 100 ms/div Figure 66. Steady State Operation with RO = 9 Ω VOUT 200 mA/div IL VOUT 50 mV/div IOUT 1 V/div 200 mA/div 200 mA/div IL 50 mV/div Figure 67. Power Management Response VSW 2 V/div 2 V/div VSW 20 μs/div Figure 68. Load Transient Response 22 50 μs/div Figure 69. Line Transient Response Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 VOUT VOUT VIN VIN-OK 2 V/div 1 V/div SW 5 μs/div 10 s/div 2 V/div Figure 71. Startup Behavior with Slow Ramping VIN, EN1=0, EN2=1 EN2 2 V/div VIN-OK 1 V/div VIN-OK VOUT VOUT VSW 2 V/div 2 V/div 1 V/div 2 V/div 2 V/div Figure 70. IR Pulse Transient Response EN1 1 V/div 1 V/div 1 V/div 100 mA/div IOUT VSW 20 ms/div Figure 72. Ship-Mode Startup Behavior Copyright © 2012–2013, Texas Instruments Incorporated 200 μs/div Figure 73. Standby-Mode Startup Behavior 23 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn DETAILED PRINCIPLE OF OPERATION Step Down (Buck) Converter Operation The buck regulator in the TPS6273X takes input power from VIN, steps it down and provides a regulated voltage at the OUT pin. It employs pulse frequency modulation (PFM) control to regulate the voltage close to the desired reference voltage. The reference voltage is set by the user programmed resistor divider. The current through the inductor is controlled through internal current sense circuitry. The peak current in the inductor is controlled to maintain high efficiency of the converter across a wide input current range. The TPS62736 converter delivers an average output current of 50mA with a peak inductor current of 100 mA. The TPS62737 converter delivers an average output current of 200 mA with a peak inductor current of 370 mA.The buck regulator is disabled when the voltage on VIN reaches the UVLO condition. The UVLO level is continuously monitored. The buck regulator continues to operate in pass (100% duty cycle) mode, passing the input voltage to the output, as long as VIN is greater than UVLO and less than VIN minus IOUT times RDS(on) of the high-side FET (i.e., VIN - IOUT x RDS(on)-HS). In order to save power from being dissipated through other IC’s on this supply rail while allowing for a faster wake up time, the buck regulator can be enabled and disabled via the EN2 pin for systems that desire to completely turn off the regulated output. Nano-Power Management and Efficiency The high efficiency of the TPS6273X is achieved via the proprietary Nano-Power management circuitry and algorithm. This feature essentially samples and holds all references in order to reduce the average quiescent current. That is, the internal circuitry is only active for a short period of time and then off for the remaining period of time at the lowest feasible duty cycle. A portion of this feature can be observed in Figure 34 where the VRDIV node is monitored. Here the VRDIV node provides a connection to the input (larger voltage level) and generates the output reference (lower voltage level) for a short period of time. The divided down value of input voltage is compared to VBIAS and the output voltage reference is sampled and held to get the VOUT_SET point. Since this biases a resistor string, the current through these resistors is only active when the Nano-Power management circuitry makes the connection—hence reducing the overall quiescent current due to the resistors. This process repeats every 64 ms. Similarly,the VIN_OK level is monitored every 64ms, as shown in Figure 67. The efficiency versus output current and versus input voltage are plotted for three different output voltages for both the TPS62736 and TPS62737 in the Typical Characteristics section. All data points were captured by averaging the overall input current. This must be done due to the periodic biasing scheme implemented via the Nano-Power management circuitry. The input current efficiency data was gathered using a source meter set to average over at least 25 samples and at the highest accuracy sampling rate. Each data point takes a long period of time to gather in order to properly measure the resulting input current when calculating the efficiency. Programming OUT Regulation Voltage and VIN_OK To set the proper output regulation voltage and input voltage power good comparator, the external resistors must be carefully selected. Figure 1 illustrates an application diagram which uses the minimal resistor count for setting both VOUT and VIN_OK. Note that VBIAS is nominally 1.21V per the electrical specification table. Referring to Figure 1, the OUT dc set point is given by: æ R + R 2 + R3 ö VOUT = VBIAS ç 1 ÷ è R1 + R2 ø (1) The VIN_OK setting is given by: æ R + R 2 + R3 ö VIN _ OK = VBIAS ç 1 ÷ R1 è ø (2) The sum of the resistors is recommended to be no greater than 13 MΩ , that is, RSUM = R1 + R2 + R3 = 13 MΩ. Due to the sampling operation of the output resistors, lowering RSUM only increases quiescent current slightly as can be seen in Figure 26. Higher resistors may result in poor output voltage regulation and/or input voltage power good threshold accuracies due to noise pickup via the high impedance pins or reduction of effective resistance due to parasitic resistances created from board assembly residue. See Layout Considerations section for more details. If it is preferred to separate the VOUT and VIN_OK resistor strings, two separate strings of resistors could be used as shown in Figure 3. The OUT dc set point is then given by Equation 3: 24 Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 æ R + R4 ö VOUT = VBIAS ç 3 ÷ è R4 ø (3) The VIN_OK setting is then given by Equation 4: æ R + R2 ö VIN _ OK = VBIAS ç 1 ÷ è R1 ø (4) If it is preferred to disable the VIN_OK setting, the VIN_OK_SET pin can be tied to VIN as shown in Figure 4. To set VOUT in this configuration, use Equation 3. To tighten the dc set point accuracy, use external resistors with better than 1% resistor tolerance. Since output voltage ripple has a large effect on input line regulation and the output load regulation, using a larger output capacitor will improve both line and load regulation. Enable Controls There are two enable pins implemented in the TPS6273X in order to maximize the flexibility of control for the system. The EN1 pin is considered to be the chip enable. If EN1 is set to a 1 then the entire chip is placed into ship mode. If EN1 is 0 then the chip is enabled. EN2 enables and disables the switching of the buck converter. When EN2 is low, the internal circuitry remains ON and the VIN_OK indicator still functions. This can be used to disable down-stream electronics in case of a low input supply condition. When EN2 is 1, the buck converter operates normally. Table 1. Enable Functionality Table EN1 PIN EN2 PIN 0 0 Partial standby mode. Buck switching converter is off, but VIN_OK indication is on FUNCTIONAL STATE 0 1 Buck mode and VIN_OK enabled 1 x Full standby mode. Switching converter and VIN_OK indication is off (ship mode) Startup Behavior The TPS6273X has two startup responses: 1) from the ship-mode state (EN1 transitions from high to low), and 2) from the standby state (EN2 transitions from low to high). The first startup response out of the ship-mode state has the longest time duration due to the internal circuitry being disabled. This response is shown in Figure 38 for the TPS62736 and Figure 72 for the TPS62737. The startup time takes approximately 100ms due to the internal Nano-Power management circuitry needing to complete the 64 ms sample and hold cycle. Startup from the standby state is shown in Figure 39 for the TPS62736 and Figure 73 for the TPS62737. This response is much faster due to the internal circuitry being pre-enabled. The startup time from this state is entirely dependent on the size of the output capacitor. The larger the capacitor, the longer it will take to charge during startup. The TPS6273X can startup into a pre-biased output voltage. Steady State Operation and Cycle by Cycle Behavior The steady state operation at full load is shown in Figure 31 for the TPS62736 and Figure 66 for TPS62737. This plot highlights the inductor current waveform, the output voltage ripple, and the switching node. The output voltage is maintained by charging and discharging the output capacitor at a primary duty cycle (major frequency) which in turn dictates the output voltage ripple frequency. When VOUT is increasing in value, the output capacitor is charged by the hysteretic buck controller. This is achieved by controlling the peak cycle-by-cycle inductor current to ILIM. The cycle-by-cycle current is maintained by turning on and off the high side FET at a secondary duty cycle (minor frequency). When VOUT reaches a peak value, all hysteretic control is disabled until a minimum value is reached. The rate at which the converter stays off is dictated by the load and the size of the output capacitor. At heavier output loads (larger output current), the time the converter is off is smaller when compared to light load conditions. The light load condition is shown in Figure 32 for the TPS62736 and Figure 65 for the TPS62737. Note that the converter is inactive for a longer period of time when compared to the active time. Copyright © 2012–2013, Texas Instruments Incorporated 25 TPS62736 TPS62737 ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 www.ti.com.cn The minor switching frequency is of concern when choosing the inductor. This maximum switching frequency is 1 MHz. The major switching frequency dictates the voltage ripple frequency. Figure 27 and Figure 28 show the major switching frequency versus load current and input voltage for the TPS62736, respectively. Figure 61 and Figure 62 show the major switching frequency versus load current and input voltage for the TPS62737, respectively. Inductor Selection The internal control circuitry is designed to control the switching behavior with a nominal inductance of 10 µH ± 20%. The inductor's saturation current should be at least 25% higher than the maximum cycle-by-cycle current limit per the electrical specs table (ILIM) in order to account for load transients. Since this device is a hysteretic controller, it is a naturally stable system (single order transfer function). However, the smaller the inductor value is, the faster the switching currents are. The speed of the peak current detect circuit sets the TPS62736 inductor's lower bound to 4.7 µH. When using a 4.7 µH, the peak inductor current will increase when compared to that of a 10 µH inductor. The steady-state operation with a 4.7 µH inductor with a 50 mA load for the TPS62736 is shown in Figure 33. A list of inductors recommended for this device is shown in Table 2. Table 2. Inductance (µH) Dimensions (mm) Part Number Manufacturer 10 2.0 x 2.5 x 1.2 DFE252012C-H-100M Toko 10 4.0x4.0x1.7 LPS4018-103M Coilcraft 4.7 (TPS62736 only) 2.0 x 2.5 x 1.2 DFE252012R-H-4R7M Toko Output Capacitor Selection The output capacitor is chosen based on transient response behavior and ripple magnitude. The lower the capacitor value, the larger the ripple will become and the larger the droop will be in the case of a transient response. It is recommended to use at least a 22 µF output capacitor for most applications. Input Capacitor Selection The bulk input capacitance is recommended to be a minimum of 4.7 µF ± 20% for the TPS62736 and 22 µF ± 20% for the TPS62737. This bulk capacitance is used to suppress the lower frequency transients produced by the switching converter. There is no upper bound to the input bulk capacitance. In addition, a high frequency bypass capacitor of 0.1 µF is recommended in parallel with the bulk capacitor. The high frequency bypass is used to suppress the high frequency transients produced by the switching converter. Layout and PCB Assembly Considerations To minimize switching noise generation, the step-down converter (buck) power stage external components must be carefully placed. The most critical external component for a buck power stage is its input capacitor. The bulk input capacitor (CIN1) and high frequency decoupling capacitor (CIN2) must be placed as close as possible between the power stage input (IN pin 1) and ground (VSS pin 12). Next, the inductor (L1) must be placed as close as possible beween the switching node (SW pin 13) and the output voltage (OUT pin 11). Finally, the output capacitor (COUT) should be placed as close as possible between the output voltage (OUT pin 11) and GND (VSS pin 12). In the diagram below, the input and output capacitor grounds are connected to VSS pin 12 through vias to the PCB's bottom layer ground plane. To minimize noise pickup by the high impedance voltage setting nodes (VIN_OK_SET pin 8 and VOUT_SET pin 9), the external resistors (R1, R2 and R3) should be placed so that the traces connecting the midpoints of the string are as short as possible. In the diagram below, the connection to VOUT_SET is by a bottom layer trace. The remaining pins are either NC pins, that should be connected to the PowerPAD™ as shown below, or digital signals with minimal layout restrictions. 26 Copyright © 2012–2013, Texas Instruments Incorporated TPS62736 TPS62737 www.ti.com.cn ZHCSAG7B – OCTOBER 2012 – REVISED JULY 2013 In order to maximize efficiency at light load, the use of voltage level setting resistors > 1MΩ is recommended. However, during board assembly, contaminants such as solder flux and even some board cleaning agents can leave residue that may form parasitic resistors across the physical resistors and/or from one end of a resistor to ground, especially in humid, fast airflow environments. This can result in the voltage regulation and threshold levels changing significantly from those expected per the installed resistor values. Therefore, it is highly recommended that no ground planes be poured near the voltage setting resistors. In addition, the boards must be carefully cleaned, possibly rotated at least once during cleaning, and then rinsed with de-ionized water until the ionic contamination of that water is well above 50 MOhm. If this is not feasible, then it is recommended that the sum of the voltage setting resistors be reduced to at least 5X below the measured ionic contamination. VIAS to GND PLANE CIN1 VIAS to GND PLANE CIN1 VIAS to GND PLANE CIN2 CIN2 VIN VIN 1 1 COUT L1 VOUT R3 R2 R1 VIA to GND PLANE Figure 74. Recommended Layout, TPS62736 COUT L1 VOUT R3 R2 R1 VIA to GND PLANE Figure 75. Recommended Layout, TPS62737 REVISION HISTORY Changes from Original (October 2012) to Revision A • Page 将器件从:预览改为了:激活 ............................................................................................................................................... 1 Changes from Revision A (March 2013) to Revision B Page • Added the TPS62737 Pinout information ............................................................................................................................. 6 • Added the TPS62737 Application Circuit, Figure 2 .............................................................................................................. 9 • Added graphs for TPS62737 to the Typical Characteristics ............................................................................................... 17 • Changed Figure 74 ............................................................................................................................................................. 27 • Added Figure 75 ................................................................................................................................................................. 27 Copyright © 2012–2013, Texas Instruments Incorporated 27 PACKAGE OPTION ADDENDUM www.ti.com 30-Jul-2013 PACKAGING INFORMATION Orderable Device Status (1) Package Type Package Pins Package Drawing Qty Eco Plan Lead/Ball Finish (2) MSL Peak Temp Op Temp (°C) Device Marking (3) (4/5) TPS62736RGYR ACTIVE VQFN RGY 14 3000 Green (RoHS & no Sb/Br) CU NIPDAU Level-2-260C-1 YEAR -40 to 85 62736 TPS62736RGYT ACTIVE VQFN RGY 14 250 Green (RoHS & no Sb/Br) CU NIPDAU Level-2-260C-1 YEAR -40 to 85 62736 TPS62737RGYR ACTIVE VQFN RGY 14 3000 Green (RoHS & no Sb/Br) CU NIPDAU Level-2-260C-1 YEAR -20 to 85 62737 TPS62737RGYT ACTIVE VQFN RGY 14 250 Green (RoHS & no Sb/Br) CU NIPDAU Level-2-260C-1 YEAR -20 to 85 62737 (1) The marketing status values are defined as follows: ACTIVE: Product device recommended for new designs. LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect. NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design. PREVIEW: Device has been announced but is not in production. Samples may or may not be available. OBSOLETE: TI has discontinued the production of the device. (2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details. TBD: The Pb-Free/Green conversion plan has not been defined. Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above. Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material) (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature. (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device. (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device. Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and Addendum-Page 1 Samples PACKAGE OPTION ADDENDUM www.ti.com 30-Jul-2013 continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release. In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis. Addendum-Page 2 PACKAGE MATERIALS INFORMATION www.ti.com 30-Jul-2013 TAPE AND REEL INFORMATION *All dimensions are nominal Device Package Package Pins Type Drawing TPS62736RGYR VQFN RGY 14 SPQ Reel Reel A0 Diameter Width (mm) (mm) W1 (mm) B0 (mm) K0 (mm) P1 (mm) W Pin1 (mm) Quadrant 3000 330.0 12.4 3.75 3.75 1.15 8.0 12.0 Q1 TPS62736RGYT VQFN RGY 14 250 180.0 12.4 3.75 3.75 1.15 8.0 12.0 Q1 TPS62737RGYR VQFN RGY 14 3000 330.0 12.4 3.75 3.75 1.15 8.0 12.0 Q1 TPS62737RGYT VQFN RGY 14 250 180.0 12.4 3.75 3.75 1.15 8.0 12.0 Q1 Pack Materials-Page 1 PACKAGE MATERIALS INFORMATION www.ti.com 30-Jul-2013 *All dimensions are nominal Device Package Type Package Drawing Pins SPQ Length (mm) Width (mm) Height (mm) TPS62736RGYR VQFN RGY 14 3000 367.0 367.0 35.0 TPS62736RGYT VQFN RGY 14 250 210.0 185.0 35.0 TPS62737RGYR VQFN RGY 14 3000 367.0 367.0 35.0 TPS62737RGYT VQFN RGY 14 250 210.0 185.0 35.0 Pack Materials-Page 2 重要声明 德州仪器(TI) 及其下属子公司有权根据 JESD46 最新标准, 对所提供的产品和服务进行更正、修改、增强、改进或其它更改, 并有权根据 JESD48 最新标准中止提供任何产品和服务。客户在下订单前应获取最新的相关信息, 并验证这些信息是否完整且是最新的。所有产品的销售 都遵循在订单确认时所提供的TI 销售条款与条件。 TI 保证其所销售的组件的性能符合产品销售时 TI 半导体产品销售条件与条款的适用规范。仅在 TI 保证的范围内,且 TI 认为 有必要时才会使 用测试或其它质量控制技术。除非适用法律做出了硬性规定,否则没有必要对每种组件的所有参数进行测试。 TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应 用相关的风险, 客户应提供充分的设计与操作安全措施。 TI 不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 组件或服务的组合设备、机器或流程相关的 TI 知识产权中授予 的直接或隐含权 限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息,不能构成从 TI 获得使用这些产品或服 务的许可、授权、或认可。使用 此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它 知识产权方面的许可。 对于 TI 的产品手册或数据表中 TI 信息的重要部分,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况 下才允许进行 复制。TI 对此类篡改过的文件不承担任何责任或义务。复制第三方的信息可能需要服从额外的限制条件。 在转售 TI 组件或服务时,如果对该组件或服务参数的陈述与 TI 标明的参数相比存在差异或虚假成分,则会失去相关 TI 组件 或服务的所有明 示或暗示授权,且这是不正当的、欺诈性商业行为。TI 对任何此类虚假陈述均不承担任何责任或义务。 客户认可并同意,尽管任何应用相关信息或支持仍可能由 TI 提供,但他们将独力负责满足与其产品及在其应用中使用 TI 产品 相关的所有法 律、法规和安全相关要求。客户声明并同意,他们具备制定与实施安全措施所需的全部专业技术和知识,可预见 故障的危险后果、监测故障 及其后果、降低有可能造成人身伤害的故障的发生机率并采取适当的补救措施。客户将全额赔偿因 在此类安全关键应用中使用任何 TI 组件而 对 TI 及其代理造成的任何损失。 在某些场合中,为了推进安全相关应用有可能对 TI 组件进行特别的促销。TI 的目标是利用此类组件帮助客户设计和创立其特 有的可满足适用 的功能安全性标准和要求的终端产品解决方案。尽管如此,此类组件仍然服从这些条款。 TI 组件未获得用于 FDA Class III(或类似的生命攸关医疗设备)的授权许可,除非各方授权官员已经达成了专门管控此类使 用的特别协议。 只有那些 TI 特别注明属于军用等级或“增强型塑料”的 TI 组件才是设计或专门用于军事/航空应用或环境的。购买者认可并同 意,对并非指定面 向军事或航空航天用途的 TI 组件进行军事或航空航天方面的应用,其风险由客户单独承担,并且由客户独 力负责满足与此类使用相关的所有 法律和法规要求。 TI 已明确指定符合 ISO/TS16949 要求的产品,这些产品主要用于汽车。在任何情况下,因使用非指定产品而无法达到 ISO/TS16949 要 求,TI不承担任何责任。 产品 应用 数字音频 www.ti.com.cn/audio 通信与电信 www.ti.com.cn/telecom 放大器和线性器件 www.ti.com.cn/amplifiers 计算机及周边 www.ti.com.cn/computer 数据转换器 www.ti.com.cn/dataconverters 消费电子 www.ti.com/consumer-apps DLP® 产品 www.dlp.com 能源 www.ti.com/energy DSP - 数字信号处理器 www.ti.com.cn/dsp 工业应用 www.ti.com.cn/industrial 时钟和计时器 www.ti.com.cn/clockandtimers 医疗电子 www.ti.com.cn/medical 接口 www.ti.com.cn/interface 安防应用 www.ti.com.cn/security 逻辑 www.ti.com.cn/logic 汽车电子 www.ti.com.cn/automotive 电源管理 www.ti.com.cn/power 视频和影像 www.ti.com.cn/video 微控制器 (MCU) www.ti.com.cn/microcontrollers RFID 系统 www.ti.com.cn/rfidsys OMAP应用处理器 www.ti.com/omap 无线连通性 www.ti.com.cn/wirelessconnectivity 德州仪器在线技术支持社区 www.deyisupport.com IMPORTANT NOTICE 邮寄地址: 上海市浦东新区世纪大道1568 号,中建大厦32 楼邮政编码: 200122 Copyright © 2014, 德州仪器半导体技术(上海)有限公司