Switched-Capacitor Circuits Basic Building Blocks

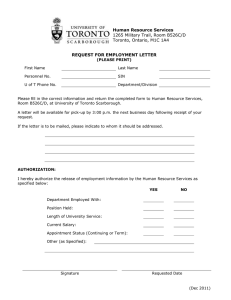

advertisement

Switched-Capacitor Circuits

David Johns and Ken Martin

University of Toronto

(johns@eecg.toronto.edu)

(martin@eecg.toronto.edu)

University of Toronto

1 of 60

© D. Johns, K. Martin, 1997

Basic Building Blocks

Opamps

• Ideal opamps usually assumed.

• Important non-idealities

— dc gain: sets the accuracy of charge transfer,

hence, transfer-function accuracy.

— unity-gain freq, phase margin & slew-rate: sets

the max clocking frequency. A general rule is that

unity-gain freq should be 5 times (or more) higher

than the clock-freq.

— dc offset: Can create dc offset at output. Circuit

techniques to combat this which also reduce 1/f

noise.

University of Toronto

2 of 60

© D. Johns, K. Martin, 1997

Basic Building Blocks

Double-Poly Capacitors

metal

C1

poly1

C p1

metal

thin oxide

C p2

poly2

C1

bottom plate

thick oxide

C p1

C p2

(substrate - ac ground)

equivalent circuit

cross-section view

• Substantial parasitics with large bottom plate

capacitance (20 percent of C 1 )

• Also, metal-metal capacitors are used but have even

larger parasitic capacitances.

University of Toronto

3 of 60

© D. Johns, K. Martin, 1997

Basic Building Blocks

Switches

I

Symbol

I

v1

v1

v1

v2

I

I

I

p-channel

v2

n-channel

transmission

gate

v2

v1

v2

I

• Mosfet switches are good switches.

— off-resistance near G: range

— on-resistance in 100: to 5k: range (depends on

transistor sizing)

• However, have non-linear parasitic capacitances.

University of Toronto

4 of 60

© D. Johns, K. Martin, 1997

Basic Building Blocks

Non-Overlapping Clocks

V on

V off

V on

V off

I1

T

n–2 n–1

I

n

n+1

teT

I2

n – 3 e 2n – 1 e 2 n + 1 e 2

I1

delay

1

f s { --T

delay

I2

teT

• Non-overlapping clocks — both clocks are never on

at same time

• Needed to ensure charge is not inadvertently lost.

• Integer values occur at end of I 1 .

• End of I 2 is 1/2 off integer value.

University of Toronto

5 of 60

© D. Johns, K. Martin, 1997

Switched-Capacitor Resistor Equivalent

I1

V1

I2

C1

V1

V2

'Q = C 1 V 1 – V 2 every clock period

Qx = Cx Vx

R eq

V2

T

R eq = -----C1

(1)

• C 1 charged to V 1 and then V 2 during each clk period.

'Q 1 = C 1 V 1 – V 2 (2)

• Find equivalent average current

C1 V1 – V2 I avg = -----------------------------T

(3)

where T is the clk period.

University of Toronto

6 of 60

© D. Johns, K. Martin, 1997

Switched-Capacitor Resistor Equivalent

• For equivalent resistor circuit

V1 – V2

I eq = -----------------R eq

(4)

• Equating two, we have

T

1

R eq = ------ = ---------C1

C1 fs

(5)

• This equivalence is useful when looking at low-freq

portion of a SC-circuit.

• For higher frequencies, discrete-time analysis is

used.

University of Toronto

7 of 60

© D. Johns, K. Martin, 1997

Resistor Equivalence Example

• What is the equivalent resistance of a 5pF

capacitance sampled at a clock frequency of 100kHz .

• Using (5), we have

1

R eq = --------------------------------------------------------- = 2M:

– 12

3

5 u 10 100 u 10 • Note that a very large equivalent resistance of 2M:

can be realized.

• Requires only 2 transistors, a clock and a relatively

small capacitance.

• In a typical CMOS process, such a large resistor

would normally require a huge amount of silicon

area.

University of Toronto

8 of 60

© D. Johns, K. Martin, 1997

Parasitic-Sensitive Integrator

v c2(nT)

I1

v ci(t)

v cx(t)

v c1(t)

I2

C2

v co(t)

I1

C1

v o(n) = v co(nT)

v i(n) = v ci(nT)

• Start by looking at an integrator which IS affected by

parasitic capacitances

• Want to find output voltage at end of I 1 in relation to

input sampled at end of I 1 .

University of Toronto

9 of 60

© D. Johns, K. Martin, 1997

Parasitic-Sensitive Integrator

C2

C2

v ci(nT – T)

v ci(nT – T e 2)

C1

v co(nT – T)

I 1 on

C1

v co(nT – T e 2)

I 2 on

• At end of I 2

C 2 v co(nT – T e 2) = C 2 v co(nT – T) – C 1 v ci(nT – T)

(6)

• But would like to know the output at end of I 1

C 2 v co(nT) = C 2 v co(nT – T e 2)

(7)

C 2 v co(nT) = C 2 v co(nT – T) – C 1 v ci(nT – T)

(8)

• leading to

University of Toronto

10 of 60

© D. Johns, K. Martin, 1997

Parasitic-Sensitive Integrator

• Modify above to write

C1

v o(n) = v o(n – 1) – ------v i(n – 1)

C

(9)

2

and taking z-transform and re-arranging, leads to

V o(z)

§ C 1· 1

H(z) { ------------ = – ¨ ------¸ ----------V i (z )

© C 2¹ z – 1

(10)

• Note that gain-coefficient is determined by a ratio of

two capacitance values.

• Ratios of capacitors can be set VERY accurately on

an integrated circuit (within 0.1 percent)

• Leads to very accurate transfer-functions.

University of Toronto

11 of 60

© D. Johns, K. Martin, 1997

Typical Waveforms

I1

t

I2

t

v ci(t)

t

v cx(t)

t

v co(t)

t

University of Toronto

12 of 60

© D. Johns, K. Martin, 1997

Low Frequency Behavior

• Equation (10) can be re-written as

§ C 1·

z –1 / 2

H(z) = – ¨ ------¸ ---------------------------© C 2¹ z 1 / 2 – z – 1 / 2

(11)

• To find freq response, recall

z = e jZT = cos ZT + j sin ZT ZT

ZT

z 1 / 2 = cos § -------· + j sin § -------·

© 2¹

© 2¹

ZT

ZT

z – 1 / 2 = cos § -------· – j sin § -------·

© 2¹

© 2¹

ZT

ZT

cos § -------· – j sin § -------·

© 2¹

© 2¹

§ C 1·

jZT

H(e ) = – ¨ ------¸ --------------------------------------------------ZT

© C 2¹

j2 sin § -------·

© 2¹

(12)

(13)

(14)

(15)

University of Toronto

13 of 60

© D. Johns, K. Martin, 1997

Low Frequency Behavior

• Above is exact but when ZT « 1 (i.e., at low freq)

H(e

jZT

§ C 1· 1

) # – ¨ ------¸ --------© C 2¹ jZT

(16)

• Thus, the transfer function is same as a continuoustime integrator having a gain constant of

C1 1

K I # ------ --C2 T

(17)

which is a function of the integrator capacitor ratio

and clock frequency only.

University of Toronto

14 of 60

© D. Johns, K. Martin, 1997

Parasitic Capacitance Effects

C p3

I1

C p4

C2

I2

I1

v i(n)

v o(n)

C1

C p1

C p2

• Accounting for parasitic capacitances, we have

§ C 1 + C p1· 1

H(z) = – ¨ ----------------------¸ ----------© C2 ¹ z – 1

(18)

• Thus, gain coefficient is not well controlled and

partially non-linear (due to C p1 being non-linear).

University of Toronto

15 of 60

© D. Johns, K. Martin, 1997

Parasitic-Insensitive Integrators

C2

I1

C1

I2

v ci(t)

v co(t)

I2

v i(n) = v ci(nT)

I1

I1

v o(n) = v co(nT)

• By using 2 extra switches, integrator can be made

insensitive to parasitic capacitances

— more accurate transfer-functions

— better linearity (since non-linear capacitances

unimportant)

University of Toronto

16 of 60

© D. Johns, K. Martin, 1997

Parasitic-Insensitive Integrators

C2

C2

v ci(nT – T e 2)

v ci(nT – T)

+

-

-

C1

v co(nT – T)

+

I 1 on

C1

v co(nT – T e 2)

I 2 on

• Same analysis as before except that C 1 is switched

in polarity before discharging into C 2 .

V o(z)

§ C 1· 1

H(z) { ------------ = ¨ ------¸ ----------V i(z)

© C 2¹ z – 1

(19)

• A positive integrator (rather than negative as before)

University of Toronto

17 of 60

© D. Johns, K. Martin, 1997

Parasitic-Insensitive Integrators

C p3

C p4

C2

I1

v i ( n)

C1

I2

I1

v o(n)

I2

I1

C p1

C p2

• C p3 has little effect since it is connected to virtual gnd

• C p4 has little effect since it is driven by output

• C p2 has little effect since it is either connected to

virtual gnd or physical gnd.

University of Toronto

18 of 60

© D. Johns, K. Martin, 1997

Parasitic-Insensitive Integrators

• C p1 is continuously being charged to v i(n) and

discharged to ground.

• I 1 on — the fact that C p1 is also charged to v i(n – 1)

does not affect C 1 charge.

• I 2 on — C p1 is discharged through the I 2 switch

attached to its node and does not affect the charge

accumulating on C 2 .

• While the parasitic capacitances may slow down

settling time behavior, they do not affect the discretetime difference equation

University of Toronto

19 of 60

© D. Johns, K. Martin, 1997

Parasitic-Insensitive Inverting Integrator

I1

C2

C1

I1

I1

v i ( n)

V i (z )

I2

I2

v o(n)

V o(z)

C 2 v co(nT – T e 2) = C 2 v co(nT – T)

C 2 v co(nT) = C 2 v co(nT – T e 2) – C 1 v ci(nT)

(20)

(21)

• Present output depends on present input(delay-free)

V o(z)

§ C 1· z

H(z) { ------------ = – ¨ ------¸ ----------V i (z )

© C 2¹ z – 1

(22)

• Delay-free integrator has negative gain while

delaying integrator has positive gain.

University of Toronto

20 of 60

© D. Johns, K. Martin, 1997

Signal-Flow-Graph Analysis

C1

V 1(z)

V 2(z)

I1

I2

I2

I1

V 3(z)

C2

I1

C3

V o( z )

I1

I2

V 1( z )

CA

I1

I2

– C1 1 – z –1 V 2( z )

V 3( z )

C2 z –1

1· 1

§ ------ ---------------© C A¹ 1 – z – 1

V o( z )

–C3

University of Toronto

21 of 60

© D. Johns, K. Martin, 1997

First-Order Filter

V in(s)

V out(s)

• Start with an active-RC structure and replace

resistors with SC equivalents.

• Analyze using discrete-time analysis.

University of Toronto

22 of 60

© D. Johns, K. Martin, 1997

First-Order Filter

I1

C2

I2

I1

I2

I1

I1

C3

I2

I2

CA

I1

C1

V i(z)

V o(z)

–C3

V i(z)

–C2

1· 1

§ ------ ---------------© C A¹ 1 – z –1

V o( z )

–C 1 1 – z –1 University of Toronto

23 of 60

© D. Johns, K. Martin, 1997

First-Order Filter

C A 1 – z – 1 V o(z) = – C 3 V o(z) – C 2 V i(z) – C 1 1 – z – 1 V i(z) (23)

§ C1·

§ C2·

¨ -------¸ 1 – z – 1 + ¨ -------¸

© C A¹

© C A¹

– -----------------------------------------------------V o( z )

C3

H(z) { ------------ =

1 – z – 1 + ------V i(z)

CA

(24)

C1

§ C 1 + C 2·

-----------------–

-----z

¨

¸

C

C

©

A ¹

A

= – ----------------------------------------C3·

§

¨ 1 + -------¸ z – 1

C A¹

©

University of Toronto

24 of 60

© D. Johns, K. Martin, 1997

First-Order Filter

• The pole of (24) is found by equating the

denominator to zero

CA

z p = -------------------CA + C3

(25)

• For positive capacitance values, this pole is

restricted to the real axis between 0 and 1

— circuit is always stable.

• The zero of (24) is found to be given by

C1

z z = ------------------C1 + C2

(26)

• Also restricted to real axis between 0 and 1.

University of Toronto

25 of 60

© D. Johns, K. Martin, 1997

First-Order Filter

The dc gain is found by setting z = 1 which results in

–C2

H(1) = --------C3

(27)

• Note that in a fully-differential implementation,

effective negative capacitances for C 1 , C 2 and C 3 can

be achieved by simply interchanging the input wires.

• In this way, a zero at z = – 1 could be realized by

setting

C 1 = – 0.5C 2

University of Toronto

(28)

26 of 60

© D. Johns, K. Martin, 1997

First-Order Example

• Find the capacitance values needed for a first-order

SC-circuit such that its 3dB point is at 10kHz when a

clock frequency of 100kHz is used.

• It is also desired that the filter have zero gain at

50kHz (i.e. z = – 1 ) and the dc gain be unity.

• Assume C A = 10pF .

Solution

• Making use of the bilinear transform

p = z – 1 e z + 1 the zero at – 1 is mapped to

: = f.

• The frequency warping maps the -3dB frequency of

10kHz (or 0.2S rad/sample ) to

University of Toronto

27 of 60

© D. Johns, K. Martin, 1997

First-Order Example

0.2S

: = tan § -----------· = 0.3249

© 2 ¹

(29)

• in the continuous-time domain leading to the

continuous-time pole, p p , required being

p p = – 0.3249

(30)

• This pole is mapped back to z p given by

1 + pp

z p = --------------- = 0.5095

1 – pp

(31)

• Therefore, H(z) is given by

kz + 1

H(z) = -----------------------z – 0.5095

University of Toronto

(32)

28 of 60

© D. Johns, K. Martin, 1997

First-Order Example

• where k is determined by setting the dc gain to one

(i.e. H(1) = 1 ) resulting

0.24525 z + 1 H(z) = -----------------------------------z – 0.5095

(33)

• or equivalently,

0.4814z + 0.4814

H(z) = -----------------------------------------1.9627z – 1

(34)

• Equating these coefficients with those of (24) (and

assuming C A = 10pF ) results in

(35)

(36)

(37)

C 1 = 4.814pF

C 2 = – 9.628 pF

C 3 = 9.628pF

University of Toronto

29 of 60

© D. Johns, K. Martin, 1997

Switch Sharing

C3

I2

C1

I1

)

I2

C2

I1

CA

I1

V o( z )

I2

• Share switches that are always connected to the

same potentials.

University of Toronto

30 of 60

© D. Johns, K. Martin, 1997

Fully-Differential Filters

• Most modern SC filters are fully-differential

• Difference between two voltages represents signal

(also balanced around a common-mode voltage).

• Common-mode noise is rejected.

• Even order distortion terms cancel

2

v1

nonlinear

element

–v1

nonlinear

element

3

4

v p1 = k 1 v 1 + k 2 v 1 + k 3 v 1 + k 4 v 1 + }

3

+

5

v diff = 2k 1 v 1 + 2k 3 v 1 + 2k 5 v 1 + }

2

3

4

v n1 = – k 1 v 1 + k 2 v 1 – k 3 v 1 + k 4 v 1 + }

University of Toronto

31 of 60

© D. Johns, K. Martin, 1997

Fully-Differential Filters

C1

C3

I2

+

V i(z)

-

I1

I1

CA I2

I2

C2

+

V (z )

- o

I1

I1

C2

I2

I1

CA I

I2

C3

2

I1

C1

University of Toronto

32 of 60

© D. Johns, K. Martin, 1997

Fully-Differential Filters

• Negative continuous-time input

— equivalent to a negative C 1

C1

I2

+

V i(z)

-

I1

I1

C3

CA I2

I2

C2

+

V (z )

- o

I1

I1

C2

I2

I1

CA I

I2

C3

2

I1

C1

University of Toronto

33 of 60

© D. Johns, K. Martin, 1997

Fully-Differential Filters

• Note that fully-differential version is essentially two

copies of single-ended version, however ... area

penalty not twice.

• Only one opamp needed (though common-mode

circuit also needed)

• Input and output signal swings have been doubled

so that same dynamic range can be achieved with

half capacitor sizes (from kT e C analysis)

• Switches can be reduced in size since small caps

used.

• However, there is more wiring in fully-differ version

but better noise and distortion performance.

University of Toronto

34 of 60

© D. Johns, K. Martin, 1997

Low-Q Biquad Filter

2

V out(s)

k2 s + k1 s + ko

H a(s) { ----------------- = – --------------------------------------V in(s)

Zo

2

2

s + § ------· s + Z o

© Q¹

1 e Zo

Q e Zo

C A = 1 V c1(s)

CB = 1

Zo e ko

–1 e Zo

V in(s)

(38)

1 e k1

V out(s)

k2

University of Toronto

35 of 60

© D. Johns, K. Martin, 1997

Low-Q Biquad Filter

I1 K C I1

4 1

I2

V 1(z)

I1 K C I2

5 2

I1 K C I1

1 1

I2

I1 K C I1

6 2

I2

C1

V i(z)

I2

I2

I2

I1

I2

C2

V o(z)

I1

I1 K C I1

2 2

I2

I2

K3 C2

University of Toronto

36 of 60

© D. Johns, K. Martin, 1997

Low-Q Biquad Filter

–K4

–K6

V 1(z)

V i(z)

–K1

1

--------------1 – z –1

K 5 z –1

1

--------------1 – z –1

V o(z)

–K2

–K3 1 – z –1 2

K 2 + K 3 z + K 1 K 5 – K 2 – 2K 3 z + K 3

V o( z )

H(z) { ------------ = – --------------------------------------------------------------------------------------------------2

V i(z)

1 + K z + K K – K – 2 z + 1

6

4 5

(39)

6

University of Toronto

37 of 60

© D. Johns, K. Martin, 1997

Low-Q Biquad Filter Design

2

a2 z + a1 z + a0

H(z) = – ------------------------------------2

b2 z + b1 z + 1

(40)

• we can equate the individual coefficients of “z” in

(39) and (40), resulting in:

(41)

(42)

(43)

(44)

(45)

K3 = a0

K2 = a2 – a0

K1 K5 = a0 + a1 + a2

K6 = b2 – 1

K4 K5 = b1 + b2 + 1

• A degree of freedom is available here in setting

internal V 1(z) output

University of Toronto

38 of 60

© D. Johns, K. Martin, 1997

Low-Q Biquad Filter Design

• Can do proper dynamic range scaling

• Or let the time-constants of 2 integrators be equal by

K4 = K5 =

(46)

b1 + b2 + 1

Low-Q Biquad Capacitance Ratio

• Comparing resistor circuit to SC circuit, we have

K4 | K5 | Zo T

(47)

Zo T

K 6 | ---------Q

(48)

• However, the sampling-rate, 1 e T , is typically much

larger that the approximated pole-frequency, Z o ,

(49)

Zo T « 1

University of Toronto

39 of 60

© D. Johns, K. Martin, 1997

Low-Q Biquad Capacitance Ratio

• Thus, the largest capacitors determining pole

positions are the integrating capacitors, C 1 and C 2 .

• If Q 1 , the smallest capacitors are K 4 C 1 and K 5 C 2

resulting in an approximate capacitance spread of

1 e Zo T .

• If Q ! 1 , then from (48) the smallest capacitor would

be K 6 C 2 resulting in an approximate capacitance

spread of Q e Z o T — can be quite large for Q » 1

University of Toronto

40 of 60

© D. Johns, K. Martin, 1997

High-Q Biquad Filter

• Use a high-Q biquad filter circuit when Q » 1

• Q-damping done with a cap around both integrators

• Active-RC prototype filter

1 e Zo

1eQ

C1 = 1

Zo e ko

V in(s)

–1 e Zo

C2 = 1

V out(s)

k1 e Zo

k2

University of Toronto

41 of 60

© D. Johns, K. Martin, 1997

High-Q Biquad Filter

I1 K C I1

4 1

I2

C1

V i(z)

I1 K C I1

1 1

I2

I2

K6 C1

V 1(z)

C2

I1 K C I2

5 2

I2

I2

I1

V o(z)

I1

K2 C1

K3 C2

• Q-damping now performed by K 6 C 1

University of Toronto

42 of 60

© D. Johns, K. Martin, 1997

High-Q Biquad Filter

• Input K 1 C 1 : major path for lowpass

• Input K 2 C 1 : major path for band-pass filters

• Input K 3 C 2 : major path for high-pass filters

• General transfer-function is:

2

V o( z )

K 3 z + K 1 K 5 + K 2 K 5 – 2K 3 z + K 3 – K 2 K 5 H(z) { ------------ = – -----------------------------------------------------------------------------------------------------------------(50)

2

V i(z)

z + K K + K K – 2 z + 1 – K K 4 5

5 6

5 6

• If matched to the following general form

2

a2 z + a1 z + a0

H(z) = – ------------------------------------2

z + b1 z + b0

(51)

University of Toronto

43 of 60

© D. Johns, K. Martin, 1997

High-Q Biquad Filter

K1 K5 = a0 + a1 + a2

K2 K5 = a2 – a0

(52)

K3 = a2

K4 K5 = 1 + b0 + b1

(54)

K5 K6 = 1 – b0

(56)

(53)

(55)

• And, as in lowpass case, can set

K4 = K5 =

(57)

1 + b0 + b1

• As before, K 4 and K 5 approx Z o T « 1 but K 6 # 1 e Q

University of Toronto

44 of 60

© D. Johns, K. Martin, 1997

Charge Injection

• To reduce charge injection (thereby improving

distortion) , turn off certain switches first.

I1

C3

Q5

C1

I1

V i(z)

C2

Q1

I2

Q 2Q 3

I 1a

Q6

I2

CA

Q4

I 2a

V o(z)

I1

• Advance I 1a and I 2a so that only their charge

injection affect circuit (result is a dc offset)

University of Toronto

45 of 60

© D. Johns, K. Martin, 1997

Charge Injection

• Note: I 2a connected to ground while I 1a connected

to virtual ground, therefore ...

— can use single n-channel transistors

— charge injection NOT signal dependent

Q CH = – W LC ox V eff = – W LC ox V GS – V t (58)

• Charge related to V GS and V t and V t related to

substrate-source voltage.

• Source of Q 3 and Q 4 remains at 0 volts — amount of

charge injected by Q 3 Q 4 is not signal dependent

and can be considered as a dc offset.

University of Toronto

46 of 60

© D. Johns, K. Martin, 1997

Charge Injection Example

• Estimate dc offset due to channel-charge injection

when C 1 = 0 and C 2 = C A = 10C 3 = 10pF .

• Assume switches Q 3 Q 4 have V tn = 0.8V , W = 30Pm ,

L = 0.8Pm , C ox = 1.9 u 10

supplies are r 2.5V .

–3

2

pF e Pm , and power

• Channel-charge of Q 3 Q 4 (when on) is

Q CH3 = Q CH4 = – 30 0.8 0.0019 2.5 – 0.8 = – 77.5 u 10

–3

(59)

pC

• dc feedback keeps virtual opamp input at zero volts.

University of Toronto

47 of 60

© D. Johns, K. Martin, 1997

Charge Injection Example

• Charge transfer into C 3 given by

(60)

Q C = – C 3 v out

3

• We estimate half channel-charges of Q 3 , Q 4 are

injected to the virtual ground leading to

1

--- Q CH3 + Q CH4 = Q C

3

2

(61)

which leads to

–3

77.5 u 10 pC

v out = ------------------------------------- = 78 mV

1pF

(62)

• dc offset affected by the capacitor sizes, switch sizes

and power supply voltage.

University of Toronto

48 of 60

© D. Johns, K. Martin, 1997

SC Gain Circuits — Parallel RC

R2

R2 e K

C1

KC 1

v in

v out(t) = – Kv in(t)

C2

I1

KC 2

I2

I1

I1

I2

I2

C1

KC 1

v in(n)

v out(n) = – Kv in(n)

University of Toronto

49 of 60

© D. Johns, K. Martin, 1997

SC Gain Circuits — Resettable Gain

C2

I2

I1

v in(n)

C1

I2

I2

I1

§ C 1·

v out(n) = – ¨ ------¸ v in(n)

© C 2¹

v out

V off

I2 I1 I2 I1 }

University of Toronto

time

50 of 60

© D. Johns, K. Martin, 1997

SC Gain Circuits

Parallel RC Gain Circuit

• circuit amplifies 1/f noise as well as opamp offset

voltage

Resettable Gain Circuit

• performs offset cancellation

• also highpass filters 1/f noise of opamp

• However, requires a high slew-rate from opamp

V off

+ C2

V off

- +

C1 +

V off

-

VC

v in(n) + 1C1 +

V off

-

V off

VC

- 2+

C2

v out(n)

§ C 1·

= – ¨ ------¸ v in(n)

© C 2¹

University of Toronto

51 of 60

© D. Johns, K. Martin, 1997

SC Gain Circuits — Capacitive-Reset

• Eliminate slew problem and still cancel offset by

coupling opamp’s output to invertering input

I1

C3

I2

I2

I 1 I 2 v in(n)

I2

I1 C2

C1

C4

I1

§ C 1·

v out(n) = – ¨ ------¸ v in(n)

© C 2¹

• C 4 is optional de-glitching capacitor

University of Toronto

52 of 60

© D. Johns, K. Martin, 1997

SC Gain Circuits — Capacitive-Reset

V off

+ C2

v out(n – 1)

- +

C3

V off

- +

C1

v out(n – 1) + V off

+

V off

-

during reset

C2

v in(n)

during valid output

C1

+

V off

-

C3

v out(n)

C1

= – § ------· v in(n)

© C 2¹

University of Toronto

53 of 60

© D. Johns, K. Martin, 1997

SC Gain Circuits — Differential Cap-Reset

I 1a

C3

I2

I 2a

C2

+

v in

-

v in

I1

I2

I2

I1

C1

C2

C1

I 2a

C3

I1

§ C 1· +

v out = ¨ ------¸ v in – v in © C 2¹

I1

I2

I 1a

• Accepts differential inputs and partially cancels

switch clock-feedthrough

University of Toronto

54 of 60

© D. Johns, K. Martin, 1997

Correlated Double-Sampling (CDS)

• Preceeding SC gain amp is an example of CDS

• Minimizes errors due to opamp offset and 1/f noise

• When CDS used, opamps should have low thermal

noise (often use n-channel input transistors)

• Often use CDS in only a few stages

— input stage for oversampling converter

— some stages in a filter (where low-freq gain high)

• Basic approach:

— Calibration phase: store input offset voltage

— Operation phase: error subtracted from signal

University of Toronto

55 of 60

© D. Johns, K. Martin, 1997

Better High-Freq CDS Amplifier

I1

C2

I

1

v in

I2

C1

I1

v out

I2

I2

I1

I2

Cc1

I1

I2

Cc2

I1

• I 2 — C 1' C 2' used but include errors

• I 1 — C 1 C 2 used but here no offset errors

University of Toronto

56 of 60

© D. Johns, K. Martin, 1997

CDS Integrator

C2

I2 I1 v in

C1

I1 I2 I2

I1

I1

v out

Cc2

I1

• I 1 — sample opamp offset on C 2'

• I 2 — C 2' placed in series with opamp to reduce error

• Offset errors reduced by opamp gain

• Can also apply this technique to gain amps

University of Toronto

57 of 60

© D. Johns, K. Martin, 1997

SC Amplitude Modulator

• Square wave modulate by r 1 (i.e. V out = r V in )

I1

C3

I2

I2

v in

IA

C1

C2

I1

IB

I A = I 2 I ca + I 1 I ca I B = I 1 I ca + I 2 I ca I1

I2

v out

IB

IA

I ca

• Makes use of cap-reset gain circuit.

• I ca is the modulating signal

University of Toronto

58 of 60

© D. Johns, K. Martin, 1997

SC Full-Wave Rectifier

Square Wave

Modulator

v in

v out

I ca

• Use square wave modulator and comparator to make

• For proper operation, comparator output should

changes synchronously with the sampling instances.

University of Toronto

59 of 60

© D. Johns, K. Martin, 1997

SC Peak Detector

V DD

I

v in

comp

opamp

v in

Q1

CH

v out

Q2

v out

CH

• Left circuit can be fast but less accurate

• Right circuit is more accurate due to feedback but

slower due to need for compensation (circuit might

also slew so opamp’s output should be clamped)

University of Toronto

60 of 60

© D. Johns, K. Martin, 1997